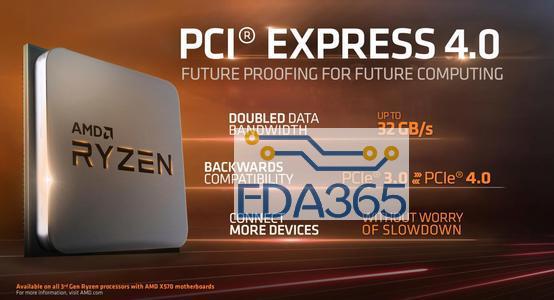

经历了PCIe1.0, PCIe2.0, PCIe3.0之后,当PCIe4.0出现在AMD平台上的时候,Intel多次提出“PCIe 4.0 无用”,而今,Intel终将支持PCIe4.0,在新的11代酷睿Rocket Lake上。

Intel在2001年提出了3GIO高速串行总线标准,用于计算机扩展。后来改名为:PCI-Express(peripheral component interconnect express,简称PCI-E,或PCIe),目的是要替代老的PCI,PCI-X和AGP总线标准。

可是在经历了PCIe1.0, PCIe2.0, PCIe3.0之后,当PCIe4.0出现在AMD平台上的时候,Intel多次提出“PCIe 4.0 无用”。

目前AMD锐龙、霄龙平台都已经全线支持PCIe 4.0,从处理器到芯片组再到显卡、计算卡无一例外。

目前AMD锐龙、霄龙平台都已经全线支持PCIe 4.0,从处理器到芯片组再到显卡、计算卡无一例外。

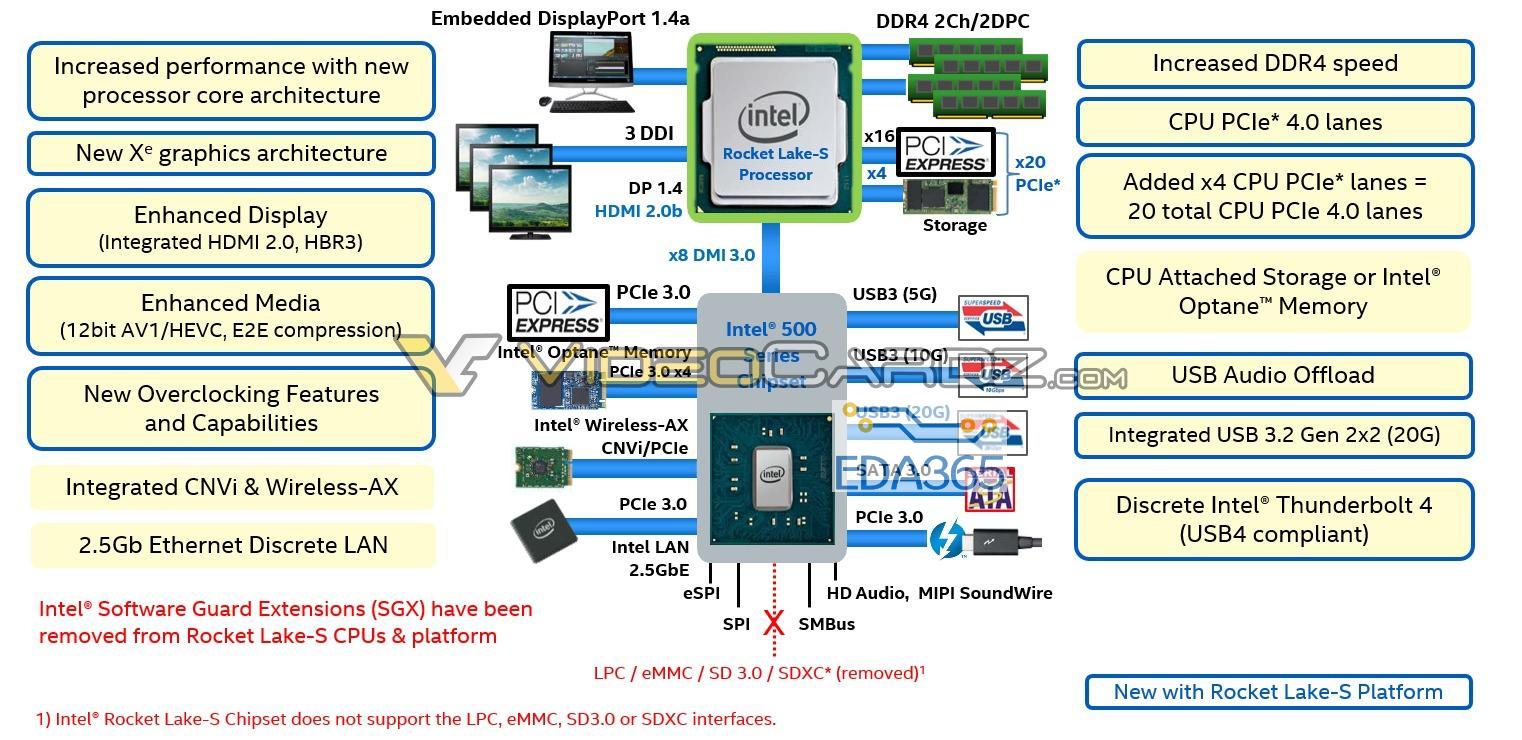

此前有传言:Intel将在2021年上半年发布的11代酷睿Rocket Lake会原生支持PCIe 4.0,现在终于得到确认。

尽管 Intel在一些专业产品上已经用上了PCIe 4.0,但是在消费级领域,Intel也并不会跨越支持PCIe 5.0,还是会老老实实地一步一步来。

SiSoftware软件内发现了一套新的Rocket Lake系统,其中硬盘赫然就是PCIe 4.0 SSD,容量1TB,支持PCIe 4.0 x4、NVMe。

Rocket Lake将会延续现有Comet Lake 10代酷睿更换的新接口LGA1200,理论上完全兼容400系列主板,但是要想开启PCIe 4.0,最佳搭档还是新的500系列主板。

目前只有技嘉公开表示它们的Z490主板全线硬件支持PCIe 4.0,未来可以直接搭配Rocket Lake开启,B460、H410是否支持悬而未决,其他厂商是否支持也是个未知数。

那么,现在终于被Intel支持的PCIe4.0到底是什么?

首先我们看看各代PCIe的演进和性能规格。

| PCI Express 版本 |

推出 | Line 编码 |

原始 传输率 |

带宽(带宽) | ||||

|---|---|---|---|---|---|---|---|---|

| ×1 | ×2 | ×4 | ×8 | ×16 | ||||

| 1.0 | 2003 | 8b/10b | 2.5 GT/s | 250 MB/s | 0.50 GB/s | 1.0 GB/s | 2.0 GB/s | 4.0 GB/s |

| 2.0 | 2007 | 8b/10b | 5.0 GT/s | 500 MB/s | 1.0 GB/s | 2.0 GB/s | 4.0 GB/s | 8.0 GB/s |

| 3.0 | 2010 | 128b/130b | 8.0 GT/s | 984.6 MB/s | 1.97 GB/s | 3.94 GB/s | 7.88 GB/s | 15.8 GB/s |

| 4.0 | 2017 | 128b/130b | 16.0 GT/s | 1969 MB/s | 3.94 GB/s | 7.88 GB/s | 15.75 GB/s | 31.5 GB/s |

| 5.0 | 2019 | NRZ 128b/130b | 32.0 GT/s | 3938 MB/s | 7.88 GB/s | 15.75 GB/s | 31.51 GB/s | 63.0 GB/s |

| 6.0 | 2021 | PAM4 & FEC 128b/130b | 64.0 GT/s | 7877 MB/s | 15.75 GB/s | 31.51 GB/s | 63.02 GB/s | 126.03 GB/s |

PCI Express 3.0是企业计算的记忆,微处理器,网络和存储之间的通信的主要标准,但它正面临新的竞争,因为其即将到来的重大更新是一些最重要的观察者所压倒的。

控制规范的PCI-SIG官员在2010年就谈到了他们的第四代计划,并表示版本4.0将于2015年到期。现在,新的延迟,加上大数据,互联网的最新趋势物联网和移动计算领域正在推动数个顶尖IT厂商采用新的数据瓶颈方法。

PCI SIG 特殊兴趣小组自2011年年底以来一直在开发PCI Express 4.0。新的目标数据速率为每通道16GT / s [每秒千兆转发],组织一直设定这个目标,即使许多没有相信使用宽泛的铜线互连总线是可行的。该标准尚未定稿,因为参与者必须同意许多参数,包括互连属性,结构管理以及设计和构建符合PCI Express 4.0规范的系统和外设所需的编程接口。

据了解,PCIe 4.0将以每秒16千兆位传输的速度移动数据,这是当前版本的两倍。 PCI-SIG主管的工程师,IBM的Al Yanes解释说,这可以通过使用更短时间发送大量数据的突发方法来实现当前电压水平的一半或四分之一。

PCIe 4.0,具有16GT / s的数据速率和新的连接器在2017年完成。

当年,PCI SIG总裁Al Yanes在接受EE Times采访时表示:“我们正在获得16GT / s,几年前没有人想到可能。” 基地距离仍在验证中,但通常为7英寸左右。 15英寸左右的两个连接器的更长的通道将具有重新定时器,但第3代已经使用了重新定时器,现在我们需要将它们用于较短的通道。

过去几年内人工智能发展有了一个较大的飞跃,导致目前的PCI-E 3.0吞吐量不足,存储设备也使用NVMe协议,走的全是PCI-E通道,网络带宽也有了更高的速度,使得PCI-E 3.0的带宽捉襟见肘。

2017年10月底,PCI-SIG组织终于正式发布了PCIe 4.0规范,版本号v1.0。PCI-SIG强调,多卡直连以及AI参与的高吞吐计算中,PCI-E 4.0的高带宽和高传输将发挥作用。

虽然这次升级用了7年,但好在这次PCIe 4.0把频率和带宽都直接翻倍,分别达到了16.0GHz和64GB/s。而预计两年后的PCIe 5.0预计带宽和速度会继续翻倍。PCIe 4.0仍然采用前代的128b/130b标准编码,PCI-SIG强调多卡直连和AI等高吞吐计算都会需要新接口的带宽和速度。

但其实在消费级产品中PCIe 3.0仍未遇上瓶颈,新标准对普通消费者的影响其实很小。原先 PCIe 3.x x16 单向 15.8GB/s 带宽足敷使用,升级至 PCIe 4.0 版本的意义不大,反倒对于原本仅能使用 1、2、4 组通道的产品影响较大,如 NVMe 界面协定 SSD、磁盘阵列卡等;处理器和芯片组之间的沟通桥梁也可以依附 PCIe 4.0 而有更大的带宽,目前 AMD 和 Intel 双方均为单向 3.98GB/s、双向 7.9GB/s,升级 PCIe 4.0 之后能够再翻倍。

IBM的Power 9处理器将率先支持PCI-E 4.0,集成48条PCI-E 4.0通道,带宽达到了192GB/s,这也是首个支持PCI-E 4.0技术的处理器。

PCI-E的速度越来越快不仅对于工控领域重要非常,对于我们普通消费者也是意义重大。PCIe 4.0或将推动NVMe协议的固态硬盘的降价,因为通道数变少,意味着新SSD可以做的更小,成本更低,同时该规范还可以促进万兆互联网的普及。

同时,PCI-E 4.0将与人工智能在算力、应用方面起到相互推动的作用。

PCIe的规范主要是为了提升电脑内部所有总线的速度,因此带宽有多种不同规格标准,其中PCIe ×16是特别为显卡所设计。AGP的数据传输效率最高为2.1GB/s,不过对上PCIe ×16的8GB/s,很明显的就分出胜负,但8GB/s是指数据传输的理想值,并不是使用PCIe接口的显卡,就能够有突飞猛进的性能表现,实际的测试数据并不会有这么大的差异存在。

| 传输通道数 | 脚Pin总数 | 主接口区Pin数 | 总长 度 | 主接口区长度 |

|---|---|---|---|---|

| x1 | 36 | 14 | 25 mm | 7.65 mm |

| x4 | 64 | 42 | 39 mm | 21.65 mm |

| x8 | 98 | 76 | 56 mm | 38.65 mm |

| x16 | 164 | 142 | 89 mm | 71.65 mm |

| 规格 | 总线宽度 | 工作时脉 | 数据速率 |

|---|---|---|---|

| PCI 2.3 | 32位 | 33/66 MHz | 133/266 MB/s |

| PCI-X 1.0 | 64位 | 66/100/133 MHz | 533/800/1066 MB/s |

| PCI-X 2.0(DDR) | 64位 | 133 MHz | 2.1 GB/s |

| PCI-X 2.0(QDR) | 64位 | 133 MHz | 4.2 GB/s |

| AGP 2X | 32位 | 66 MHz | *2=532 MB/s |

| AGP 4X | 32位 | 66 MHz | *4=1.0 GB/s |

| AGP 8X | 32位 | 66 MHz | *8=2.1 GB/s |

| PCI-E 2.0 X1 | 1比特 | 2.5 GHz | 500 MB/s |

| PCI-E 2.0 X2 | 2比特 | 2.5 GHz | 1 GB/s |

| PCI-E 2.0 X4 | 4位 | 2.5 GHz | 2 GB/s |

| PCI-E 2.0 X8 | 8位 | 2.5 GHz | 4 GB/s |

| PCI-E 2.0 X16 | 16位 | 2.5 GHz | 8 GB/s |

计算公式:PCI-E串行总线带宽(MB/s) = 串行总线时钟频率(MHz)* 串行总线位宽(bit/8 = B)* 串行总线管线* 编码方式* 每时钟传输几组数据(cycle),例:双工PCI-E 1.0 X1,其带宽 = 2500*1/8*1*8/10*1*2=500 MB/s。

PCI Express 1.0总线频率2500 MHz,这是在100 MHz的基准频率通过锁相环振荡器(Phase Lock Loop,PLL)达到的。PCI-E 2.0总线频率从2.5GHz提高到5GHz,3.0则提高到8GHz,编码方式变成128/130。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多