摘要:卷积码在现代无线通信系统中应用十分广泛,Viterbi译码是常用的一种对卷积码的译码算法。介绍了卷积编码及Viterbi串行解码的原理及其FPGA的实现。在保证系统性能的前提下讨论了分帧式编解码在实际系统中的应用。

0 引言

在现代通信系统中,信道编码技术得到了广泛的应用。卷积码结构简单,硬件实现容易,同时有着较好的查错纠错能力,因此在无线通信中经常使用,而其解码方式常用Viterbi译码。

1 卷积编码

卷积码(Convolutional Coding)是由PgElias 于20 世纪50年代提出的一种非分组码。它实现非常简单,将要发送的信息序列经过一个特定的线性移位寄存器,即完成了编码。

卷积编码常用(n,k,m) 表示,一般n 和k 的值都比较小,其中m 为编码约束长度,它表示编码时相应的信息比特在编码器中停留的时间。卷积编码是一种前后相关联的编码过程,编码后的码元和当前的k 个比特位相关,同时也与前m - 1 个输入比特相关,使得相互关联的码元达到m × n 个。衡量卷积码性能的两个重要参数是码率 (k n)和约束长度。

2 卷积码的描述方法

卷积码的编码描述方法有很多,工程中常用的是寄存器网络结构法、码多项式法和状态图形表示法。

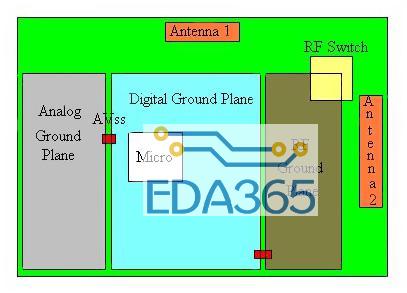

如本系统中使用的(2,1,7)卷积编码,它的寄存器网络结构法表示如图1所示。

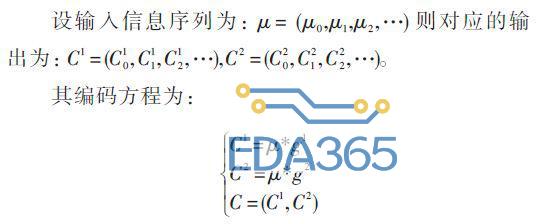

离散卷积法表示如下:

其中卷积运算用*表示, g1,g2 为脉冲冲激响应。则如图1中可以表示为:

3 卷积码的译码

由于卷积码自身没有严格的代数结构,其译码过程相对复杂。目前常用的方法有两类:

(1)代数解码。这种解码方式是利用编码本身的代数结构进行解码,但不考虑信道的统计特性;(2)概率解码。这一解码方式则充分利用了信道的统计特性。目前常用的有Viterbi译码、后验概率译码(MAP)以及它的改进算法Max_log_MAP等。本文采用的是Viterbi译码简称(VB)。

对于(n,k,m) 的二进制卷积码,编码输入的信息序列是独立等概率的,比较各种条件下的概率,即似然函数P(R|U(m)),选择其中概率的,所得就是译码值,它具有差错概率。其中R 是实际接收到的序列,U(m) 是可能的发送序列。当满足P(R|U(m′)) =max P(R|U(m)) 条件时,U(m′) 就是译码值。

假设加性高斯白噪声作为系统噪声,同时信道是无记忆性,则卷积码的似然函数为:

式中:Ri 是接收序列R 的第i 个分支;Ui (m) 是特定码字U(m) 的第i 个分支;rji 是Ri 的第j 个码元;uji (m) 是Ui (m) 的第j 个码元,每个分支由n 个码元组成。在工程实践中通常用对似然函数取对数,以加法代替乘法。对数的似然函数定义为:

当log P(R|U(m)) 的值时,译码成功。Viterbi译码利用了编码网络图的特殊结构,降低了计算的复杂度,但它本质上仍然是似然译码。算法实际执行时,边接收边比较,同时去除不可能成为似然选择对象的路径,也就是说如果两条路径到达同一状态,被选中的是具有量度的路径。这一路径称为幸存路径,对所有状态进行比较、选择,抛弃不可能的路径,从而降低了译码器的复杂性。译码从根本上说,也就是选择具有距离的码字或似然量度的码字。

4 卷积码编码的工程实现

卷积码的编码在工程中比较简单,由移位寄存器和异或组成,系统中使用(2,1,7)编码,实现原理如图2所示。在FPGA中的仿真如图3所示。

5 卷积码译码--Viterbi 译码的FPGA 实现

Viterbi算法的基本实现方法如下:在不同时刻,按照似然准则将网格图中所有的路径进行比较,保留一条具有似然值的路径(幸存路径),同时舍弃其他路径。每个时刻进行相同的操作,对每接收到的一段数据进行计算、比较并保存幸存路径,留下的路径就是所要求得的译码值。

对于卷积码(2,1,7),其编码的状态数为26,所以在译码时,译码器多需要保留26条幸存路径,和它所对应的路径度量值。由于是(2,1,7)编码每个节点将引出两条支路,但通过比较似然函数的累加值后,可以丢弃一半的路径,使得留存下来的路径总数保持不变。这样在具体实现时可以开辟固定大小的存储区,有利于硬件资源的估计。

在工程实现中采用迭代的方法,在每个时刻,对进入每个状态的所有路径的量度值进行比较,同时把具有量度值的路径存储下来。具体步骤如下:

(1)初始化,从时刻t = n 起,计算每个状态的路径和路径度量,并存储。

(2)在t + 1 时刻,接收新的一组数据,将当前的路径度量与前一时刻的度量相加,求得并保存度量并保存幸存路径,删除其余路径(3)当t < L + n( L 为反馈深度)时重复步骤(2),否则结束输出结果。

由于软判决可以对信道噪声进行更好的估计,因此它比硬判决有着更好的译码性能。因此,本文Viterbi译码器采用软判决算法,同时对信号采用线性(均匀)八电平量化。其FPGA的实现图如图4所示。

6 系统应用

在一般的通信系统中卷积编码和Viterbi译码可以是连续的,但在实际系统的应用中由于系统采用PCM分帧的模式传送,因此卷积码编码和Viterbi译码也相应改成按帧传送模式。由于卷积码的编码是数据前后相关的一种编码模式,在按帧发送后设编码和解码的初始状态均为0,如(2,1,7)编码举例,从编码的原理图2中可以清楚的看到,在相同的信道状态和传输数据一定的条件下,每一帧都将影响6 b 数据解码的正确性。

为此可以有两种解决方式:

(1)为每帧数据添加固定的6 b 数据,这种做法增加了系统的数据冗余;

(2)编码端不做任何处理,影响系统的误码率。

考虑到系统性能,由于系统传输能力还有剩余因此采用种处理方法。同时加入6 b 数据全部为0,这样不仅解决了数据误码率的问题同时保持了解码初始状态的一致性,使解码能更好的同步,有效地提高解码的正确性。

分帧式卷积编码及Viterbi 解码的FPGA 实现的联合仿真如图5所示。

分帧式传输对系统的影响如图6所示。

7 结论

在实际通信系统中,通过测量比较,分帧式编解码和连续编解码相比,在信道传输中对系统影响不大,在某些情况下分帧式编解码甚至会优于连续编解码。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多