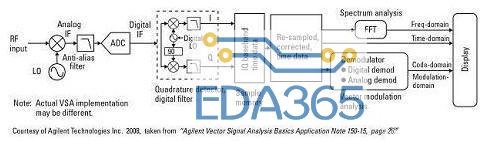

通信接收器与频谱分析仪内部信号链路的架构之间存在着相似性。利用功能强大的数字信号处理器 (DSP),先进的数字接收器可在数字域中 (而不象过去的产品那样在模拟域中) 进行同相和正交 (I-Q) 信息的解调。虽然通信接收器连续执行载频和符号时钟恢复,但频谱分析仪则以“字组” 的形式来捕获该信息,并以时点的方式进行存储,以实施进一步的处理和图形显示 (见图1)。所以,在数字域中,通信接收器和频谱分析仪之间存在着显着的差异。而在模拟域中则存在着较多的相似性。因此,面向通信市场的高性能组件的开发成果令频谱分析仪从中获益。不过。由于频谱分析仪是一种测量接收器,故而其性能要求高于大多数通信系统。

近,人们开发了用于高灵敏度通信接收器的高速模数转换器 (ADC)。凌力尔特公司推出的LTC2208便是一例,该器件可在130Msps的采样速率条件下提供16位分辨率。在高中频 (IF) 范围内,这具有适合频谱分析仪的足够线性度和动态范围。这样的一款器件可用于在进行数字处理之前完成模拟IF至数字IF的转换。然而,如果想利用IF数字化的可用性能,就需要对RF和混合信号学科的专门知识有一定程度的了解和掌握。特别要指出的是,少数关键设计领域对性能具有重大的影响:

·驱动CMOS采样及保持输入

·电源旁路电容器的紧密耦合

·高频布局方法

对于这种高性能ADC而言,另一个问题是美国政府颁布的出口许可要求。下面讨论的简化IF数字转换器同时解决了技术和商业方面的问题。

驱动CMOS采样及保持输入

在许多ADC中都采用了一个CMOS采样及保持 (S/H) 前端,旨在实现比采用一个双极S/H前端时更低的功耗。由于转换电流受限的原因,双极S/H将导致动态范围随着输入频率的提高而较快地减小。为了获得相当的性能,双极S/H将需要消耗较多的功率。有限输入电阻和偏置电流会造成驱动电路设计的复杂化。此外,双极S/H的下降速度比CMOS S/H快,因而限制了低采样速率操作。尽管拥有众多的优点,但CMOS S/H通常需要低于双极S/H的驱动阻抗。在采样速率 FS 条件下,在输入端上将有可能发生采样干扰。不稳定的输入会在ADC中引起非线性和增益误差。而对非线性和低驱动阻抗进行补偿需要采用一个复杂的驱动电路。

针对该设计问题的传统解决方案很耗时,而且往往需要不停地与供应商的应用支持工程师进行对话。然而,系统级封装 (SiP) 技术的应用造就了一种简化的IF数字转换器。

SiP技术通常在消费类应用中使用,例如:USB记忆棒和无线头戴式耳机中的RF模块。近,它被成功地应用于DC/DC转换器,旨在帮助设计师攻克众多电源应用的设计难题。目前,凌力尔特公司将该技术运用在高速16位接收器上。该公司将多年的应用专长与其业界的高速ADC和的放大器结合起来,以实现具节省空间之外形尺寸和极高性能的解决方案。LTM9001便是一款频谱分析仪应用的SiP接收器产品实例。

电源旁路电容器的紧密耦合

另一项直接影响高速ADC性能的任务是电源旁路电容器的布局。传统ADC电路板布局的一个常见问题是噪声过大,这是由从旁路电容器至ADC的长印制线所造成的。上佳的惯例是把电容器布设在尽可能靠近器件电源引脚的地方。在分立型设计中,采用导线压焊法将芯片焊接至IC封装的引线框架。这样,在的情况下,旁路电容器的距离将稍远一点。传统的封装尺寸是由其边界上的引脚数目规定的,也有可能是以充分耗散器件的功率为目的而选择。因此,键合导线的长度比 μModuleTM 接收器中的键合导线长得多,前者达到了3.5mm (图2中的左图),而后者则仅为0.8mm (图2中的右图)。所以,与采用传统封装时相比,LTM9001中的内部旁路电容器与芯片的距离可以近得多。

高频布局方法

如欲获得16位、高速ADC的完整性能,则必需进行谨慎的布局和上佳的电路设计。印刷电路板 (PCB) 布局对性能具有重大的影响,即使电路拓扑结构和组件参数值都正确,也不能忽视该问题。一个常见的错误是认为:如果IF为162MHz,则不需要采用高频布局方法。但是,对于诸如LTM9001中的高性能ADC而言,采样及保持带宽超过了700MHz。高频噪声会被采样及保持电路所捡拾,从而导致SNR下降。这是一个需要大量经验的领域。

LTM9001的衬垫设计融入了许多只能从多年的应用经验中获得的思想。此外,还把众多谨慎的布局、正确的电路设计和高性能组件作为一个单元进行了全面的特性分析和测试。结果形成了一个所需外部组件非常之少的子系统,见图3。采用无源滤波和旁路电容器传统封装器件的占板面积约为22mm x 13mm,而采用SiP时的占板面积则仅为11.25mm x 11.25mm。

IF数字转换器分块

图4中示出的LTM9001 μModule 接收器子系统实现了一个16位、130Msps ADC与一个固定增益放大器、抗混叠滤波器和旁路电容的集成,所需占用的面积不到采用传统封装时的一半。μModule接收器由安装在一个高性能、四层衬垫上的引线键合芯片、封装组件和无源组件所组成。LTM9001-AA被配置为具有20dB增益、一个200Ω的输入阻抗和一个 ±250mV 的输入范围。该匹配网络专为在这些条件下优化放大器输出与ADC输入之间的接口而设计。此外,还有一个专为162.5MHz、±25MHz (第三奈奎斯特区的中心) 而设计的两极点带通滤波器。LTM9001准备放置在位于终降频转换混频器级之后的高阶、高选择性滤波器的后面。

出口限制

美国政府对高速模数转换器的出口限制制约了在中国的通信、测试和仪表设备制造商。为了面对这些限制规定,ADC供应商推出了具集成数字降频转换器 (DDC)、分辨率为11位和14位的ADC,但是,这些器件通常并不适合于频谱分析仪。然而,LTM9001则被美国政府归类为“接收器子系统” (出口控制分类编号:ECCN 5A991),因此无需申请出口许可证。

结论

通过运用SiP技术以及来自通信行业的组件,一款简化的IF数字转换器解决了频谱分析仪接收器设计的某些关键难题。采用CMOS采样及保持前端的ADC提供了远远低于双极前端的功耗和更加优越的高频性能,但是其驱动方案则较为复杂。通过在μModule接收器中集成驱动器和抗混叠滤波器,该难题得以解决。通过采用内置紧密耦合旁路电容器的裸芯片,消除了另一个潜在的噪声源。再加上一种优化的高频布局,这些因素增加了赢得性成功的概率,并提供了始终如一的高性能。出口分类使得该接收器子系统能够不受限制地输入中国。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多