Type A型915MHz RFID读写器编码的FPGA实现就是对经过处理的待发送数据帧进行PIE编码。经过前面对PIE编码的介绍,很容易看出PIE编码具有以下特点:①电平从位窗的起始处翻转;②如果电平除了在位窗的起始处翻转,还在位窗的中间翻转则表示逻辑“0”,否则表示逻辑“1”。

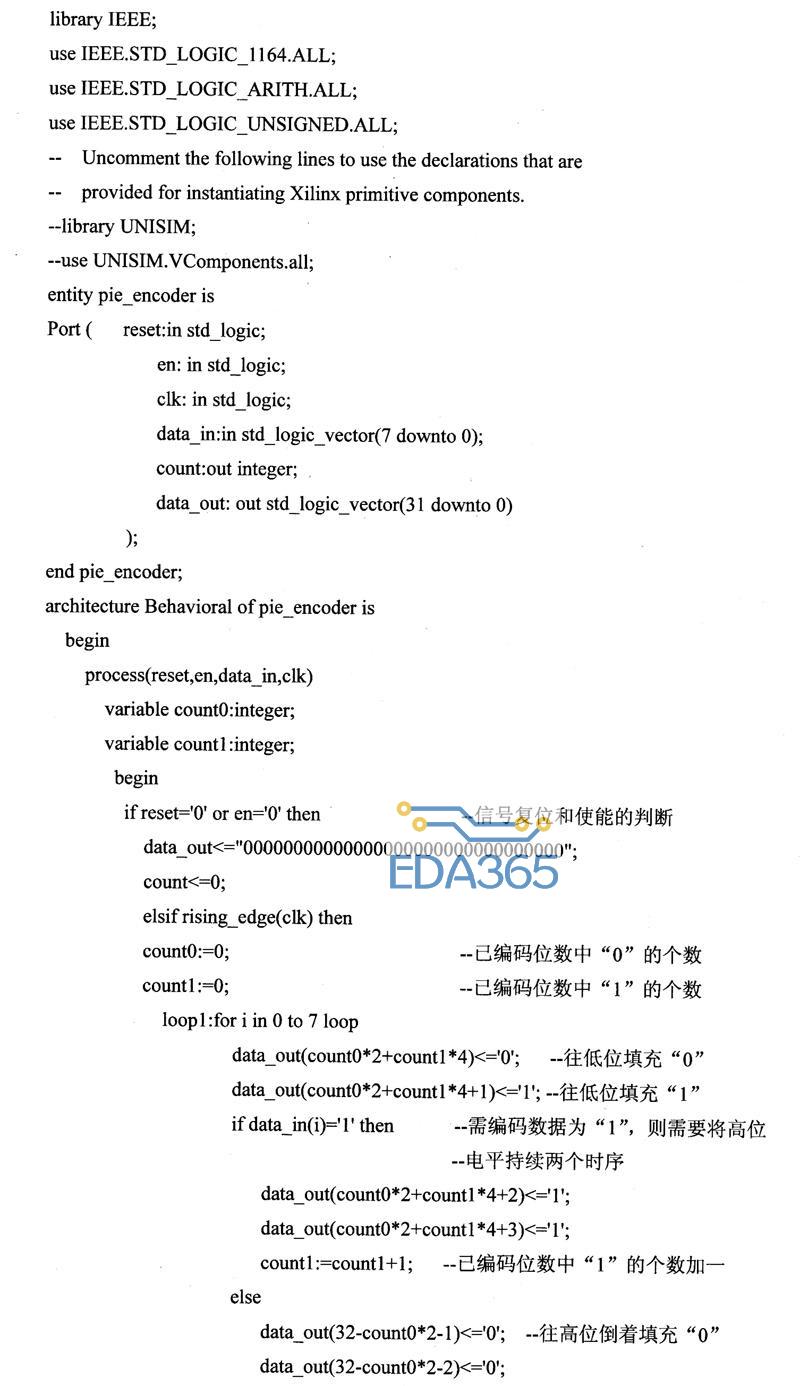

因此,本节采用以下的VHDL程序用于数据的PIE编码。

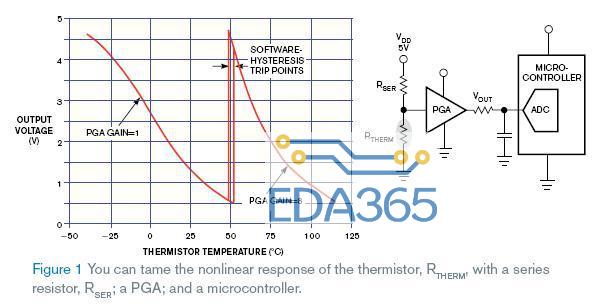

从以上的程序可以看出,利用数字逻辑的基本原理实现PIE编码非常困难,这主要是由于其编码后的信号宽度不同。在以上的程序中假设了需编码的数据位数为8位,如果进行编码,则编码后的数据长度为16≤length≤32。另外,观察前面介绍的PIE编码的形式,可以知道,“0”→“01”,“1”→“0111”。则进行某位数据的转换时,可以先填充“0”和“1”,然后根据该位数据的具体值决定是否填充两个“1”。同时,如果该位数据为“0”,则需要在输出数据的高位(即终数据的末端)倒着填充两个“0”。这样,经过8次循环,输出的数组data_out的前count*2+(8-count)*4位为所要数据,后面的位数全为0。此时,再使data_out经过一个系统抽样脉冲,获得的数据波形即为所要的PIE编码。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多