| 1引言

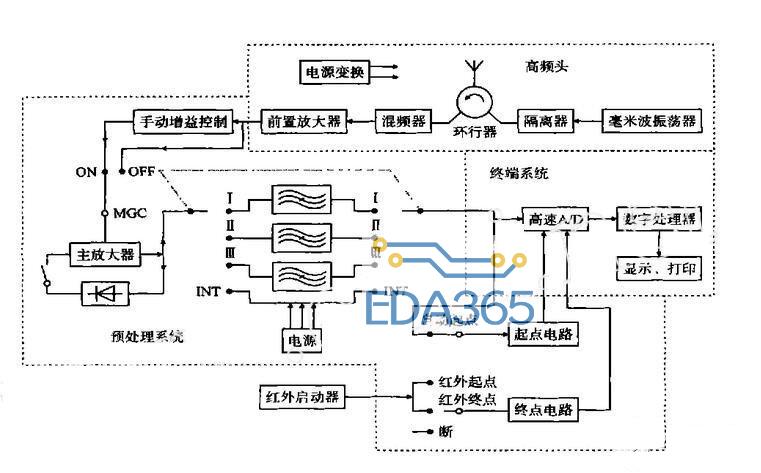

由于长距离的无屏蔽双绞线上存在噪声、衰减、信号失真等现象,在以太网接收器中需要采用信号处理技术以确保数据正确接收。均衡技术的目标是减少码间干扰(ISI)现象带来的接收信号失真。 到目前为止,大部分以太网接收器采用模拟均衡技术来减少由信道特性引起的失真[1]。本文尝试采用一种数字域上的信号处理技术,即自适应式的数字均衡技术来减少失真,其原理是利用输入数据流来调整滤波器的系数,从而使误差达到。 经典的判决反馈均衡器的结构如图1所示 [2]。 滤波器和系数更新的公式如下:  式中y(n)为滤波器输出序列, x(n)为滤波器输入序列;ck (n)为滤波器的第k个抽头系数;e( n)为误差序列;μ为调整步长。

由于这一结构易于实现,在高速数据传输时又具有较优良的特性,因此得到了广泛应用。实现这种用于以太网的自适应均衡器所需的参数可以通过仿真得到。本文讨论了在特定的以太网环境下(100Base-T4),均衡器的结构和参数设计,电路实现的结构,以及进一步优化的方向。 2结构及参数设计 在衡量用于以太网接收器的均衡器性能时,软判决信噪比(SDNR)是一个主要的参数。软判决信噪比是信号序列(硬判决处)与误差序列(即硬判决与软判决之差)的平均功率之比。误差越小,均衡器的性能越好,分割电路发生判决错误的概率越小。假设误差序列按高斯分布,均衡器的SDNR与整个以太网接收器的BER(bit error rate)具有如下关系[4]:  式中PM是误符号率(与BER有换算关系), M是符号电平数,γav是平均信噪比。 在对以太网接收器进行系统仿真时,采用了 Matlab仿真的方式[5]。在仿真中改变参数的值,同时观察对应的软判决信噪比的变化,就可以在改变参数带来的系统性能的改善和对应的硬件代价之间权衡考虑(trade-off)。 2.1 信道模拟 2.2均衡器的参数 2.3步长和字长 3均衡器的电路实现 在实现均衡器时,FFE的整个乘加部分所允许的关键路径时延为40ns(25MHz)。就FFE而言,其关键路径包括乘法器、累加器、加法器和分割电路。以今天的CMOS技术而言,不难实现一个8×6乘法器,一个10位累加器,一个10位加法器和分割器,并使其累积延时不大于20ns。DFE的情形也是如此。 3.1 FFE电路的实现

图中的乘法器(8×6)采用Booth编码的乘法器来实现,加法器(7比特)则简单的采用行波进位加法器即可(进一步的优化,可以考虑采用进位存储的结构)。 3.2 DFE电路的实现 3.3 系数更新电路的实现 3.4 分割电路及误差信号的产生

只需软判决的前三比特即可确定输出符号(硬判决)。在计算误差序列时,由于输出符号对应于+1/2,0,-1/2,误差序列的符号位可以把硬判决的LSB与软判决的第二位MSB异或得到:当硬判决符号为0时,误差序列(不含符号位)为软判决的N-1位LSB;当硬判决符号为+或-时,误差序列(不含符号位)为软判决的 N-1位LSB加减1/2。 4分析与讨论 本文对以上电路用VHDL语言进行描述,通过仿真和综合验证,电路功能基本正确。下一步的工作是对电路结构作进一步的优化,例如在结构方面,FFE的乘法器和累加器可以为奇数抽头和偶数抽头共享,但是却需要两倍于波特率的时钟信号;在电路方面,Booth乘法器和累加器均有进一步优化的潜力。 本文提出了一种适用于以太网接收器的FFE- DFE均衡器,并进行系统仿真和电路实现。希望能对高速数据传输系统的设计提供有益的借鉴。 | |||

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多