引言

MC145201是摩托罗拉公司生产的串行码编程的锁相环频率合成器,输出频率达到2GHz,内含完全可编程的 R, N和 A计数器。该芯片可外接晶振,也可以直接输入参考频率。针对不同的应用场合,MC145201具有双列直插式、SOG和TSSOP外形的贴片封装。在实际电路应用中,所需外围电路元器件较少,在小面积的电路板上面即可搭配完成一个锁相环频率合成器。

MC145201的结构

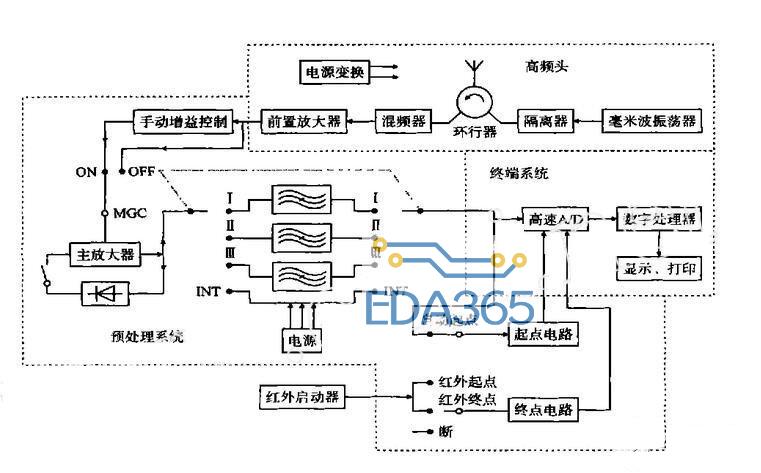

图1为MC145201的内部功能框图。

REFin(20脚)和REFout(1脚),此二脚与外部晶体振荡器连接,可形成参考频率,也可以直接连接外部参考频率,但是连接方法稍有不同。

连接晶振的时候,两个引脚还要接不大于30pF的电容,晶振范围2---15MHz。

连接外部参考频率的时候,不再需要外接电容。但是当参考信号电压范围不同时,参考频率的范围亦不同。

当Vin≥400mVp-p 时,参考频率的范围是12MHz----27MHz。

当Vin≥1Vp-p 时,参考频率的范围是4.5MHz-----27MHz。

LD(2脚)锁定检测输出脚,当锁相环路锁定时( r和 v同频同相的时候),该引脚输出高电平并有窄的脉冲;当环路失锁时,输出的脉冲为低电平(如图2所示),该引脚可用可不用,刚开始加电,片内初始化给引脚低电平,防止电路错锁,不用时悬空。

R(3脚) 和 V(4脚)是片内鉴相器的两路输出,当 R和 V同频同相时,各自输出高电平,并带有窄脉冲(如图2 (C7为低电平)所示,当C7位高电平,R和V图形互换)

VPD(5脚),VDD(14脚),VCC(12脚)为电源接入端,均不能超过5.5V,通常选取5V作为供电电源,一般VDD和VCC还要接一个1 F的电容到地。

PDOUT(6脚)鉴相器单端输出脚,外接低通滤波器即可形成环路。该引脚可用可不用,也可翻转(通过C寄存器的C7送高低位改变)。

GND(7脚) 接地端。

RX(8脚)脚接一电阻(和C寄存器的送数有关),该电阻的大小决定了PDOUT脚的输出电流。当C2和C3全为高的时候, PDOUT脚的输出电流。要想在5 V供电下到达输出电流2mA, RX接一个18K的电阻。当用 R和 V作为输出,外接环路波器时,RX可以不用。

TEST1(9脚)和TEST2(13脚)决定了MC145201内置分频器的分频比,当TEST1为高时,内置分频比为64,当TEST1为低的时,内置分频比为65。

fin(10脚) fin(11脚),其中 fin为外部环路滤波器送入MC145201引脚,通常用一个0.01F的电容连接, fin通常用1个1000pF的电容接地。

Din(19脚)、CLK(18脚)、ENB(17脚),此三个引脚为外部数据送入端。Din为串行数据输入端,在时钟由低到高转换后,比特数据流开始装载进入芯片的寄存器。其传送格式是这样规定的,即1个字节送C寄存器,2个字节送R寄存器,3个字节送 A寄存器,送数时高位在前,低位在后;ENB为低电平使能端,该引脚接高电平的时候,数据不能被读入,只有当该引脚由高转为低时才能读入数据;CLK为时钟输入脚,当时钟从低电平转为高电平的时候,数据从Din脚输入寄存器,而从高电平转为低电平的时候,数据从寄存器读出,送入内部计数器。当CLK为8个时钟周期时,访问C寄存器;CLK为16个时钟周期时,访问R寄存器;CLK为24个时钟周期时,访问A 寄存器。

同时为了保证R计数器和A计数器以及N计数器同时工作,MC145201设计了特殊的双缓存的R寄存器。原理如下:当16比特数据来的时候,首先被R寄存器的个缓存器写入,当A寄存器开始工作时,R寄存器的第2个缓存器读入个缓存器的低13位(也就是R计数器所需的),这样就保证了R、A和N计数器的同时工作。

OUTPUTA(16脚)和OUTPUTB(15脚)其中,OUTPUTA可以用作 R, V,Data Out 或者扩展引脚。

当A23=A22=1时,OUTPUTA作为 R;

当A23=1,A22=0时,OUTPUTA作为 V;

当A23=0,A22=1时,OUTPUTA作为 Data Out ;

当A23=A22=0时,OUTPUTA作为扩展引脚。

而OUTPUTB一般都是用来作为外围电路的扩展引脚来用的,他是由C0控制的,C0为低,该引脚即低,C0为高,该引脚为高,呈现高阻状态。

MC145201的实际应用

笔者在设计30MHz---88MHz,每25K一个跳变频点,300跳/秒的频率合成器的时候用到了MC145201。同时用 DDS(AD9851)驱动MC145201,能产生频谱较纯净的频率源。

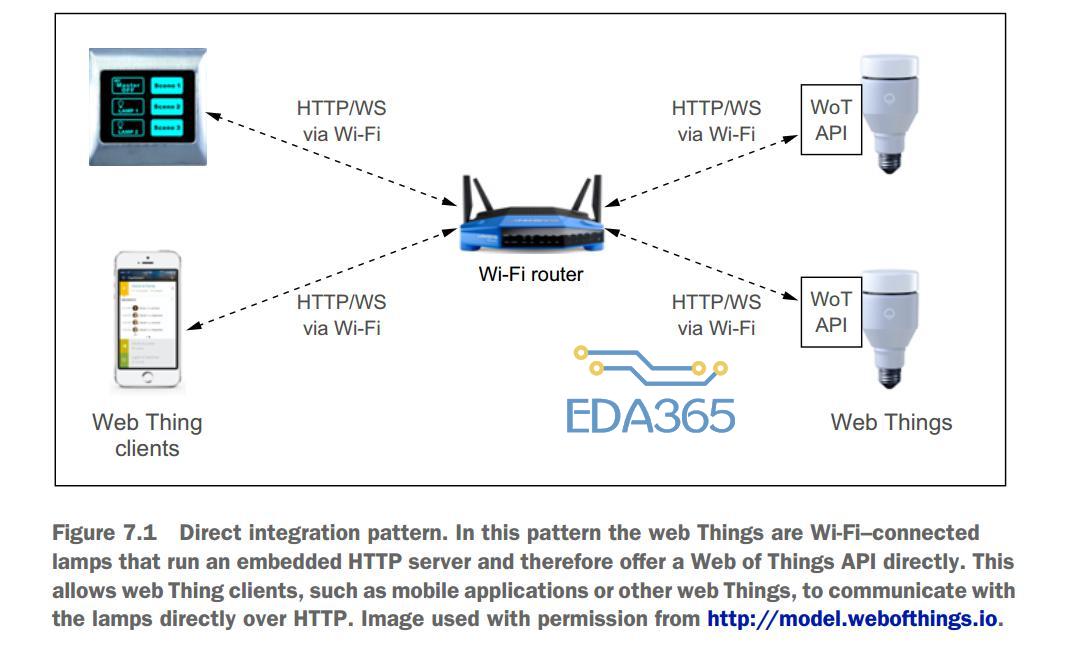

在图3中,AD9851的输出范围为10MHz----24.2424MHz,R计数器的分频比为100,N和A的分频比均为5,内置分频器的分频比为65,选用MC145201的 R和 V脚送入后面的有源比例积分滤波器,经过压控振荡器送回MC145201,电路图如图3所示。

经过对上述电路的调试,通过改变环路滤波器的参数,能很好的抑制输出电压中的载频分量和高频噪声,减少了寄生输出,得到了性能较佳的一款频率合成器。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多