1.引言

随着当前移动存储技术的快速发展和移动存储市场的高速扩大,FLASH型存储器的用量迅速增长。FLASH芯片由于其便携、可靠、成本低等优点,在移动产品中非常适用。市场的需求催生了一大批FLASH芯片研发、生产、应用企业。为保证芯片长期可靠的工作,这些企业需要在产品出厂前对FLASH存储器进行高速和细致地测试,因此,高效FLASH存储器测试算法的研究就显得十分必要。

不论哪种类型存储器的测试,都不是一个十分简单的问题,不能只将存储器内部每个存储单元依次测试一遍就得出结论,这是因为每一个存储单元的改变都有可能影响存储器内部其他单元的变化(这种情况又是常常发生的)。这种相关性产生了巨大的测试工作量。另外,FLASH存储器有其自身的特点,它只能将存储单元内的数据从“1”写为“0”,而不能从“0”写为“1”,若想实现“0”-》“1”操作,只能把整个扇区或整个存储器的数据擦除,而擦除操作要花费大量的时间。FLASH存储器还有其他特性,比如读写速度慢、写数据之前要先写入状态字、很多FLASH只适于顺序读写而不适于跳转操作等,这些特点都制约了FLASH存储器的测试。

为解决FLASH测试中的这些问题,人们提出了应用内建自测试或利用嵌入式软件等测试方法测试相关性能,都取得了比较好的效果,但这些方法大多不适用于利用测试仪进行批量的产品测试。而多数对通用存储器测试很有效的算法,由于受到FLASH器件自身的限制(如不能不能直接从“0”写为“1”),很难直接适用于FLASH测试。

文本在简单介绍FLASH芯片的结构与特点之后,说明了FLASH存储器测试程序原理。在此基础上,分析和改进了几种通用的存储器测试方法,使之能有效地应用于FLASH测试中。这些方法简单高效,故障覆盖率高,并且可以快速预先产生,与其他一些测试算法相比,更适于应用在测试仪中进行工程测试。本文分析了这些方法的主要特点,在此基础之上,介绍了实际FLASH存储器测试中应用的流程。

2.FLASH芯片的结构特征

FLASH存储器种类多样,其中最为常用的为NOR型和NAND型FLASH。通常,NOR型比较适合存储程序代码,其随机读写速度快,但容量一般较小(比如小于32 MB),且价格较高;而NAND型容量可达lGB以上,价格也相对便宜,适合存储数据,但一般只能整块读写数据,随机存取能力差。它们对数据的存取不是使用线性地址映射,而是通过寄存器的操作串行存取数据。

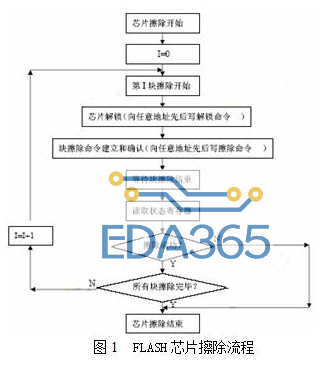

一般来说,不论哪种类型的FLASH,都有一个ID寄存器,用来读取存储器信息,可根据供应商提供的芯片资料进行具体的类型判断。另外,FLASH存储器的擦除过程相对费时,且擦除流程相对复杂。图1为FLASH芯片擦除的一般流程。

可见,擦除数据的操作限制了FLASH芯片的工作速度。此外,其他一些特性,比如读写速度慢、写数据之前要先写入状态字、很多FLASH都设有冗余单元等等,这些特点都制约了测试速度的提高。因此,设计合理的方法,或将几块FLASH并测,并且应用测试算法减少测试时间就显得十分必要。

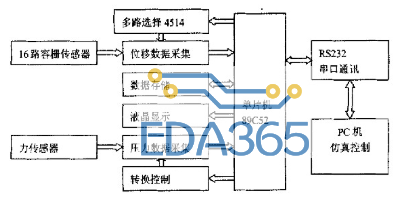

3.系统连接

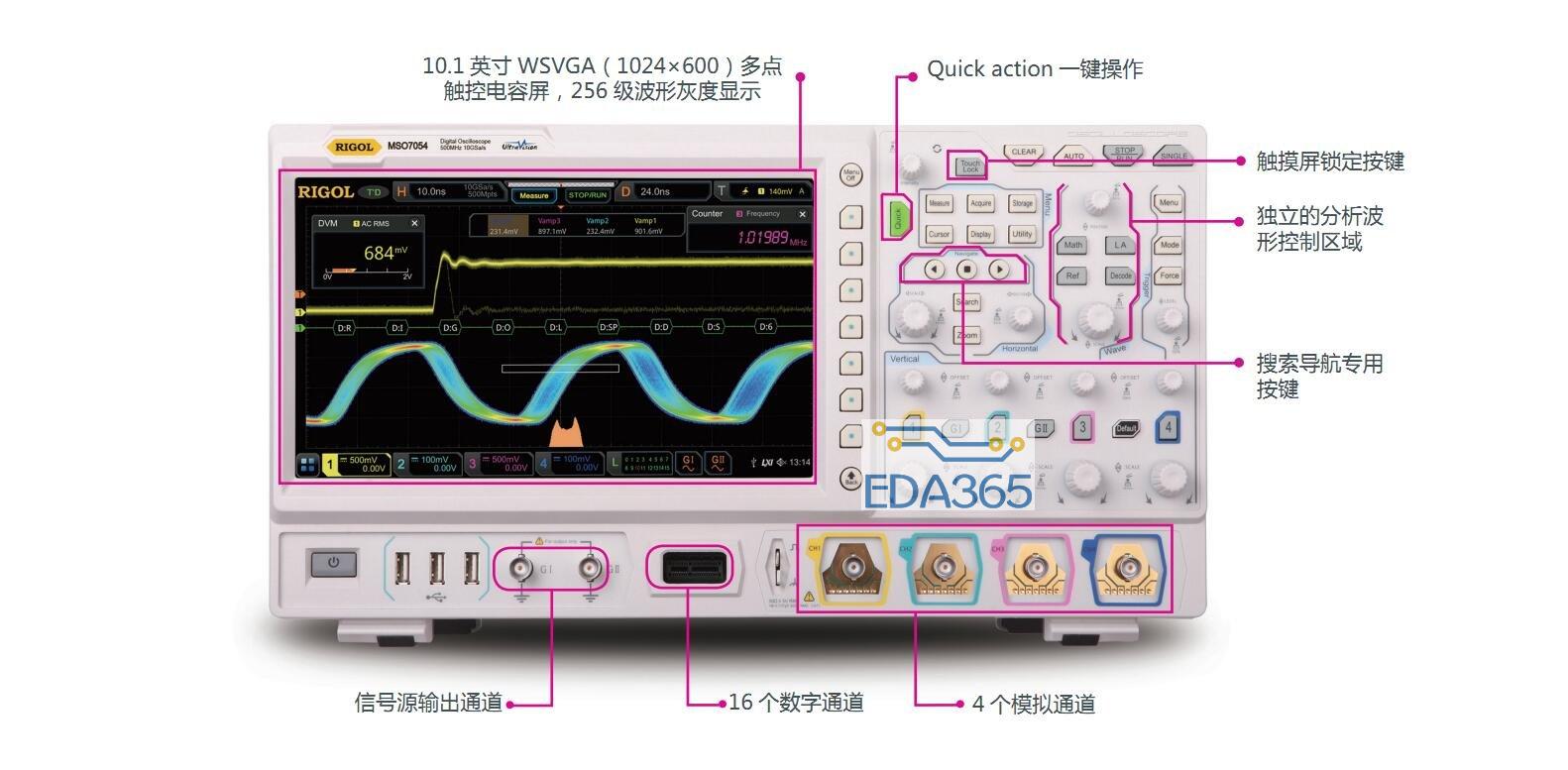

本文选用的芯片为AMD公司的NOR型FLASH——Am29LV400B及三星公司的NAND型FLASH K9F5608UOB,它们都可通过44 PIN专用适配器和数字电路测试仪的数字通道直接相连。我们所采用的硬件实验平台是北京自动测试技术所开发的BC3192数模混合测试系统,该系统可提供工作速度快,算法图形产生方式灵活,非常适合测试需要。

4.测试实现方法

假设存储器可选址的存储单元数为N,由于存储器芯片每次只能访问一个存储单元,每个单元只有“0”或“1”两种状态,所以所有可能出现的状态共2N种。由于选取的地址又是随机的,所以,当测试步数为M时,选址序列组合可能有2N NM种之多。即使采用全“0”或全“1”两种图案测试,总的测试图形也将有2NM种,这是个巨大的数字。

为了能够有效地检测存储器芯片,必须分析半导体存储器的结构,确定和选择几种能够有效检验存储器功能的图形,使之既能达到检测目的,又使测试量限定在允许范围之内。但实际应用中,由于每种测试图形都有其局限性,再加上各个生产厂家以及各种型号存储器的特性不完全一致,现在还没有最佳的统一测试方法。

根据FLASH芯片的特点,我们主要改进并使用了以下几种办法:

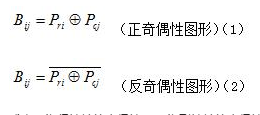

4.1 奇偶校验图形检验法

奇偶校验图形检验法是一种比较适合存储器测试的方法。在奇偶性图形检验法中,向存储单元矩阵写入的数据图案是根据存储单元选址地址码的奇偶性而定的。如果存储单元的行地址码和列地址码中有偶数个1,其奇偶性为0,则在该存储单元中写入“0”(或“1”);如果有奇数个1,其奇偶性为1,则在该存储单元中写入“1”(或“0”);存储单元矩阵存入的信号数据将是行地址码和列地址码之间的异或关系,其算法如下:

式中Pr为行地址的奇偶性,Pc为列地址的奇偶性。

FLASH芯片奇偶性图形功能检测的流程是:首先根据算法写入背景图形,然后逐位读出并检验结果的正确性,再将芯片数据擦除,以反码图形重复上述测试过程。其总的测试步数为M=4N。

由于奇偶性图形是不对称的,任何一位的地址译码器失效都会引起本应写入互为反码数据的两个存储单元之一重复选址,并且第二次选址改变了第一次选址时写入的内容,而另一个存储单元未被访问。因此地址奇偶性图形可以很好地检验出地址译码器的故障。

奇偶性图形每次都把整个存储器单元写完后再整体读出,没有反复擦除的过程(整个过程只需擦除两次),非常适用于FLASH芯片测试。

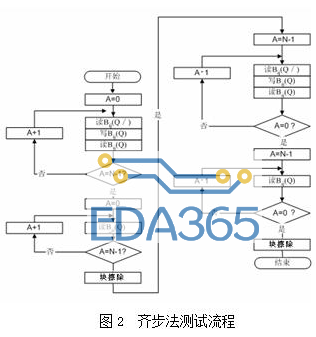

4.2 齐步法

齐步法[6]是对存储器的每个单元依次进行检验的一种方法。首先从第一个存储单元开始,逐个对每个单元进行取反和检验,直到最后一个单元检测结束才完成一遍扫描。然后,在背景为反码的情况下,从第一个存储单元开始,逐个对每个单元进行取反和检验,直到最后一个单元检测结束。整个过程就像所有单元一起向前走步一样,因此称为“齐步法”。根据FLASH芯片特点,我们改变在反码背景条件下走步的过程,把它改造如下,形成了适合的齐步算法。

在图2中给出了测试FLASH齐步法的测试流程:

在测试之前,每个存储单元具有信息“1”。首先在存储矩阵中写入背景图案(初始状态为全“1”),然后从地址A0开始选址进行读“1”,写“0”,读“0”操作,并检验读出结果。接着,依次到下一个选址单元重复该操作(读“1”,写“0”,读“0”),直到全部存储单元(A=N-1)重复完为止。再在读操作方式下对全部存储单元进行一次正向扫描读出,检查有无正向对反向的多重写入问题。然后将存储器输入擦除,使之全部单元为全“1”。进而开始反向扫描:从最高地址AN-1开始执行读“1”,写“0”,读“0”操作,逐位进行上述操作过程,直至最终地址为AN-1,最后对全部存储单元进行读“0”扫描,以检验读出结果的正确性。

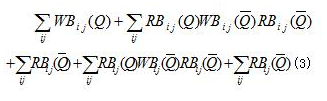

用这种测试算法检测存储芯片,可使每个存储单元都被访问。既能保证每个存储单元都能存储“1”和“0”数据,又能保证每个存储单元都受到周围其他单元的读“1”、读“0”和写“1”、写“0”的打扰。齐步法总的测试步数为:

式(3)中,W表示写操作,R表示读操作,Q表示“1”, 表示“0”。Bij表示存储器第i行j列的存储单元。如WBij(Q)就表示对第i行j列的存储单元进行写“1”操作所用的时间。

由式(3)可知,其测试步数共9N,且整个过程只需两次擦除操作,可见它是一种即快速又有效的方法。

4.3 移动变反法

移动变反测试法是按顺序变反每个地址存储单元数据的方法。它需要在变反前后读出每个存储单元的数据,而且,还必须借助于前进和后退的地址寻址序列产生地址跳跃,地址以20、21…、2n-1次方的增量变化(n是地址位数)。按照以上规律进行地址跳变后,再对每个地址进行三次操作:读、写和读即可完成一个循环。

以上操作的目的主要在于地址间产生有效相互打扰,但显然如果以整个芯片为单元进行上述操作需要多次擦除数据,因此对FLASH测试芯片应做如此改进:以扇区为单元完成操作。假设FLASH芯片有N个扇区,移动变反法的功能测试先要以“1”为背景图案写入全部存储单元。首先,在第一个扇区,对A0存储单元读出并验证是“1”,再将该存储单元改写成“0”,最后读出该存储单元的信息以证明新写入的“0”仍存于该存储单元中。第一扇区测试地址按有效位的阶20递增,对每个存储单元都要重复上述的读“1”,写“0”读“0”的操作过程,需要测试步长为3n(n为该扇区的存储单元数)才能使全部的存储单元都变成“0”。这次测试的地址序列是递增1的,即由地址最低位A0增加到最高位A(n-1),对A(n-1)存储单元进行读“1”,写“0”和读“0”验证。

对第二个扇区,以下一个地址阶21作为地址增量的变化量,每次用不同的地址位作为最低位(分别为第0位和第1位),使地址以此增量的变化通过所有可能的地址。因此在一次测试程序中所有地址的存储单元都被测试一次。

然后,依次以22、24…2N作为地址增量,重复上述过程,每完成一个循环便产生一个循环进位。

由于各个扇区的大小不同,移动变反法功能测试图形步长为3n(n为最大扇区存储单元个数)。以扇区为单元的测试实际上是一种对芯片功能的抽测,因为它并没有进行对各单元存取数据进行反复打扰,以验证其地址线间信号改变所带来的影响,但这种方法分别在各个扇区对邻近地址线一一做了打扰测试,由于各个扇区结构根本上是相同的,因此这种抽测很有代表性,并且把测试时间减少了一个数量级。

移动变反法测试图形是一种良好的折衷测试方案。因为它几乎具有各种测试图形的最好特点,可以用较少的试验步数测试尽可能多的存储单元间打扰的相互影响。在具体程序中,“1”场变反为“0”场是按序选择地址,并通过写入这些地址而产生的,在两次读出之间有一次写操作。移动变反法测试包括了功能测试和动态测试,功能测试保证被测存储单元不受读、写其他存储单元的影响,动态测试预测最坏和最好条件下的取数时间,并预测地址变换对这些时间的影响。

这种测试方法易于实现,它是在跳步算法的基础上,通过改变跳步的长度,减小了算法的复杂度。移动变反法测试是一种具有良好功能测试和动态测试特点的测试图形,并且所需的测试时间较短,在很多情况下都有很好的效果。尤其是对于较大容量存储器的测试,该方法特别有效。

移动变反法还可以作进一步扩展,即对数据做移动变反处理。以芯片为32位总线为例,首先对存储器各单元写入0xAAAAAAAA,检验并擦除,然后对存储器写入0xCCCCCCCC,检验并擦除,以后依次写入0xF0F0F0F0,0x0F0F0F0F,0xFF00FF00,0x00FF00FF,0xFFFF0000,0x0000FFFF, 0xFFFFFFFF,0x0,都在检验所写的正确性后再擦除数据。其原理与地址移动变反相同,在此不再赘述。

4.测试方法的综合使用和流水测试

以上,从算法的角度上提高了FLASH芯片的可测性。虽然NOR、NAND型FLASH结构不同,但由于以上算法都可通过计算,顺序产生测试图形,因此可通用于以上两类器件的测试中。

上述三种方法各有优点,在实际应用中可配合使用。地址奇偶性图形测试最为方便高效,因为在写入图形过程中每次只改变一位地址线,而且写入的是相反的数据,所以如果哪一位地址线出现短路立刻会被检查出来,使用该方法最适宜检验地址译码器的故障。齐步法适于用来检验多重地址选择与译码器的故障,并且可以检测写入时噪声对存储芯片特性的影响,它能保证正确的地址译码和每个存储单元存储“1”和“0”信息的能力。在大多数生产测试中,联合使用这两种方法可以判别出FLASH绝大多数的故障。当然,各个厂家生产的芯片在结构和工艺上有一定区别,因此出现各种错误的概率也不同,可以根据实际情况调整方法。由于设计问题,有些芯片还有可能出现其他一些不太常见的错误,这就需要进行更详尽的测试,这时使用移动变反测试法就比较合适。这种方法可以很好地测试芯片的动态错误,并且可根据具体需要详细展开测试或简化测试,对于产品性能分析十分有效。

在具体程序设计时,为简化算法执行,可以将读取产品型号、调用读写命令的语句作为子程序存储在测试仪中,每次需要时都可以无缝调用。

在测试过程中,最耗费时间的是程序擦除操作,一次擦除往往就需要几秒,其解决办法是将擦除工序单独处理。在实际应用中,可使用两台测试仪,其中,在擦除时几个芯片并行运行。这样,一台设备用于读、写、测试,另一台设备用于擦除数据,就可以有效地形成流水线操作,大大节省测试时间。此外,将几种方法综合使用,还有助于提高故障覆盖率。

5.实验结果

根据上述思想,我们在国产BC3192的测试系统平台上,对AMD公司的NOR型FLASH——Am29LV400B及三星公司的NAND型FLASH——9F5608UOB都进行了测试。实验表明,和传统的以棋盘格为基础的测试图形相比,奇偶校验法、齐步法和移动变反法产生的测试图形故障覆盖率更高,这些算法由于最多只有两次芯片擦除操作,所以测试时间完全能符合工程测试需要,其中,移动变反法没有擦除操作,所以测试速度最快。在实验中,我们采用上述三种方法中任意一种,按照流水的方法测试,在相同故障覆盖率下,都可以使测试效率可提高40%以上。

6.结论

本文是在传统存储器测试理论基础上对FLASH测试的尝试,该方法保留了传统方法的优点,较好地解决了FLASH存储器测试的困难。该方法方便快捷,流程简单,所有测试图形都可以事先生成,这样就可以直接加载到测试仪中,有利于直接应用于测试仪进行生产测试。

责任编辑:gt

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多