#include "stm32f10x.h"

#if defined (STM32F10X_LD_VL) || (defined STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)

#define SYSCLK_FREQ_24MHz 24000000

#else

#define SYSCLK_FREQ_72MHz 72000000

#endif

#if defined (STM32F10X_HD) || (defined STM32F10X_XL) || (defined STM32F10X_HD_VL)

#endif

#define VECT_TAB_OFFSET 0x0

#ifdef SYSCLK_FREQ_HSE

uint32_t SystemCoreClock = SYSCLK_FREQ_HSE;

#elif defined SYSCLK_FREQ_24MHz

uint32_t SystemCoreClock = SYSCLK_FREQ_24MHz;

#elif defined SYSCLK_FREQ_36MHz

uint32_t SystemCoreClock = SYSCLK_FREQ_36MHz;

#elif defined SYSCLK_FREQ_48MHz

uint32_t SystemCoreClock = SYSCLK_FREQ_48MHz;

#elif defined SYSCLK_FREQ_56MHz

uint32_t SystemCoreClock = SYSCLK_FREQ_56MHz;

#elif defined SYSCLK_FREQ_72MHz

uint32_t SystemCoreClock = SYSCLK_FREQ_72MHz;

#else

uint32_t SystemCoreClock = HSI_VALUE;

#endif

__I uint8_t AHBPrescTable[16] = {0, 0, 0, 0, 0, 0, 0, 0, 1, 2, 3, 4, 6, 7, 8, 9};

static void SetSysClock(void);

#ifdef SYSCLK_FREQ_HSE

static void SetSysClockToHSE(void);

#elif defined SYSCLK_FREQ_24MHz

static void SetSysClockTo24(void);

#elif defined SYSCLK_FREQ_36MHz

static void SetSysClockTo36(void);

#elif defined SYSCLK_FREQ_48MHz

static void SetSysClockTo48(void);

#elif defined SYSCLK_FREQ_56MHz

static void SetSysClockTo56(void);

#elif defined SYSCLK_FREQ_72MHz

static void SetSysClockTo72(void);

#endif

#ifdef DATA_IN_ExtSRAM

static void SystemInit_ExtMemCtl(void);

#endif

void SystemInit (void)

{

RCC->CR |= (uint32_t)0x00000001;

#ifndef STM32F10X_CL

RCC->CFGR &= (uint32_t)0xF8FF0000;

#else

RCC->CFGR &= (uint32_t)0xF0FF0000;

#endif

RCC->CR &= (uint32_t)0xFEF6FFFF;

RCC->CR &= (uint32_t)0xFFFBFFFF;

RCC->CFGR &= (uint32_t)0xFF80FFFF;

#ifdef STM32F10X_CL

RCC->CR &= (uint32_t)0xEBFFFFFF;

RCC->CIR = 0x00FF0000;

RCC->CFGR2 = 0x00000000;

#elif defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)

RCC->CIR = 0x009F0000;

RCC->CFGR2 = 0x00000000;

#else

RCC->CIR = 0x009F0000;

#endif

#if defined (STM32F10X_HD) || (defined STM32F10X_XL) || (defined STM32F10X_HD_VL)

#ifdef DATA_IN_ExtSRAM

SystemInit_ExtMemCtl();

#endif

#endif

SetSysClock();

#ifdef VECT_TAB_SRAM

SCB->VTOR = SRAM_BASE | VECT_TAB_OFFSET;

#else

SCB->VTOR = FLASH_BASE | VECT_TAB_OFFSET;

#endif

}

void SystemCoreClockUpdate (void)

{

uint32_t tmp = 0, pllmull = 0, pllsource = 0;

#ifdef STM32F10X_CL

uint32_t prediv1source = 0, prediv1factor = 0, prediv2factor = 0, pll2mull = 0;

#endif

#if defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)

uint32_t prediv1factor = 0;

#endif

tmp = RCC->CFGR & RCC_CFGR_SWS;

switch (tmp)

{

case 0x00:

SystemCoreClock = HSI_VALUE;

break;

case 0x04:

SystemCoreClock = HSE_VALUE;

break;

case 0x08:

pllmull = RCC->CFGR & RCC_CFGR_PLLMULL;

pllsource = RCC->CFGR & RCC_CFGR_PLLSRC;

#ifndef STM32F10X_CL

pllmull = ( pllmull >> 18) + 2;

if (pllsource == 0x00)

{

SystemCoreClock = (HSI_VALUE >> 1) * pllmull;

}

else

{

#if defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)

prediv1factor = (RCC->CFGR2 & RCC_CFGR2_PREDIV1) + 1;

SystemCoreClock = (HSE_VALUE / prediv1factor) * pllmull;

#else

if ((RCC->CFGR & RCC_CFGR_PLLXTPRE) != (uint32_t)RESET)

{

SystemCoreClock = (HSE_VALUE >> 1) * pllmull;

}

else

{

SystemCoreClock = HSE_VALUE * pllmull;

}

#endif

}

#else

pllmull = pllmull >> 18;

if (pllmull != 0x0D)

{

pllmull += 2;

}

else

{

pllmull = 13 / 2;

}

if (pllsource == 0x00)

{

SystemCoreClock = (HSI_VALUE >> 1) * pllmull;

}

else

{

prediv1source = RCC->CFGR2 & RCC_CFGR2_PREDIV1SRC;

prediv1factor = (RCC->CFGR2 & RCC_CFGR2_PREDIV1) + 1;

if (prediv1source == 0)

{

SystemCoreClock = (HSE_VALUE / prediv1factor) * pllmull;

}

else

{

prediv2factor = ((RCC->CFGR2 & RCC_CFGR2_PREDIV2) >> 4) + 1;

pll2mull = ((RCC->CFGR2 & RCC_CFGR2_PLL2MUL) >> 8 ) + 2;

SystemCoreClock = (((HSE_VALUE / prediv2factor) * pll2mull) / prediv1factor) * pllmull;

}

}

#endif

break;

default:

SystemCoreClock = HSI_VALUE;

break;

}

tmp = AHBPrescTable[((RCC->CFGR & RCC_CFGR_HPRE) >> 4)];

SystemCoreClock >>= tmp;

}

static void SetSysClock(void)

{

#ifdef SYSCLK_FREQ_HSE

SetSysClockToHSE();

#elif defined SYSCLK_FREQ_24MHz

SetSysClockTo24();

#elif defined SYSCLK_FREQ_36MHz

SetSysClockTo36();

#elif defined SYSCLK_FREQ_48MHz

SetSysClockTo48();

#elif defined SYSCLK_FREQ_56MHz

SetSysClockTo56();

#elif defined SYSCLK_FREQ_72MHz

SetSysClockTo72();

#endif

}

#ifdef DATA_IN_ExtSRAM

void SystemInit_ExtMemCtl(void)

{

RCC->AHBENR = 0x00000114;

RCC->APB2ENR = 0x000001E0;

GPIOD->CRL = 0x44BB44BB;

GPIOD->CRH = 0xBBBBBBBB;

GPIOE->CRL = 0xB44444BB;

GPIOE->CRH = 0xBBBBBBBB;

GPIOF->CRL = 0x44BBBBBB;

GPIOF->CRH = 0xBBBB4444;

GPIOG->CRL = 0x44BBBBBB;

GPIOG->CRH = 0x44444B44;

FSMC_Bank1->BTCR[4] = 0x00001011;

FSMC_Bank1->BTCR[5] = 0x00000200;

}

#endif

#ifdef SYSCLK_FREQ_HSE

static void SetSysClockToHSE(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

#if !defined STM32F10X_LD_VL && !defined STM32F10X_MD_VL && !defined STM32F10X_HD_VL

FLASH->ACR |= FLASH_ACR_PRFTBE;

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

#ifndef STM32F10X_CL

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_0;

#else

if (HSE_VALUE <= 24000000)

{

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_0;

}

else

{

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_1;

}

#endif

#endif

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV1;

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_HSE;

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x04)

{

}

}

else

{

}

}

#elif defined SYSCLK_FREQ_24MHz

static void SetSysClockTo24(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

#if !defined STM32F10X_LD_VL && !defined STM32F10X_MD_VL && !defined STM32F10X_HD_VL

FLASH->ACR |= FLASH_ACR_PRFTBE;

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_0;

#endif

[page]

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV1;

#ifdef STM32F10X_CL

RCC->CFGR &= (uint32_t)~(RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL);

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLSRC_PREDIV1 |

RCC_CFGR_PLLMULL6);

RCC->CFGR2 &= (uint32_t)~(RCC_CFGR2_PREDIV2 | RCC_CFGR2_PLL2MUL |

RCC_CFGR2_PREDIV1 | RCC_CFGR2_PREDIV1SRC);

RCC->CFGR2 |= (uint32_t)(RCC_CFGR2_PREDIV2_DIV5 | RCC_CFGR2_PLL2MUL8 |

RCC_CFGR2_PREDIV1SRC_PLL2 | RCC_CFGR2_PREDIV1_DIV10);

RCC->CR |= RCC_CR_PLL2ON;

while((RCC->CR & RCC_CR_PLL2RDY) == 0)

{

}

#elif defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || defined (STM32F10X_HD_VL)

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_PREDIV1 | RCC_CFGR_PLLXTPRE_PREDIV1_Div2 | RCC_CFGR_PLLMULL6);

#else

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLXTPRE_HSE_Div2 | RCC_CFGR_PLLMULL6);

#endif

RCC->CR |= RCC_CR_PLLON;

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

}

else

{

}

}

#elif defined SYSCLK_FREQ_36MHz

static void SetSysClockTo36(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

FLASH->ACR |= FLASH_ACR_PRFTBE;

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_1;

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV1;

#ifdef STM32F10X_CL

RCC->CFGR &= (uint32_t)~(RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL);

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLSRC_PREDIV1 |

RCC_CFGR_PLLMULL9);

RCC->CFGR2 &= (uint32_t)~(RCC_CFGR2_PREDIV2 | RCC_CFGR2_PLL2MUL |

RCC_CFGR2_PREDIV1 | RCC_CFGR2_PREDIV1SRC);

RCC->CFGR2 |= (uint32_t)(RCC_CFGR2_PREDIV2_DIV5 | RCC_CFGR2_PLL2MUL8 |

RCC_CFGR2_PREDIV1SRC_PLL2 | RCC_CFGR2_PREDIV1_DIV10);

RCC->CR |= RCC_CR_PLL2ON;

while((RCC->CR & RCC_CR_PLL2RDY) == 0)

{

}

#else

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLXTPRE_HSE_Div2 | RCC_CFGR_PLLMULL9);

#endif

RCC->CR |= RCC_CR_PLLON;

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

}

else

{

}

}

#elif defined SYSCLK_FREQ_48MHz

static void SetSysClockTo48(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

FLASH->ACR |= FLASH_ACR_PRFTBE;

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_1;

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;

#ifdef STM32F10X_CL

RCC->CFGR2 &= (uint32_t)~(RCC_CFGR2_PREDIV2 | RCC_CFGR2_PLL2MUL |

RCC_CFGR2_PREDIV1 | RCC_CFGR2_PREDIV1SRC);

RCC->CFGR2 |= (uint32_t)(RCC_CFGR2_PREDIV2_DIV5 | RCC_CFGR2_PLL2MUL8 |

RCC_CFGR2_PREDIV1SRC_PLL2 | RCC_CFGR2_PREDIV1_DIV5);

RCC->CR |= RCC_CR_PLL2ON;

while((RCC->CR & RCC_CR_PLL2RDY) == 0)

{

}

RCC->CFGR &= (uint32_t)~(RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL);

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLSRC_PREDIV1 |

RCC_CFGR_PLLMULL6);

#else

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL6);

#endif

RCC->CR |= RCC_CR_PLLON;

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

}

else

{

}

}

#elif defined SYSCLK_FREQ_56MHz

static void SetSysClockTo56(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

FLASH->ACR |= FLASH_ACR_PRFTBE;

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2;

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;

#ifdef STM32F10X_CL

RCC->CFGR2 &= (uint32_t)~(RCC_CFGR2_PREDIV2 | RCC_CFGR2_PLL2MUL |

RCC_CFGR2_PREDIV1 | RCC_CFGR2_PREDIV1SRC);

RCC->CFGR2 |= (uint32_t)(RCC_CFGR2_PREDIV2_DIV5 | RCC_CFGR2_PLL2MUL8 |

RCC_CFGR2_PREDIV1SRC_PLL2 | RCC_CFGR2_PREDIV1_DIV5);

RCC->CR |= RCC_CR_PLL2ON;

while((RCC->CR & RCC_CR_PLL2RDY) == 0)

{

}

RCC->CFGR &= (uint32_t)~(RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL);

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLSRC_PREDIV1 |

RCC_CFGR_PLLMULL7);

#else

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL7);

#endif

RCC->CR |= RCC_CR_PLLON;

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

}

else

{

}

}

#elif defined SYSCLK_FREQ_72MHz

static void SetSysClockTo72(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

FLASH->ACR |= FLASH_ACR_PRFTBE;

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2;

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;

#ifdef STM32F10X_CL

RCC->CFGR2 &= (uint32_t)~(RCC_CFGR2_PREDIV2 | RCC_CFGR2_PLL2MUL |

RCC_CFGR2_PREDIV1 | RCC_CFGR2_PREDIV1SRC);

RCC->CFGR2 |= (uint32_t)(RCC_CFGR2_PREDIV2_DIV5 | RCC_CFGR2_PLL2MUL8 |

RCC_CFGR2_PREDIV1SRC_PLL2 | RCC_CFGR2_PREDIV1_DIV5);

RCC->CR |= RCC_CR_PLL2ON;

while((RCC->CR & RCC_CR_PLL2RDY) == 0)

{

}

RCC->CFGR &= (uint32_t)~(RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL);

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLSRC_PREDIV1 |

RCC_CFGR_PLLMULL9);

#else

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

#endif

RCC->CR |= RCC_CR_PLLON;

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

}

else

{

}

}

#endif

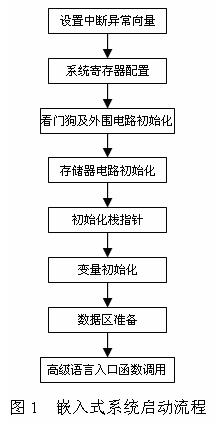

关键字:启动过程 system stm32f10x c  热门文章

更多

热门文章

更多