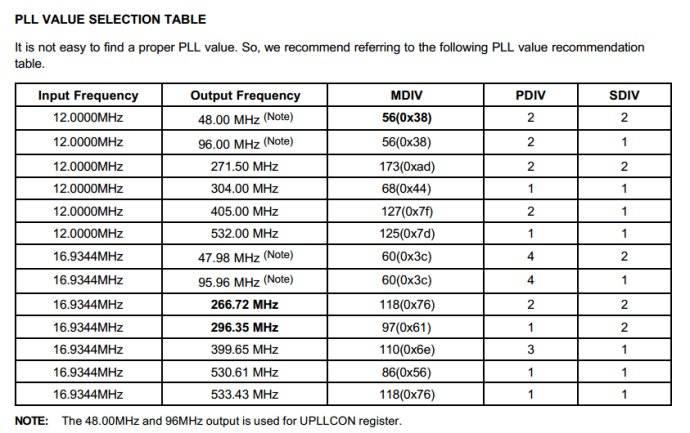

2440的晶振频率为12MHZ,有两个PLL:MPLL和UPLL,其中MPLL产生FCLK、HCLK、PCLK;UPLL产生UCLK。FCLK为ARM核提供时钟,HCLK为AHB总线时钟,PCLK为APB总线时钟,UCLK为USB总线时钟。所以要2440正常工作,主要是要设置好FCLK,所以主要配置MPLL以及分频。

时钟初始化:

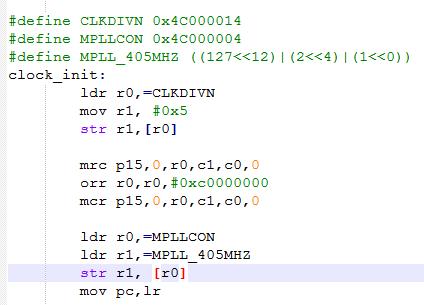

1、设置lock time(默认就行)

2、设置分频系数(设置CLKDIVN寄存器)

3、设置CPU到异步工作模式(参考手册page243)

4、设置fclk(设置MPLLCON寄存器)

参考汇编代码(设置FCLK为405M,分频分别为F:H:P=1:4:8):

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多