其中,单口RAM接口可以实现两类用途:一、挂接单口RAM,使得FreeARM7能够正确地读写数据;二、挂接外设,使得FteeARM7能够正确操作外设。

2 微处理器改进与逻辑扩展

基于FreeARM7的微处理器改进与逻辑扩展的结构如图1所示。预期的实现目标是:在主机上编写嵌入式程序汇编成机器码后,经过USB 1.1设备控制器传输至双端口RAM中,在微处理器代码下载模式下,代码下载控制逻辑将双端口RAM中的机器代码装载至ROM中,之后启动微处理器正常工作模式,微处理器执行ROM中的嵌入式代码,接收主机通过USB传送来的参数值,并将运行结果通过USB返回至主机。

基于Cyclone II FPGA具体实现时,ROM、RAM和双端口RAM都是利用Quartus II软件中MegaWizardPlug-In.Manager工具例化相应的存储模块,而其他硬件逻辑的扩展都是以IP核(Verilog描述)的形式出现。[page]

2.1 微处理器lP核改进

FreeARM7 IP核是微处理器的核心部分,不能直接作为微处理器使用,其原因是数据总线需要读取ROM内的数据、本文选择Philips公司32位ARM7微处理器LPC2101作为原型设计。LPC2101带有适当的存储资源,内嵌2 KB片内静态RAM和8 KB的Flash存储器,且软件可移植性好,工作可靠。参考LPC2101工作原理,当FreeARM7的输出信号ram_addr的最高4位为4'b0时,表示数据总线需要读取ROM的数据。为解决该问题,新增一个wrap文件lpc2101_arm.v完成该功能。它的作用是:当ram_addr[31:28]==4'b0时,该逻辑直接从rom_en、rom_addr、rom_data的接口中读取ROM数据,送入ram rdata。

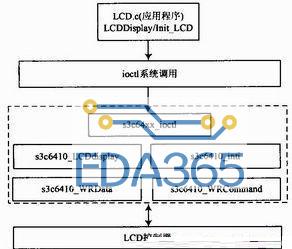

2.2 USB1.1设备控制器

本文选用的USB设备控制器是课题组早期项目之一,它是由Opencores网站提供的初级开源版本改进而成,其结构如图2所示。IP核支持低速和全速模式,共有1个控制传输端点(EP0)、7个其他可配置端点,且缺少微处理器也能响应主机对设备的枚举。收发器电路主要完成模/数信号转换,即在OUT事物中将模拟信号D+和D-转换成串行接口引擎模块可识别的数字信号rxd、rxdp和rxdn,在IN事物中将数字信号txdp和

txdn在使能信号txoe的控制下转换成模拟信号D+和D-;串行接口引擎模块主要完成收发包,根据传输方向可分为接收和发送,主要包括总线检测、同步检测、时钟恢复、不归零反向编码和解码、位填充及位去除、数据的串/并转换;协议层包括协议引擎态机、组包、解包、FIFO控制器;端点O控制器主要负责响应主机标准请求;描述符RAM存储了设备的各种描述符;其他端点控制器及FIFO提供了配置接口,目的是预留给开发者进行IP核移植。

2.3 代码下载控制逻辑

该逻辑主要功能是在代码下载模式下,将双端口RAM中的汇编程序转移到ROM中,其主要任务是产生读双端口RAM使能信号和地址信号,以及写ROM的使能信号和地址信号。在硬件逻辑中通过计数器实现。当系统复位或退出代码下载模式时,计数器:rom_wr_cnt清零,否则当USB接收完一个包(64字节)后,置计数器使能信号cnt_vld有效,rom_wr_cnt开始计数。cnt_vld直接作为读双端口RAM的使能信号,cnt_vld两级缓存后作为写ROM的使能信号。同时,rom_wr_cnt的低8位直接作为读双端口RAM的地址信号,rom_wr_cnt计算结果经过两级缓存后作为写ROM的地址信号。当64字节转移完毕后,置cnt_vld无效,此时rom_wr_cnt锁存当前值,等待下一个包接收完毕后再次置cnt_vld有效,代码下载控制逻辑就将下一个包的数据追加到ROM中,反复进行就完成了代码经由USB接口下载至ROM中。

3 嵌入式代码的开发

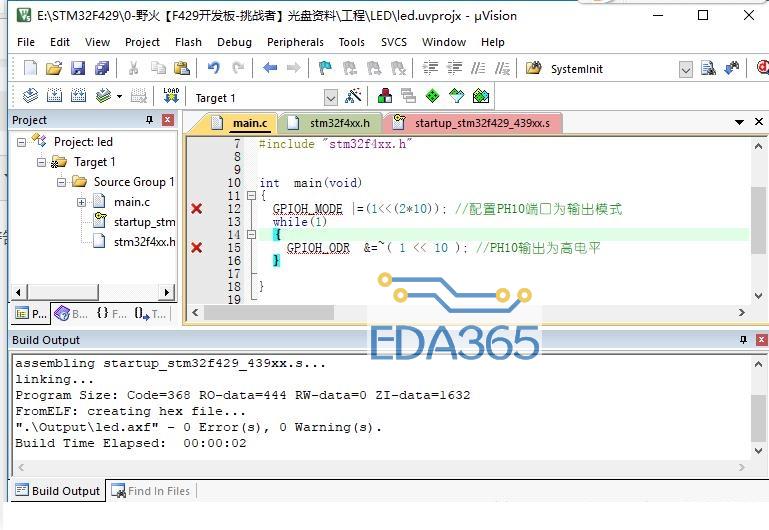

3.1 uVision3.63环境设置

利用μVision3.63新建一个工程,选择器件类型为NXP(founded by Philips)系列的LPC2101,在默认工程环境的基础上做如下确认:

①在“output”选项卡中选中“Create HEX Flie”,确保产生可供下载的机器码。

②在“Target”选项卡中选择Code Generation为“ARM-Mode”,确保以ARM指令集为依据产生机器码。

③在“C/C++”和“Asm”选项卡中分别去选“EnableARM/Thumb Interworking”,确保生成的代码只包含ARM指令。[page]

3.2 Bootloader的设置

Bootloader启动一般分为两个阶段。第一阶段主要包含依赖于微处理器的体系结构硬件初始化的代码,设置堆栈并跳转到第二阶段的C程序入口点,通常采用汇编语言来实现。第二阶段通常用C语言完成,以便实现更复杂的功能,也使程序有更好的可读性和可移植性。在μVision3.63软件自带的示例工程“Hello”中,通过下面3行代码实现了两个阶段的工作交接:

由于本文讨论的微处理器只是在FreeARM7基础之上做了一些基本的扩展,微处理器的体系结构硬件单一,因此第一阶段主要是对堆栈位置和大小进行设置。对USB接口的初始化在第二阶段的C程序中进行,初始化程序如下:

4 微处理器的功能验证

在完成前面的工作之后,借助FPGA对微处理器进行了功能验证。选用Altera公司DE2开发板作为硬件逻辑的实现载体,微处理器IP核工作时钟为开发板上27 MHz晶振输入,USB控制器IP核工作时钟为27 MHz晶振倍频至48 MHz。功能验证流程如图3所示,在主机上利用μVision 3.63编写、编译验证程序后,微处理器进入下载模式接收主机对设备的代码下载,之后进入用户模式接收主机端传送的验证程序参数值,在运行代码后将执行结果返回至主机,通过与主机软件模拟结果比较达到验证微处理器运行结果的目的。

[page]

4.1 验证程序开发

数据加密标准(DES)是著名的对称密钥分组密码,它由美国标准FIPS 46-2定义。基于ARM7指令系统,DES的C语言实现难度不大,但它是对IP核工作能力的一次综合检验。将DES算法分解为密钥生成算法和加解密算法,对应验证程序中两个子函数,其最终的代码实现框架如下:

4.2 主机驱动与通信软件开发

Windows驱动程序模型(Windows Driver Model,WDM)旨在提供一种灵活的方式来简化各种驱动程序的开发,实现对新硬件的支持,降低驱动程序开发的复杂度。基于WDM采用Driver Studio开发USB驱动程序,会自动生成一个驱动程序框架,在此基础上添加读写管道即可完成驱动程序的开发。

USB通信软件采用MFC编写,主要功能有:将.hex文件以十六进制的形式发送至USB接收USB返回的数据,并以十六进制的形式显示。采用DES程序标准测试向量,其中初始密钥K=1A624(289520DEC46,明文P=748502CD38451097,密文C=DDOCFEB783CF3FDE,在通信软件中代码下载及验证数据的收发如图4所示。按照上述原理,还编写了其他若干验证程序并下载至ROM中,微控制器的执行结果均正确。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多