第一章 绪论

1.1 单片机基础

全称:单片微型计算机(Single Chip MicroComputer)

它是把MPU、存储器、I/O口、定时器/计数器、中断系统、时钟电路、A/D-D/A等集成在一个芯片上构成的微型计算机系统。

单片机又称:单片微控制器、嵌入式微控制器

1.2 MSP430F663x片内资源

MSP430F663x 系列配置有一个高性能12 位ADC、比较器、两个USCI、USB2.0、硬件乘法器、DMA、四个16 位定时器、带有报警功能的RTC、LCD 驱动器和多达74 个I/O 。

1.3 进制转换

【注意】小数的进制转换

1.4 原码、反码、补码的书写

【注意】一般是8位补码,有时也有16位补码

1.5 位操作

P1OUT|=BIT1; //P1.1置1

P1OUT|=BIT0+BIT2+BIT6+BIT7; //P1.0、 P1.2、 P1.6、 P1.7置1

P1OUT&=~BIT7; //P1.7清0

P1OUT&=~(BIT1+BIT3); //P1.3、 P1.1清0

P1OUT^=BIT0; //P1.0取反

P1OUT^= BIT0+BIT2+BIT4+BIT6; //P1.0、 P1.2、 P1.4、 P1.6取反

MSP430的C编译器不支持位寻址,所以运算中尽量减少位操作。

第2章 硬件结构

2.1 MSP430 CPU 与 MSP430X CPU

MSP430 CPU是指MSP430F1xx系列采用的16 位CPU,数据总线宽度16位,地址总线宽度16位,寄存器16位。寻址空间216=64KB。

MSP430X CPU(简称CPUX)是指MSP430F2xx/4xx/5xx/6xx系列采用的CPU,数据总线宽度16位,地址总线宽度20位,寄存器20位。寻址空间220=1MB。CPUX的算术逻辑单元(ALU)也可以完成20位的计算。

CPUX向下兼容MSP430 CPU。

2.2 PC、SP、SR

PC:

取完指令后CPU根据该指令的字节数自动增量PC,因此20位的PC(R0)的值总是指向下一条要执行的指令。PC总是指向偶地址(bit0=0)。

SP:

20位的堆栈指针,始终指向偶地址

【作用】:保护现场和恢复现场。

先进后出

堆栈分两种:

(1)向上增长,栈底占用较低地址,栈顶占用较高地址:8051

(2)向下增长,栈底占用较高地址,栈顶占用较低地址:MSP430、AVR

(3)ARM支持两种增长方式的堆栈。

SR:

用作源或目标寄存器的16位状态寄存器(SR,也称为R2)只能用于通过字指令寻址的寄存器模式。 寻址模式的其余组合用于支持常数发生器。

SCG1:系统时钟发生器1该位可用于根据器件系列启用或禁用时钟系统中的功能; 例如,DCO偏置启用或禁用。

SCG0:系统时钟发生器0该位可用于根据器件系列启用或禁用时钟系统中的功能; 例如,FLL(频率锁定环)启用或禁用。

OSCOFF:关闭振荡器。 该位置1时,当LFXT1 CLK不用于MCLK或SMCLK时,它会关闭LFXT1晶体振荡器。

CPUOFF:CPU关闭。 该位置1时,将关闭CPU。

CPUOFF,OSCOFF,SCGO和SCG1位请求系统进入低功耗模式。

【例如】:关闭和打开锁频环(FLL)

__bis_SR_register(SCG0); // Disable the FLL control loop

UCSCTL0 = 0x0000; // Set lowest possible DCOx, MODx

UCSCTL1 = DCORSEL_3; // Set RSELx for DCO = 4.9 MHz

UCSCTL2 = FLLD_1 + 74; // Set DCO Multiplier for 2.45MHz

// (FLL_N + 1) * FLLRef = FdcoCLKDIV

// (74 + 1) * 32768 = 2.45MHz

// Set FLL Div = fDCOCLK/2

__bic_SR_register(SCG0); // Enable the FLL control loop

//其中__bis_SR_register()函数是将SR寄存器中的相应位置1

//__bic_SR_register()函数是将SR寄存器中的相应位置0

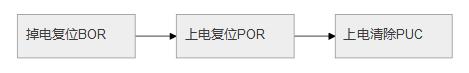

2.3 三种系统复位

2.4 复位状态

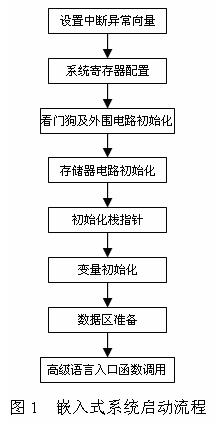

在BOR之后,初始设备条件是:

RST / NMI引脚配置为复位模式。

I / O引脚切换到输入模式。

状态寄存器(SR)复位。

看门狗定时器在看门狗模式下上电。

第3章 中断、时钟与低功耗

3.1 中断

3.1.1 各种中断向量

【注意】排序顺序为实验顺序,不代表优先级大小

中断向量的计算

3.1.2 中断优先级

不同中断源发出的中断请求重要程度不同,每个中断源对应一个优先级,称为中断优先级。

【作用】:多个中断同时发生时,决定哪个中断被响应。

【注意】:

中断优先级只有在多个中断同时到来时才起作用,在中断嵌套中是不考虑的

中断优先级固定不变,取决于模块在中断向量表中的排序

3.1.3 中断嵌套

CPU响应某一中断时,在开总中断的前提下若有其他中断发生,CPU将中断当前ISR,执行新的ISR。

MSP430默认关闭中断嵌套,即进入中断服务函数后,默认关闭总中断。如果想要开启中断嵌套需要用户使用软件开启总中断。

开启和关闭总中断例程中最常用的方式是

__bis_SR_register(GIE); // 开启总中断

__bic_SR_register(GIE); // 关闭总中断

//其中__bis_SR_register()函数是将SR寄存器中的相应位置1

//__bic_SR_register()函数是将SR寄存器中的相应位置0

3.1.4 中断服务函数

如果是多元中断,可能会在终端服务函数中查看是那种中断置位,即用if或switch语句判断中断标志位是否为1.例如:

// Timer_A1 Interrupt Vector (TAIV) handler

#pragma vector=TIMER0_A1_VECTOR

__interrupt void TIMER0_A1_ISR(void)

{

switch(__even_in_range(TA0IV,14))// __even_in_range()本征函数,用于多源中断的查询。

{

case 0: break; // No interrupt

case 2: break; // CCR1 not used

case 4: break; // CCR2 not used

case 6: break; // reserved

case 8: break; // reserved

case 10: break; // reserved

case 12: break; // reserved

case 14: P4OUT ^= BIT1; // TAIFG

break;

default: break;

}

}

3.2 UCS时钟系统

3.2.1 五种时钟源和三种时钟信号

【注】DCOCLKDIV时钟为DCOCLK分频得到

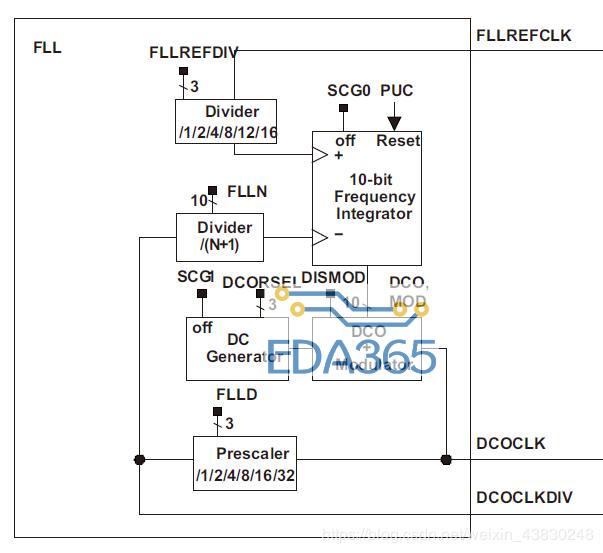

3.2.2 FLL——锁频环

计算公式:fDCOCLK ÷[D × (N + 1) ] = fFLLREFCLK ÷ n

【注释】:

D:FLLD,默认为2

N:FLLN,默认为31

n:FLLREFDIV, 默认为1

fFLLREFCLK :FLL的参考时钟,默认为XT1CLK(32768Hz)

所以fDCOCLK 默认为2097152Hz,fDCOCLKDIV默认为1048576Hz

3.2.3 UCS复位之后

由于复位的时候XT1CLK未稳定,所以ACLK和FLL的参考时钟会自动变为REFOCLK(注意这里是REFOCLK,和后边WDT看门狗模式下的时钟故障保护功能,自动变成VLOCLK相区别)

根据实验情况,如果在配置ACLK和FLL之前,XT1CLK未稳定,那么时钟频率会相对变低

//稳定XT1CLK和XT2CLK的程序

//1. 解锁XT1的引脚,这是f66xx设备独有的

while(BAKCTL & LOCKBAK)// Unlock XT1 pins

{

BAKCTL &= ~(LOCKBAK);

}

//2. 设置XT2的引脚

P7SEL |= BIT2 + BIT3; // Port select XT2

//3. 开启XT1, XT2

UCSCTL6 &= ~(XT1OFF + XT2OFF); // Set XT1, XT2 On

//4. 稳定XT1CLK、XT2CLK、DCOCLK

do

{

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + DCOFFG); // Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while (SFRIFG1&OFIFG); // Test oscillator fault flag

//5. ACLK选择XT1CLK、SMCLK选择XT2CLK

UCSCTL4 |= SELA__XT1CLK + SELS__XT2CLK; // Select SMCLK, ACLK source

3.2.4 设置DCOCLK输出的频率范围

使用UCSCTL1寄存器中的DCORSEL位来设置范围

不用看UCSCTL0寄存器中的DCO和MOD位,单片机会自动设置

尽可能让输出的频率在DCORSEL控制的范围的中间位置

3.2.5 UCS模块失效安全操作

任何一种失效都会导致OFIFG(振荡器失效中断、非屏蔽)

受到OFIE使能位控制

振荡器关闭、打开但未正常工作时,对应振荡器失效位XT1 LFOFFG,XT1 HFOFFG, XT2OFFG置位;

振荡器失效位一旦置位必须用户软件清除;

若用户软件清除振荡器失效位后失效条件依然存在,振荡器失效位会自动置位。

振荡器失效事件不受GIE控制。

3.3 低功耗

最常用的开启低功耗的方式

__bis_SR_register(LPM3_bits);//开启低功耗模式3

__bic_SR_register(LPM3_bits);//关闭低功耗模式3

//也可以这样:

LPM3;//开启

LPM3_EXIT;//关闭

第四章 数字I/O模块

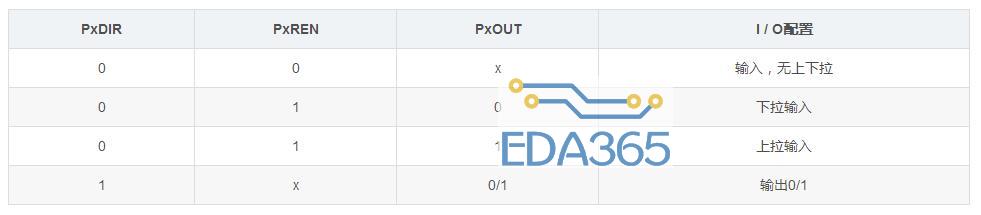

4.1 数字I/O模块寄存器设置

关于PxDIR,PxREN和PxOUT在正确I / O配置中的用法

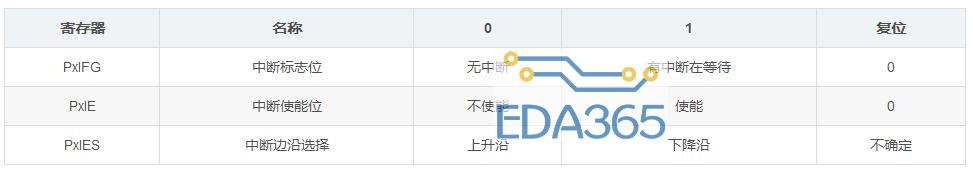

对于P1,P2引脚而言,具有中断能力,利用PxIFG, PxIE,和PxIES 寄存器进行配置。

4.2 按键

4.2.1 关于上下拉

对于按键必须要有上下拉,因为要有默认的输入值,不能让输入值处于浮空状态

可以选择内部的上下拉和外部的上下拉

MSP430F6638具有内部上下拉,所以不一定必须使用外部上下拉

4.2.2 按键消抖

软件消抖:在首次检测到按键按下后,先执行一段延时子程序,然后再次确认按键是否按下,达到消抖目的。

硬件消抖:常用双稳态电路、单稳态电路和RC积分电路等方法。

4.3 额外的东西

对于在中断服务函数中手动清零中断标志位IFG,其实有一种更方便的方法老师没讲——PxIV,这个东西会在后边讲Timer_A中看到类似的寄存器——TAxIV

读/写这个寄存器都会使得正在等待处理的最高中断标志位清零

如果有多个中断同时到来,那么处理完最高中断后会从新开启一个中断。

第5章 看门狗WDT_A

5.1 看门狗概述

5.1.1 看门狗的作用

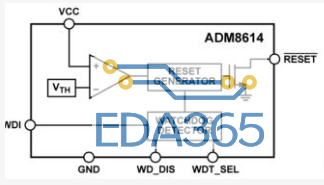

看门狗(Watchdog Timer-WDT)分硬件看门狗和软件看门狗,用于程序跑飞时的系统复位。

5.1.2 程序跑飞

程序跑飞不是一种硬件故障,但它会引起死机。

5.1.3 看门狗是什么

简单的说是一个定时器,从程序开始运行的时候就开始计数,当计数满的时候就会使程序复位。所以要在计满之前让看门狗定时器的数值清零,俗称喂狗。如果在计满之前看门狗没有收到喂狗信号,则认为程序已经跑飞。

5.1.4 看门狗的两种功能

分别是看门狗模式和间隔定时器模式

这两种模式使用不同的中断向量,但是都是单源中断(所以中断标志位WDTIFG可以自动清零)

看门狗模式的中断是系统中断

间隔定时器的中断是可屏蔽中断

看门狗和间隔定时器使用相同的中断标志位:WDTIFG

这两种模式不能同时使用

看门狗模式具有时钟故障保护功能,但是间隔定时器模式没有

5.2 看门狗的默认复位时间

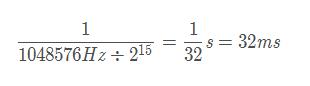

WDTIS默认为4h,其时钟信号默认为SMCLK,而SMCLK的时钟源默认为DCOCLKDIV,DCOCLKDIV的频率默认为1048576Hz,所以时间间隔默认为

5.3 时钟故障保护

为保证WDT在看门狗模式下能工作,如

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多