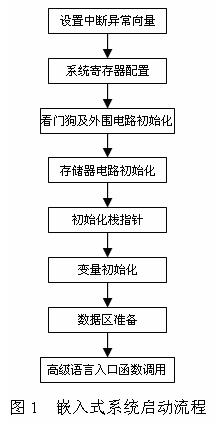

我想,很多的朋友包括一些刚入门,或者是刚从事嵌入式开发的工程师,都会对内存这一块不知所措吧,先抛开信号完整性不说,单从内存的原理以及与主芯片的连接,就已经大伤脑筋了,而很多朋友虽然已经开发出了可以使用的硬件电路板,但大多数的人都是因为有了开发板的参考而所以成功。那如果现在没有了开发板,或者设计要求与你开发板的内存容易配置不一样,那你应该如何下手呢?今天我将把自己根据2410的芯片手册以及内存的芯片手册而完成器件的原理与分析方法,分享给大家,希望如果有不对的地方可以提出,本例中将以S3C2410为主芯片,8Mbyte内存为设计方案,(注:本设计我已认证)

S3C2410,其“存储控制器”提供了访问外围设备所需的信号,它有如下特性:

●支持小字节、大字节序(通过软件选择);

●每个bank的地址空间为128MB,总共1GB(8banks);

●可编程控制的总线位宽(8/16/32-bit),不过bank0只能选择两种位宽(16/32-bit);

●总共8个bank,bank0~bank5可以支持外接ROM、SRAM等,bank6~bank7除可以支持ROM、SRAM外还支持SDRAM等;

●bank0~bank6共7个bank的起始地址是固定的;

●bank7的起始地址可编程选择;

●bank6、bank7的地址空间大小是可编程控制的;

●每个bank的访问周期均可编程控制;

●可以通过外部的“wait”信号延长总线的访问周期;

●在外接SDRAM时,支持自刷新和省电模式;

对于本系统而言,无论出于成本或是RAM占用的面积而言使用SRAM都是不划算的。SRAM一般用于小系统中,SRAM常用于快速存储的较低容量的RAM需求,比如Cache(缓存)。另外本系统需只要带动linux内核,和一些数据库的存取,需要占用内存不是很大,如果用SRAM的话不仅面积占用很大,将近4倍于SDRAM。而且价格将近于SDRAM的8倍左右,显然是不合理的。SDRAM具有高速、大容量等优点,是一种具有同步接口的高速动态随机存储器。它的同步接口和内部流水线结构允许存储外部高速数据,数据传输速度可以和ARM的时钟频率同步,在ARM系统中主要用作程序的运行空间、数据及堆栈区。从成本上考虑,它SRAM便宜很多,根据设计的性价比,可采用SDRAM作为高速缓存,实现高速数据传输。

本系统中用SDRAM时有一个重要的因素需要仔细考虑,然后选择SDRAM的大小。一般来说,移植到开发板上的linux内核是一个镜像文件,本系统的镜像文件不超过1.5M,在运行内核的时候将此镜像文件复制到内存并解压,解压后大小后超过2M,假如把数据段等都考虑进去,那么运行内核需要占用内存3M多,这里保守估计到4M,而一般的代码都在100K以加,加上数据库的内容,不会超过10M,所以选用16M内存比较划算。

根据上面CPU的特性说明,得知在bank6和bank7上可以连接SDRAM,每个bank最大可以连接128M,另外可以连接16M或更小。对于16M来说,可以满足系统内存占用的要求,32M以上虽然性能会更好,但是由于内存有大量的存储空间不被使用,所以从成本上考虑,会不划算。

在设计的时候还需要考虑位宽的问题,对于本系统使用的CPU核为ARM9,总线位宽最大为32bit,这里选择最大的总线位宽来保证总线每次数据传输率最大。SDRAM的最高位宽为16bit,因此如果要达到总线位宽32bit的话,可以用两片16bit位宽的SDRAM并联得到。那么此时每片SDRAM的大小可以为4banks*1M*16bit。

根据上面的分析,这里选用SDRAM芯片型号为HY57V641620ESTP-H。该系列的SDRAM是67,108,864位CMOS同步DRAM,适用于大存储和高带宽的存储器的选择。该芯片的内部存储结构是4banks×1M×16bits,HY57V641620ESTP-H系列是完全同步操作提供参照的时钟上升沿。 所有输入和输出 是同步的时钟输入的上升沿。数据路径内部管线 , 实现非常高的带宽。所有输入和输出电压电平兼容LVTTL接口。其特征是:

●3.3 ± 0.3V单电源;

●所有器件引脚兼容LVTTL接口;

●所有的输入和输出参照系统时钟的上升沿;

●自动刷新和自刷新,每64ms自刷新一遍;

●可编程CAS延迟,2,3个时钟

该SDRAM系列根据不同的最高频率,提供了几种型号选择,本系统选用最高频率为133MHZ的HY57V641620ESTP-H型号。SDRAM的频率由锁相环MPLL经过分频所得到的HCLK总线频率提供SDRAM的时钟频率,这里选择100MHZ主要为了分频方便而选择。

该芯片具有54个引脚,封装为TSOP,其引脚描述如下:

CLK:时钟引脚,用于系统时钟的输入,所有的输入在系统时钟的上升沿向SDRAM注册。

CKE:时钟使能引脚,控制内部的时钟信号。

/CS:片选引脚,使能或禁止所有除CLK、CKE、UDQM、LDQM的输入。

BA0、BA1:bank地址引脚。

A0~A12:地址线引脚,行地址:RA0 RA12,列地址:CA0 CA8。

/RAS、/CAS、/WE:行地址选通,列地址选通,写使能引脚。

UDQM、LDQM:数据输入输出屏蔽引脚。

DQ0~DQ15:数据输入输出引脚。

VDD/VSS:电源/接地引脚,为内部电路和输入缓冲供电。

VDDQ/VSSQ:数据输出电源/地引脚,为输出缓冲供电。

NC:未连接。

电气性能如表1表示:

表1:DC下的电气性能

从规格书中可以看到其输入的电源电压典型值为3.3V,和CPU输出电压一致。输入的高电平电压最小为2.0V,符合CMOS中高电平输出电压最小为3.3-0.05V。输入的低电平电压最大为0.8V,符合CMOS中低电平输出电压最大为0.05V。

本系统通过8根片选信号的配置将SDRAM连接在BANK6上,根据S3C2440手册描述该BANK6的起始地址为0x30000000,本系统配置的SDRAM访问空间为16M大小,那么结束地址为0x30ffffff。BANK6连接SDRAM比较复杂,CPU提供了一组用于SDRAM的信号:

说明如下:

●SDRAM时钟有效信号SCKE;

●SDRAM时钟信号SCLK0/SCLK1;

●数据掩码信号DQM0/DQM1/DQM2/DQM3;

●SDRAM片选信号nSCS0(它与nGCS6是同一引脚的两个功能);

●SDRAM行地址选通脉冲信号nSRAS;

●SDRAM列脉冲信号nSCAS;

●写允许信号nWE(它不是专用于SDRAM的)。

地址线和数据线的连接:

地址线的连接相对来说比较复杂,需要对SDRAM芯片的规格书仔细和S3C2440手册对存储控制器的描述很好的理解。这里首先对本系统中所用的SDRAM芯片的内部结构进行阐述。SDRAM芯片选用的是HY57V641620ESTP-H型号,内部具有4个bank,每个bank是1M,每个存储单元为16位数据。其内部结构如图1-2-1所示:

从其内部结构我们也可以看出,该芯片对外提供了14根地址总线。其中BA0和BA1用于选择片选4个bank。每个bank的1M大小的存储空间则由A0~A11控制。每个bank的内部是一个存储阵列,阵列就如同表格一样,将数据“填”进去。和表格的检索原理一样,先指定一个行(row),再指定一个列(column),就可以准确地找到所需要的单元格,这也是SDRAM的寻址原理。对于该bank,其内部的每个存储单元,如同上面所说的分别由行和列地址总线来控制。在该芯片的规格书的引脚说明中,如表1-2-2所示,行使用RA0~RA11共12根地址线,列使用RA0~RA7共8根数据线。而这样的行列方式组成了一个BANK的1M寻址空间(2^12*2^8=2^20,为1M空间)。而每一个空间中存的数据长度为16bit。

图1:HY57V641620ESTP-H内部结构

表1-2-2:内存引脚功能表

对于具体的地址线和数据线的连接需要根据手册来正确连接。根据S3C2410手册,可得到双SDRAM的连接方法,具体如表3和表4所示:

表3:不同数据位宽度地址线连接方法

表4:16MB内存连接方法

本系统选择的bank大小配置为16M,总线带宽为32bit,芯片的bank数量为4块,对应表中存储配置的(1M*16*4BANKS)*2ea,根据表中的bank address是连接到A23、A22。该bank address是用了两个地址总线来选择4个bank,对应芯片引脚中的BA0和BA1。因此,根据上面所说,A22连接两片芯片的BA0引脚,A23连接两片芯片的BA1引脚。

其余信号引脚的连接:

nSCS为SDRAM芯片的片选信号,而在S3C2440该CPU中提供了片选信号nSCS0,该引脚和nGCS6是同一个引脚的两个功能。当该信号有效时,选中SDRAM芯片。

SCKE、SCLK0、SCLK1 3个引脚分别是两片RAM芯片的时钟有效信号和两个时钟信号。在CPU端,也相应提供对应的3个引脚,依次相连即可。SCLK0代表的是低16位芯片的时钟引脚,SCLK1代表的是高16位芯片的时钟引脚。

nWE芯片引脚为写使能信号,在CPU端引脚提供了一个不是专用于SDRAM的写允许信号引脚nWE,将此引脚分别用于芯片的写使能,同时控制两片芯片的写使能与否。LDQM、UDQM 两个SDRAM芯片引脚分别为写使能和数据掩码信号引脚,用于在读模式下控制输出缓冲,在写模式下屏蔽输入数据。前面所讲的CPU所提供给SDRAM信号中有4个数据掩码信号DQM0/ DQM1/ DQM2/ DQM3,将低16位芯片的LDQM、UDQM引脚和DQM0、DQM1相连,将高16位芯片的LDQM、UDQM引脚和DQM2、DQM3相连。

芯片手册上关于电源部分描述如下

根据上表,VDD和VDDQ电源信号需要连接3.3V,引脚说明中VSS和VSSQ信号需要接地。

根据上面所述,电路图连接如图2所示:

图2:sdram连接方法

SC32410的SDRAM接口时序图如图3所示:

图3:S3C2410 SDRAM时序图

影响SDRAM性能的主要时序参数有3个,分别是tRCD、CL和tRP。以内存最主要的操作——读取为例。tRCD决定了行寻址(有效)至列寻址(读/写命令)之间的间隔,CL决定了列寻址到数据进行真正被读取所花费的时间,tRP则决定了相同L-Bank中不同工作行转换的速度。相关参数的值我们可以从SDRAM的规格书中得到:

HY57V641620ESTP-H的结构为1M*4Bank*16bit,如图4所示:

图4:HY57V641620ESTP-H中1个BANK的结构

至此,s3c2410对内存的操作,时序的产生,以及最后对应到具体操作的哪个内容空间,比较系统的了解了。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多