一. NVIC和系统控制块特性

1. 灵活的中断管理:使能/禁止中断,优先级配置 2. 硬件嵌套中断支持 3. 向量化的异常入口 4. 中断屏蔽 5. NVIC寄存器的起始地址:0xE000E100, 对其访问必须是每次32bit 6. SCB的起始地址: 0xE000E010,也是每次32bit访问。1234567

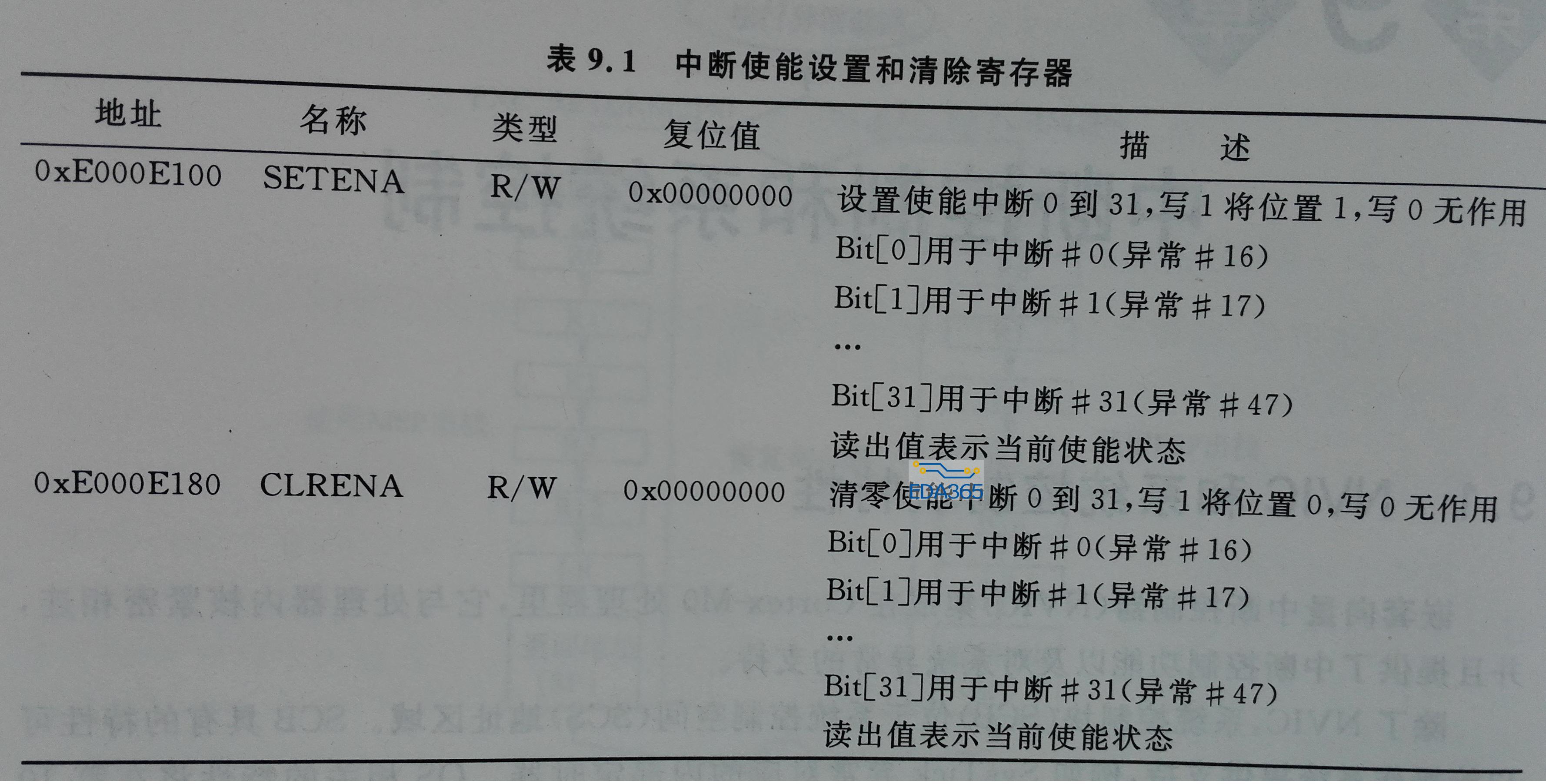

二. 中断使能和清除使能

1. 中断寄存器是可编程的,用于控制中断请求(异常编号16以上)的使能(SETENA)和禁止(CLRENA), 如下所示:12

2. 使能/禁止 中断的代码: 1). C代码:123

*(volatile unsigned long) (0xE000E100) = 0x4 ; //使能#2中断 *(volatile unsigned long) (0xE000E180) = 0x4 ; //禁止#2中断12

2). 汇编代码:12

LDR R0, =0xE000E100 ; //SETEAN寄存器的地址 MOVS R1, #04 ; //设置#2中断 STR R1, [R0] ; //使能中断#2123

3). CMSIS标准设备驱动函数: 12

void NVIC_EnableIRQ(IRQn_Type_IRQn); //使能中断#IRQn; void NVIC_DisableIRQ(IRQn_Type_IRQn); //禁止中断#IRQn;12

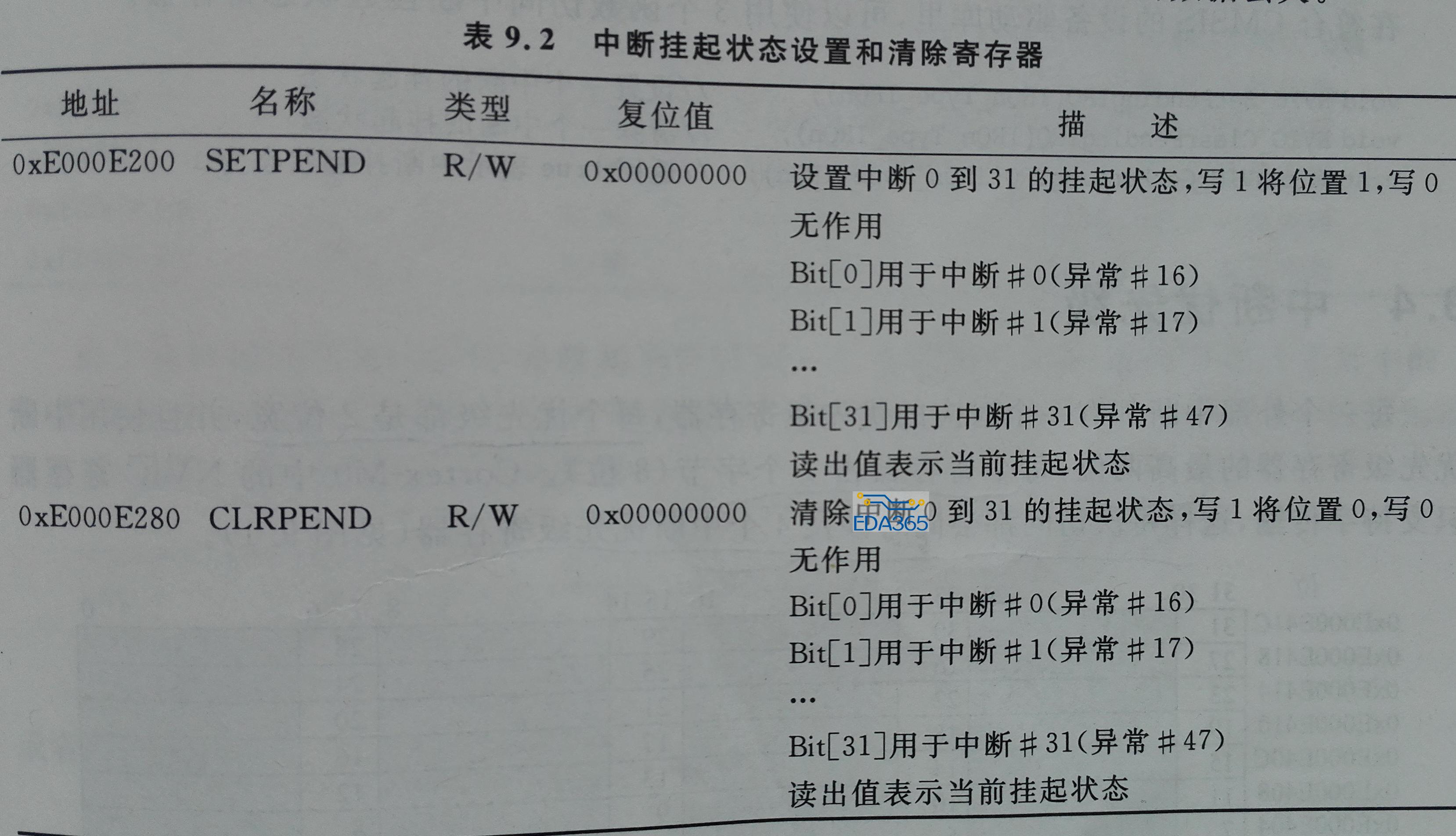

三. 中断挂起和清除挂起:

1. 可以通过操作中断挂起(SETPEND)和清除挂起(CLRPEND),这两个寄存器来访问和修改中断挂起状态。12

2.挂起/清除挂起的代码: 1). C代码:123

*(volatile unsigned long)(0xE000E100) = 0x4 ; //使能中断#2 *(volatile unsigned long)(0xE000E200) = 0x4 ; // 挂起中断#2 *(volatile unsigned long)(0xE000E280) = 0x4 ; // 清除中断#2的挂起状态123

2). 汇编代码:12

LDR R0, =0xE000E100 ; //设置使能中断寄存器地址 MOVS R1, #0x4 ; //中断#2 STR R1, [R0] ; //使能#2中断 LDR R0, =0xE000E200 ; //设置挂起中断寄存器地址 MOVS R1, #0x4 ; //中断#2 STR R1, [R0] ; //挂起#2中断 LDR R0, =0xE000E280 ; //设置清除中断挂起寄存器地址 MOVS R1, #0x4 ; //中断#2 STR R1, [R0] ; //清除#2的挂起状态123456789

3). CMSIS标准设备驱动函数: 12

void NVIC_SetPendingIRQ(IRQn_Type_IRQn) ; //设置一个中断挂起 void NVIC_ClearPendingIRQ(IRQn_Type_IRQn); //清除中断挂起 void NVIC_GetPendingIRQ(IRQn_Type_IRQn) ; //读取中断挂起状态123

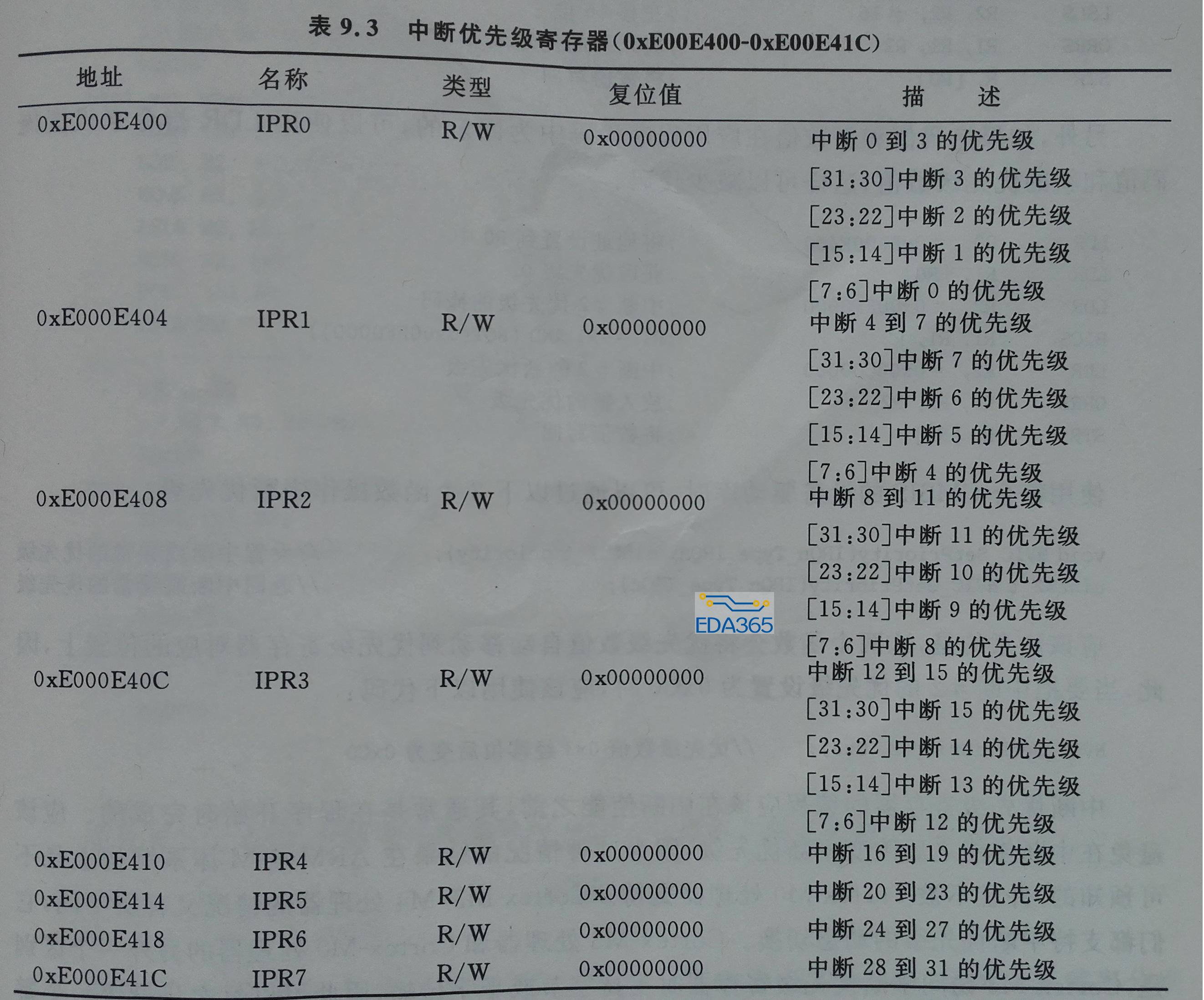

四. 中断优先级:(0xE000E400~0xE000E41C)

1. 每个外部中断都有一个对应的中断有先级寄存器,每个优先级都是只有一个字节且只有最高2Bit有效; 2. NVIC支持字传输,所以每次访问都会涉及4个中断优先级寄存器。123

3. 设置中断优先级代码:(先读一个字,再修改对应字节,最后整个字写回) 1). C代码:1234

unsigned long temp; //定义一个临时变量 temp = *(volatile unsigned long)(0xE000E400); //读取IRP0值 temp &= (0xFF00FFFF |(0xC0 <2). 汇编代码:12LDR R0, =0xE000E100 ; //设置使能中断寄存器地址 MOVS R1, #0x4 ; //中断#2 STR R1, [R0] ; //使能#2中断 LDR R0, =0xE000E200 ; //设置挂起中断寄存器地址 MOVS R1, #0x4 ; //中断#2 STR R1, [R0] ; //挂起#2中断 LDR R0, =0xE000E280 ; //设置清除中断挂起寄存器地址 MOVS R1, #0x4 ; //中断#2 STR R1, [R0] ; //清除#2的挂起状态1234567893). CMSIS标准设备驱动函数: 12void NVIC_SetPriority(IRQn_Type_IRQn, uint32_t priority) ; //设置中断优先级 uint32_t NVIC_GetPriority(IRQn_Type_IRQn); //读取中断优先级 这里的priority是0,1,2,3.函数内部会自动移位到对应的优先级最高2位: void NVIC_SetPriority(2, 3) ; //设置#2中断的优先级为0xC012345五. 异常屏蔽寄存器(PRIMASK)

1.对时间敏感的应用,需要用PRIMASK来屏蔽掉除NMI和硬件错误异常以外的其他所有中断和异常。 2.PRIMASK只有1Bit有效,默认为0,为1时起屏蔽作用。 3.操作PRIMASK的代码: 1). 汇编代码:12345MOVS R0, #1 ; MSR PRIMASK, R0 ; //使用MSR指令设置PRIMASK值122). CPS指令:12CPSIE i ; //清除PRIMASK值 CPSID i ; //设置PRIMASK值123). CMSIS标准设备驱动函数:12void _enable_irq(void) ; //清除PRIMASK值 void _disable_irq(void) ; //设置PRIMASK值12六. 中断输入和挂起行为

1. Cortex-M0允许电平触发和脉冲触发两种方式; 2. 每个外部中断请求都会对应一个挂起状态寄存器,且只有1bit,当开始处理这个异常时,硬件会自动清除挂起状态; 3. 大多数外设都是使用电平触发,当执行中断服务程序并且清除外设中断信号之前,该信号一直为高:1234

4. 使用脉冲触发中断时,至少持续1个时钟周期:12

七. 中断等待 (中断确认 –> 中断服务处理开始执行)

1. Cortex-M0中断默认等待的时间为16个时钟周期; 2. 中断等待的条件: 1). 改中断使能并且没有被PRIMASK屏蔽掉; 2). 存储器系统没有任何等待。 3. IRQLATENCY的8位信号可以控制中断等待:设置为0,则以最快速度响应中断。1234567八. 系统异常的控制寄存器(SHPR2,SHPR3)

1. Cortex-M0处理器只有SVC、PendSV和SysTick 3个与OS相关的系统异常才具有可编程的 优先级123. 中断控制状态寄存器(ICSR, 0xE000ED04): P139, 表9.6 4. 符合CMSIS的设备驱动,可使用 "SCB -> ICRS" 来访问。1234九. 系统控制寄存器(0xE000E000~0xE000EFFF)

1. SCS包括NVIC、调试控制、SysTick定时器; 2. CPU ID基址寄存器(0xE000ED00),只读,包含处理器ID信息,"SCB -> CPUID" 访问; 3. 应用中断和复位控制寄存器(AIRCR, 0xE000ED0C): 1). 用于应用程序请求系统复位,识别系统的大小端,以及清除所有的异常活动状态:12345

2). CMSIS 设备驱动,可以使用 "SCB -> AIRCR" 来访问; 3). CMSIS 设备驱动, 请求系统复位的函数:123Void NVIC_SystemReset(void);1十. 配置和控制寄存器(CCR, 0xE000ED14)

1. CCR 只读, 决定了栈的双字节对齐设置和非对称访问的处理; 2. CMSIS 设备驱动,可以使用 "SCB -> CCR" 来访问;关键字:Cortex-M0 中断控制 系统控制

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多