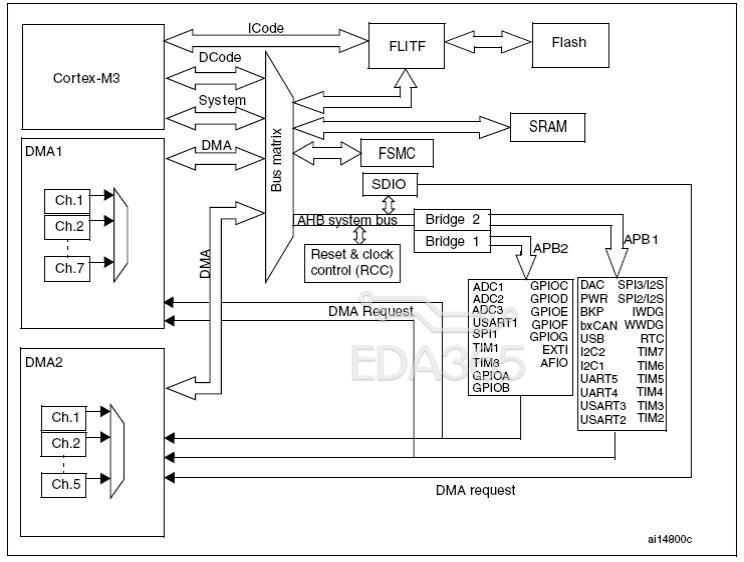

STM32系统架构如下图所示:

主系统有以下部分构成:

DCode总线

该总线将M3内核的DCode总线与闪存存储器数据接口相连

ICode总线

该总线将M3内核的ICode总线与闪存存储器指令接口相连,指令取指在该总线上完成

系统总线S-bus

此总线连接Cortex™-M3内核的系统总线(外设总线)到总线矩阵,总线矩阵协调着内核和DMA间的访问。

DMA总线 DMA1和DMA2

此总线将DMA的AHB主控接口与总线矩阵相联,总线矩阵协调着CPU的DCode和DMA到SRAM、闪存和外设的访问。

总线矩阵

此总线矩阵协调内核系统总线和DMA主控总线之间的访问仲裁。此仲裁利用轮换算法。此总线矩阵由四个驱动部件(CPU的DCode、系统总线、DMA1总线和DMA2总线)和四个被动部件(闪存存储器接口(FLITF)、SRAM、FSMC和AHB2APB桥)构成。

AHB外设通过总线矩阵与系统总线相连,允许DMA访问。

AHB/APB桥(APB)

两个AHB/APB桥在AHB和2个APB总线间提供同步连接。APB1操作速度限于36MHz,APB2操作于全速(最高72MHz)。 有关连接到每个桥的不同外设的地址映射请参考表1。在每一次复位以后,所有除SRAM和

FLITF以外的外设都被关闭,在使用一个外设之前,必须设置寄存器RCC_AHBENR来打开该外

设的时钟。

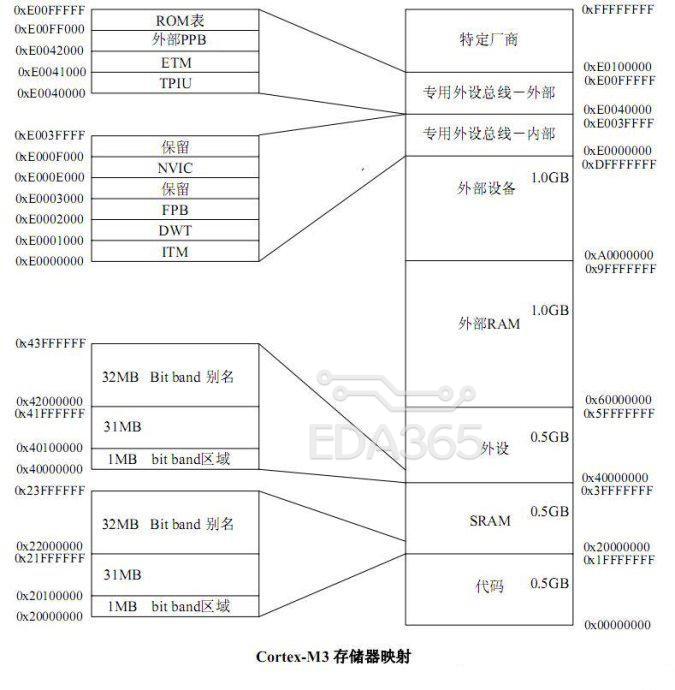

程序存储器、数据存储器、寄存器和输入输出端口被组织在同一个4GB的线性地址空间内。数据字节以小端格式存放在存储器中。一个字里的最低地址字节被认为是该字的最低有效字节,而最高地址字节是最高有效字节。

Cortex-M3是32位的内核,因此其PC指针可以指向2^32=4G的地址空间,也就0x0000_0000——0xFFFF_FFFF这一大块空间。

好,根据图中描述,Cortex-M3内核将0x0000_0000——0xFFFF_FFFF这块4G大小的空间分成8大块:代码、SRAM、外设、外部RAM、外部设备、专用外设总线-内部、专用外设总线-外部、特定厂商等。导致了,使用该内核的芯片厂家必须按照这个进行各自芯片的存储器结构设计。

这就可以去了解STM32的存储器结构,以及为什么这样设计STM32存储器的结构了。

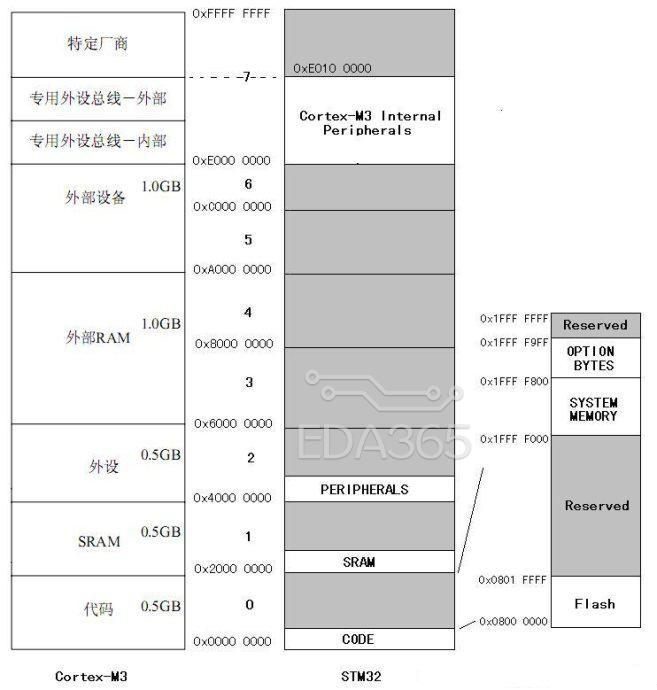

图中可以很清晰的看到,STM32的存储器结构和Cortex-M3的很相似,不同的是,STM32加入了很多实际的东西,如:Flash、SRAM等。只有加入了这些东西,才能成为一个拥有实际意义的、可以工作的处理芯片——STM32。

STM32的存储器地址空间被划分为大小相等的8块区域,每块区域大小为512MB。

对STM32存储器知识的掌握,实际上就是对Flash和SRAM这两个区域知识的掌握。因此,下面将重点描述Flash和SRAM的知识。

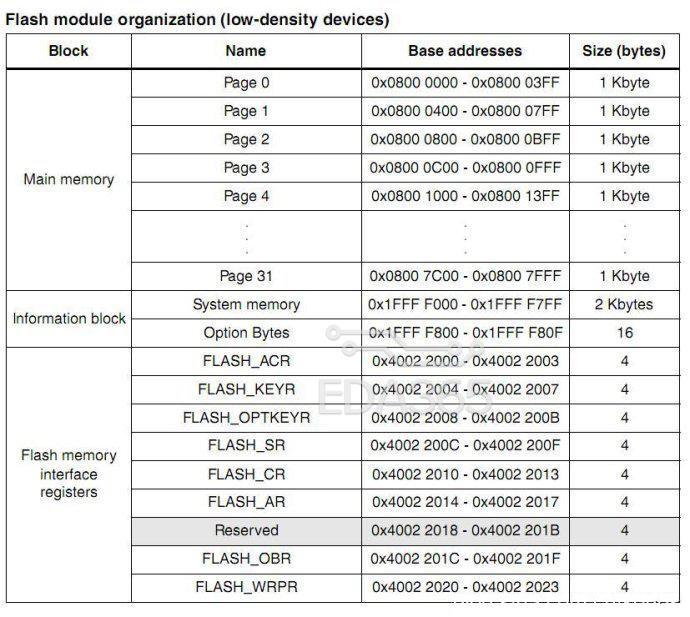

STM32的Flash,严格说,应该是Flash模块。

该Flash模块包括:Flash主存储区(Main memory)、Flash信息区(Information block),以及Flash存储接口寄存器区(Flash memory interface)。

三个组成部分分别在0x0000 0000——0xFFFF FFFF不同的区域,如图(小密度的STM32)所示:

图中淡蓝色就是你需要知道的。

Peripherals:外设的存储器映射,对该区域操作,就是对相应的外设进行操作;

SRAM:运行时临时存放代码的地方;

Flash:存放代码的地方;

System Memory:STM32出厂时自带的你只能使用,不能写或擦除;

Option Bytes:可以按照用户的需要进行配置(如配置看门狗为硬件实现还是软件实现);

今后,你的编写代码、程序运行、寄存器设置、ICP、IAP都依靠这些东西。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多