文中采用了单片DSP器件TMS32F2812,通过对轨道移频信号解调算法的研究,使设计系统具有集成度高、实时性好、抗干扰能力强和可靠性高等优点。

1 系统的整体设计

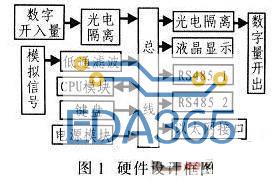

系统采用了TMS32F2812处理芯片,主频高达150 MHz,时钟周期为6.67 ns。2×8的ADC转换通道。SPI串口。两个1 kb×16 SARAM等模块,这些模块易于实现ADC的采样、主从控制芯片的数据交换和FFT变换所需要的大容量SARAM空间。

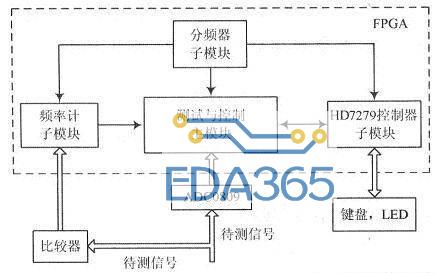

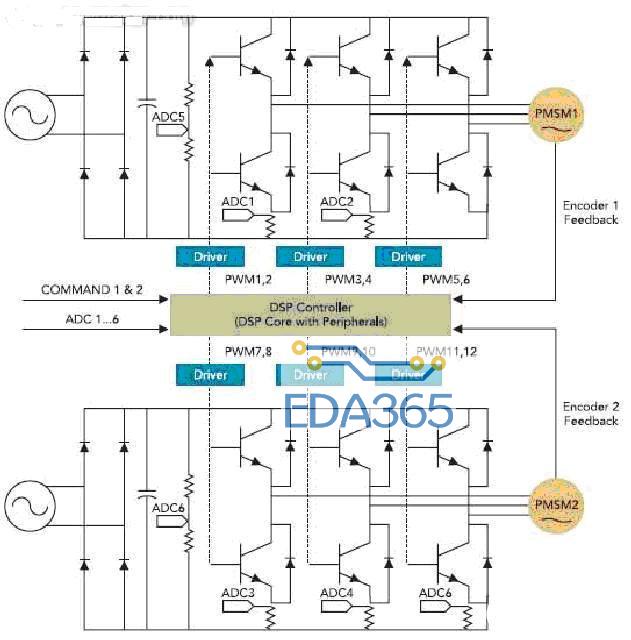

本系统总体设计如图1所示。采用双机热备,两路同时对调理后的FSK信号采样和解调,比较一致输出,这样可提高系统的可靠性。

2 主要技术实现

2.1 信号调理

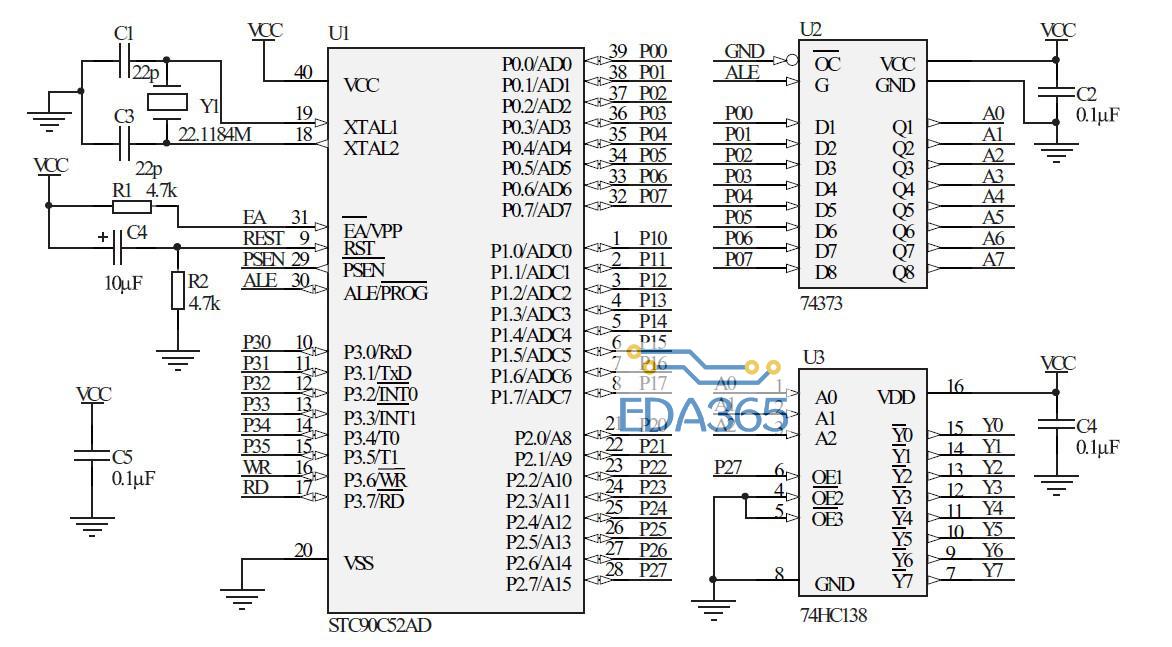

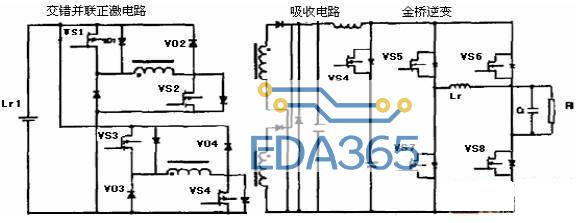

信号调理主要用低通滤波器,低通滤波器的设计使用的是MicroChip滤波器设计的软件FilterLab,该软件只需输入通带频率和滤波器的阶数,就可以生成相应的电路图,省去了滤波器设计中复杂的运算。图2所示是FilterLab软件生成的Butterworth低通滤波器,阶数为4,通带频率为4 000 Hz,图中给出了滤波器电容电阻的建议取值。

2.2 信号采样设计

由于使用了TMS320F2812的内部A/D,在实际运用中,发现内部的A/D采样误差较大,最大可达9%,这样远达不到采样精度要求,需要通过软件校正。首先选用ADC的任意两个通道作为参考输入通道,并分别输入已知的直流参考电压,通过读取相应的结果寄存器获取转换值,利用两组输出值便可求得ADC模块得校正增益和校正偏置,然后利用这两个值对其他通道转换数据进行补偿。具体的补偿公式如式(3)~式(6)所示

2.3 信号处理模块设计

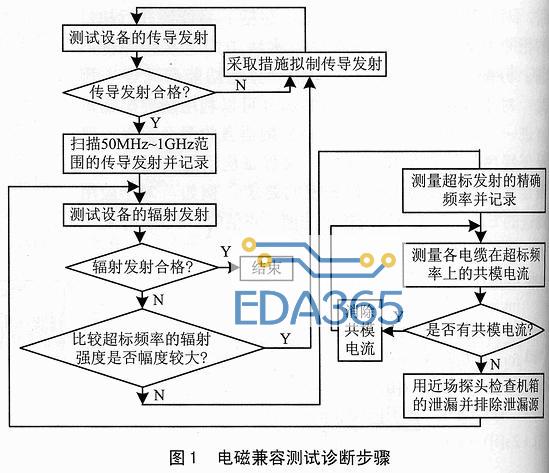

信号处理模块主要由欠采样、FFT变换和Rife频率休整等部分组成,信号处理模块的流程如图3所示,其中搬移、滤波、抽取、FFT组成了Z—EFT。

在FFT变换中使用的是TI的FFT函数库,FFT程序模块化,易于大数量FFT变换的修改,且运算速度快,执行效率高。FFT变换主要由模块初始化和FFT计算等组成。

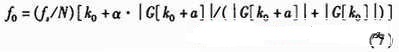

进过FFT变换后,频率主瓣中存在两个采样点,中心频率必定介于这两点之间,使用Rife频率估计法进行频谱分析可得到精确的频率估计值。Rife频率估计法,就是用频谱的绝对值的最大值G(k)进行比较,在k=[0,(N-1)/2]中求得最大值的|G(k)|,比较|G(k-1)|和|G(k+1)|大小,若|G(k-1)|<|G(k+1)|,则α=-1,否则α=1,颛谱估计值如式(9)所示,其中,fs为采样频率

3 实验数据分析

ZPW-2000A的低频和载频测量数据如表1所示。

从测量数据看,载频频率误差在0.2 Hz以内,低频频率误差在0.02 Hz以内,精度高于铁道部的相关规定。

4 结束语

对ZPW-2000A的移频键控信号解调,对载频直接进行FFT变换,测出载频频率;然后进行搬移、滤波、FFT变换和Rife频率休整,解调出低频频率,这样解调出来的频率很高,且FFT算法用的TI的算法库,运行效率较高,实时性较强。本系统采用了双机热备,提高了设备的可靠性。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多