ADI公司的ADAU1787是集成了两个数字信号处理器(DSP)的具有四个输入和两个输出的编译码器(CODEC).ADAU1787具有可编程的FastDSP音频处理引擎,高达768kHz取样速率,双二阶滤波器,限制器,音量控制和混合; ADAU1787还集成了SigmaDSP音频处理核,高达50MIPS性能,低延迟24位ADC和DAC.主要特性还具有96dB信噪比(SNR)(信号通过PGA和ADC与A加权滤波器)以及105dB组合SNR(信号通过DAC和耳机与A加权滤波器),串口fSYNC频率从8kHz到192kHz,模拟进到模拟出的群时延为5 μs (fS = 768 kHz),4个单端模拟输入,可配置麦克风或线输入,8个数字麦克风输入,2个模拟差分音频输出可配置成线输出或耳机驱动器,锁相环(PLL)支持30kHz到27MHz任何输入时钟速率,主要用在降噪手持机和耳机,蓝牙ANC手持机和耳机,个人导航设备(PND),数码相机和摄像机,音乐乐器效果处理器,多媒体扬声器系统和智能手机。本文介绍了ADAU1787主要特性,框图和系统框图以及评估板EVAL-ADAU1787Z主要特性,电路图,材料清单和PCB设计图。

The ADAU1787 is a codec with four inputs and two outputs that incorporates two digital signal processors (DSPs)。 The path from the analog input to the DSP core to the analog output is optimized for low latency and is ideal for noise cancelling headsets. With the addition of just a few passive components, the ADAU1787 provides a complete headset solution.

Note that throughout this data sheet, multifunction pins, such as BCLK_0/MP1, are referred to either by the entire pin name or by a single function of the pin, for example, BCLK_0, when only that function is relevant.

ADAU1787主要特性:

Programmable FastDSP audio processing engine

Up to 768 kHz sample rate

Biquad filters, limiters, volume controls, mixing

28-bit SigmaDSP audio processing core

Visually programmable using SigmaStudio

Up to 50 MIPS performance

Low latency, 24-bit ADCs and DACs

96 dB SNR (signal through PGA and ADC with A-weighted filter)

105 dB combined SNR (signal through DAC and headphone with A-weighted filter) Serial port fSYNC frequency from 8 kHz to 192 kHz

5 μs group delay (fS = 768 kHz) analog in to analog out with FastDSP bypass

4 single-ended analog inputs, configurable as microphone or line inputs

8 digital microphone inputs

2 analog differential audio outputs, configurable as either line output or headphone driver

PLL supporting any input clock rate from 30 kHz to 27 MHz

Full-duplex, 4-channel ASRCs

2,16-channel serial audio ports supporting I2S, left justified,or up to TDM16

8 interpolators and 8 decimators with flexible routing

Power supplies

Analog AVDD at 1.8 V typical

Digital I/O IOVDD at 1.1 V to 1.98 V

Digital DVDD at 0.9 V typical

Low power (11.027 mW for typical stereo noise cancelling solution)

I2C and SPI control interfaces, self boot from I2C EEPROM

Flexible GPIO

42-ball, 0.35 mm pitch, 2.695 mm × 2.320 mm WLCSP

ADAU1787应用:

Noise cancelling handsets, headsets, and headphones

Bluetooth ANC handsets, headsets, and headphones

Personal navigation devices

Digital still and video cameras

Musical instrument effect processors

Multimedia speaker systems

Smartphones

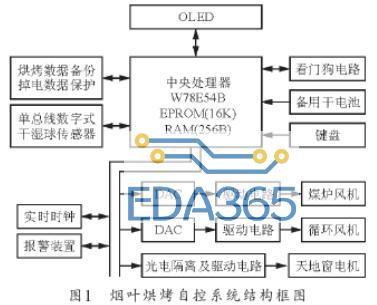

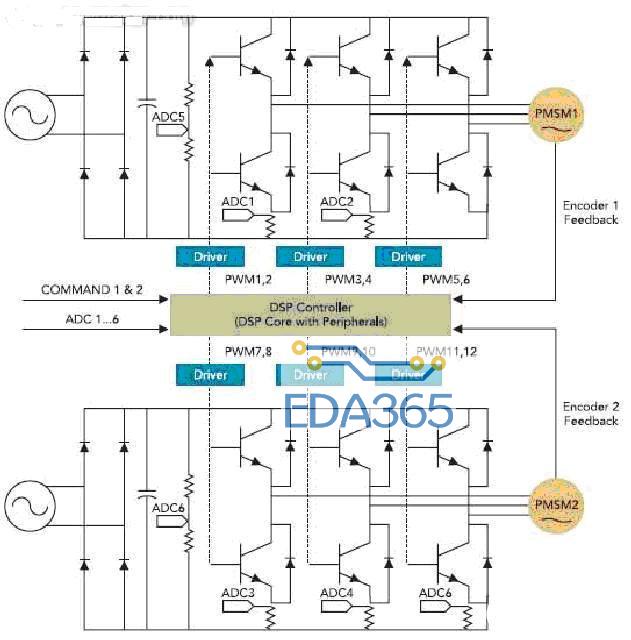

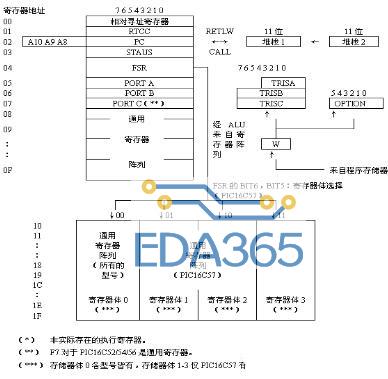

图1. ADAU1787框图

图2. ADAU1787系统框图:模拟麦克风,自举模式

评估板EVAL-ADAU1787Z

This user guide explains the design and setup of the EVAL-ADAU1787Z evaluation board. This evaluation board provides access to all analog and digital inputs/outputs on the ADAU1787. The ADAU1787 core is controlled by Analog Devices, Inc., SigmaStudio® software, which interfaces to the EVAL-ADAU1787Z via a USB connection. The EVAL-ADAU1787Z can be powered by the USB bus or by a single 3.8 V to 5 V supply. Any of these supplies are regulated to the voltages required on the EVAL-ADAU1787Z. The printed circuit board (PCB) is a 6-layer design, with a ground plane and a power plane on the inner layers. The EVAL-ADAU1787Z contains connectors for external microphones and speakers. The master clock can be provided externally or by the on-board 24.576 MHz passive crystal.

Multifunction pin names may be referenced by their relevant function only, for example, MPx, throughout this user guide.

评估板EVAL-ADAU1787Z包括:

EVAL-ADAU1787Z evaluation board

EVAL-ADUSB2EBZ (USBi) communications adapter

USB cable with mini USB plug

图3.评估板EVAL-ADAU1787Z外形图

图4.评估板EVAL-ADAU1787Z PCB跳线和开关设定图

图5.评估板EVAL-ADAU1787Z电路图(1):ADAU1787

图6.评估板EVAL-ADAU1787Z电路图(2):电源

评估板EVAL-ADAU1787Z材料清单:

图7.评估板EVAL-ADAU1787Z PCB设计图(1):顶层装配

图8.评估板EVAL-ADAU1787Z PCB设计图(2):顶层铜

图9.评估板EVAL-ADAU1787Z PCB设计图(3):地平面

图10.评估板EVAL-ADAU1787Z PCB设计图(4):电源面

图11.评估板EVAL-ADAU1787Z PCB设计图(5):层4铜

图12.评估板EVAL-ADAU1787Z PCB设计图(6):层5铜

图13.评估板EVAL-ADAU1787Z PCB设计图(7):层6底铜

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多