DSP处理器与通用处理器的比较

1 对密集的乘法运算的支持

GPP不是设计来做密集乘法任务的,即使是一些现代的GPP,也要求多个指令周期来做一次乘法。而DSP处理器使用专门的硬件来实现单周期乘法。DSP处理器还增加了累加器寄存器来处理多个乘积的和。累加器寄存器通常比其他寄存器宽,增加称为结果bits的额外bits来避免溢出。

同时,为了充分体现专门的乘法-累加硬件的好处,几乎所有的DSP的指令集都包含有显式的MAC指令。

2 存储器结构

传统上,GPP使用冯.诺依曼存储器结构。这种结构中,只有一个存储器空间通过一组总线(一个地址总线和一个数据总线)连接到处理器核。通常,做一次乘法会发生4次存储器访问,用掉至少四个指令周期。

大多数DSP采用了哈佛结构,将存储器空间划分成两个,分别存储程序和数据。它们有两组总线连接到处理器核,允许同时对它们进行访问。这种安排将处理器存贮器的带宽加倍,更重要的是同时为处理器核提供数据与指令。在这种布局下,DSP得以实现单周期的MAC指令。

还有一个问题,即现在典型的高性能GPP实际上已包含两个片内高速缓存,一个是数据,一个是指令,它们直接连接到处理器核,以加快运行时的访问速度。从物理上说,这种片内的双存储器和总线的结构几乎与哈佛结构的一样了。然而从逻辑上说,两者还是有重要的区别。

GPP使用控制逻辑来决定哪些数据和指令字存储在片内的高速缓存里,其程序员并不加以指定(也可能根本不知道)。与此相反,DSP使用多个片内存储器和多组总线来保证每个指令周期内存储器的多次访问。在使用DSP时,程序员要明确地控制哪些数据和指令要存储在片内存储器中。程序员在写程序时,必须保证处理器能够有效地使用其双总线。

此外,DSP处理器几乎都不具备数据高速缓存。这是因为DSP的典型数据是数据流。也就是说,DSP处理器对每个数据样本做计算后,就丢弃了,几乎不再重复使用。

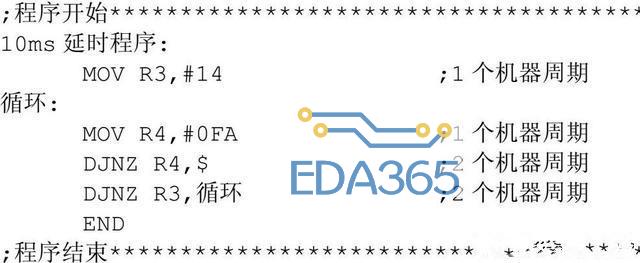

3 零开销循环

如果了解到DSP算法的一个共同的特点,即大多数的处理时间是花在执行较小的循环上,也就容易理解,为什么大多数的DSP都有专门的硬件,用于零开销循环。所谓零开销循环是指处理器在执行循环时,不用花时间去检查循环计数器的值、条件转移到循环的顶部、将循环计数器减1。

与此相反,GPP的循环使用软件来实现。某些高性能的GPP使用转移预报硬件,几乎达到与硬件支持的零开销循环同样的效果。

4 定点计算

大多数DSP使用定点计算,而不是使用浮点。虽然DSP的应用必须十分注意数字的精确,用浮点来做应该容易的多,但是对DSP来说,廉价也是非常重要的。定点机器比起相应的浮点机器来要便宜(而且更快)。为了不使用浮点机器而又保证数字的准确,DSP处理器在指令集和硬件方面都支持饱和计算、舍入和移位。

5 专门的寻址方式

DSP处理器往往都支持专门的寻址模式,它们对通常的信号处理操作和算法是很有用的。例如,模块(循环)寻址(对实现数字滤波器延时线很有用)、位倒序寻址(对FFT很有用)。这些非常专门的寻址模式在GPP中是不常使用的,只有用软件来实现。

6 执行时间的预测

大多数的DSP应用(如蜂窝电话和调制解调器)都是严格的实时应用,所有的处理必须在指定的时间内完成。这就要求程序员准确地确定每个样本需要多少处理时间,或者,至少要知道,在最坏的情况下,需要多少时间。

如果打算用低成本的GPP去完成实时信号处理的任务,执行时间的预测大概不会成为什么问题,应为低成本GPP具有相对直接的结构,比较容易预测执行时间。然而,大多数实时DSP应用所要求的处理能力是低成本GPP所不能提供的。

这时候,DSP对高性能GPP的优势在于,即便是使用了高速缓存的DSP,哪些指令会放进去也是由程序员(而不是处理器)来决定的,因此很容易判断指令是从高速缓存还是从存储器中读取。DSP一般不使用动态特性,如转移预测和推理执行等。因此,由一段给定的代码来预测所要求的执行时间是完全直截了当的。从而使程序员得以确定芯片的性能限制。

7 定点DSP指令集

定点DSP指令集是按两个目标来设计的:

使处理器能够在每个指令周期内完成多个操作,从而提高每个指令周期的计算效率。

将存贮DSP程序的存储器空间减到最小(由于存储器对整个系统的成本影响甚大,该问题在对成本敏感的DSP应用中尤为重要)。

为了实现这些目标,DSP处理器的指令集通常都允许程序员在一个指令内说明若干个并行的操作。例如,在一条指令包含了MAC操作,即同时的一个或两个数据移动。在典型的例子里,一条指令就包含了计算FIR滤波器的一节所需要的所有操作。这种高效率付出的代价是,其指令集既不直观,也不容易使用(与GPP的指令集相比)。

GPP的程序通常并不在意处理器的指令集是否容易使用,因为他们一般使用象C或C++等高级语言。而对于DSP的程序员来说,不幸的是主要的DSP应用程序都是用汇编语言写的(至少部分是汇编语言优化的)。这里有两个理由:首先,大多数广泛使用的高级语言,例如C,并不适合于描述典型的DSP算法。其次,DSP结构的复杂性,如多存储器空间、多总线、不规则的指令集、高度专门化的硬件等,使得难于为其编写高效率的编译器。

即便用编译器将C源代码编译成为DSP的汇编代码,优化的任务仍然很重。典型的DSP应用都具有大量计算的要求,并有严格的开销限制,使得程序的优化必不可少(至少是对程序的最关键部分)。因此,考虑选用DSP的一个关键因素是,是否存在足够的能够较好地适应DSP处理器指令集的程序员。

8 开发工具的要求

因为DSP应用要求高度优化的代码,大多数DSP厂商都提供一些开发工具,以帮助程序员完成其优化工作。例如,大多数厂商都提供处理器的仿真工具,以准确地仿真每个指令周期内处理器的活动。无论对于确保实时操作还是代码的优化,这些都是很有用的工具。

GPP厂商通常并不提供这样的工具,主要是因为GPP程序员通常并不需要详细到这一层的信息。GPP缺乏精确到指令周期的仿真工具,是DSP应用开发者所面临的的大问题:由于几乎不可能预测高性能GPP对于给定任务所需要的周期数,从而无法说明如何去改善代码的性能。

微处理器(Microprocessor)的分类

通用处理器(GPP)

采用冯.诺依曼结构,程序和数据的存储空间合二而一

8-bit Apple(6502),NEC PC-8000(Z80)

8086/286/386/486/Pentium/Pentium II/ Pentium III

PowerPc 64-bit CPU(SUN Sparc,DEC Alpha, HP)

CISC 复杂指令计算机, RISC 精简指令计算机

采取各种方法提高计算速度,提高时钟频率,高速总线,多级Cashe,协处理器等

Single Chip Computer/ Micro Controller Unit(MCU)

除开通用CPU所具有的ALU和CU,还有存储器(RAM/ROM)寄存器,时钟,计数器,定时器,串/并口,有的还有A/D,D/A

INTEL MCS/48/51/96(98)

MOTOROLA HCS05/011

DSP

采用哈佛结构,程序和数据分开存储

采用一系列措施保证数字信号的处理速度,如对FFT的专门优化

MCU与DSP的简单比较

MCU DSP

低档 高档 低档 高档

指令周期(ns) 600 40 50 5

乘加时间(ns) 1900 80 50 5

US$/MIPS 1.5 0.5 0.15 0.1

飞速发展的数字信号处理器

由于超大规模集成电路技术的迅猛发展,过去二十年中,数字信号处理技术,即DSP(Digital Signal Processor)技术也得到了突飞猛进的发展,这种发展趋势在今后十年内仍将保持下去。据世界半导体贸易统计组织发布的统计与预测报告,2001~2006年可编程DSP市场的预期增长率为27.2%。预期2006年DSP市场将达到141.9亿美元,且增长率是逐年递增的,2005年的增长率预期为34%。到2010年,DSP芯片的集成度将会提高11倍,单个芯片上将会集成5亿只晶体管。目前DSP的生产工艺正在由0.35μm转向0.25μm、0.18μm、0.13μm,到2005年可能达到0.075μm。

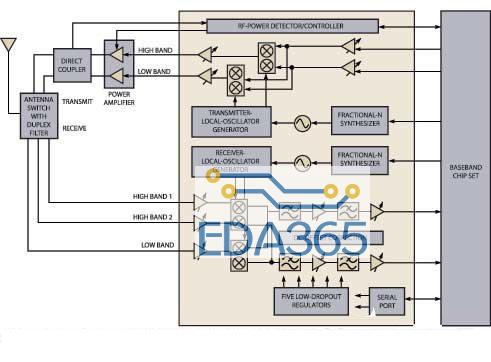

集成度的提高使得硅片的面积进一步缩小,从而导致DSP芯片成本降低,价格下降。价格下降促使需求的上升和应用领域的扩展。DSP已从军用转向民用,在计算机、通信、消费类电子产品方面即所谓3C领域得到了广泛的应用。DSP在通信领域应用最多,占72%,计算机占3%,消费类、办公自动化各占2%,从趋势上看,工业(特别是变频电机控制)中的应用,以及消费类产品中应用的份额会有所上升。

在通信领域,DSP产品涵盖了从3G无线基站到无线局域网的广泛应用,数字化电视也离不开DSP。DSP在语言处理中的应用也是尽人皆知的,包括语言的压缩与解压,语言的合成,语言的识别等。

计算机的硬盘驱动器在使用DSP技术以后可大大提高存取速度,提高容量和缩小体积,以至于今后有可能用于掌上电脑。在PC机中,DSP可加速图形处理功能。以后的PC机,可能每台PC中含有不只一颗DSP芯片。在计算机外设中,激光打印机、扫描仪、光盘机等需要大量数据传输的设备,都有可能用到DSP技术。

DSP技术发展的另一趋势是速度更快,功耗更低,DSP片外的速度能达到几十兆赫已经近于极限,为了降低系统的噪声,提高系统抗干扰能力,片外时钟有进一步降低的趋势,即外部使用几兆赫的振荡器就够了,而片内则用压控振荡器加锁相环的技术,把片内时钟速度提高到100MHz、200MHz乃至更高,会有更多的DSP片内时钟达到1GHz。预期到2010年,同类水平的DSP的功耗将降到原来的1/3。

DSP与CPU

如果用普通计算机中的CPU来处理算法,做乘法和加法都要调用相应的乘法、加法函数,如果是浮点数运算,通常CPU需要将浮点运算交给协处理处理,虽然协处理器的浮点运算速度可能很快,但加上CPU将输入参数传出,再将运算结果取回的时间,会显得速度很慢;做循环时,要有循环变量,每次循环变量加1后再判断是否已经循环了n次,这一过程是比较慢的。

而DSP则在硬件设计上针对这类计算采取了一些独特的设计,以求最快的运算速度,以至于趋于模拟电路的延迟时间。

DSP能在一个时钟周期内完成乘法和加法运算,并能并行地同时将下面运算要用到的两个参数传入相应的运算用寄存器。在乘法及乘加指令的执行方式上,DSP的小数乘法在算法上分定点算法DSP与浮点算法DSP。在定点类DSP中,小数点的位置是固定的,不论定点的DSP还是浮点的DSP,乘法器都是用硬件逻辑完成的,乘法可以在一个指令周期内完成。

在循环方面,DSP有诸如重复n次(Repeat n),或循环n次(DO Loop n)等指令,使DSP能迅速完成n次循环,而不必每次都检查是不是已经循环n次了。这就是DSP在做数字信号处理方面的优势与独到之处。也是DSP区别于CPU的地方。

DSP与CPU在结构方面的另一区别是,DSP往往采用哈佛结构,而传统的CPU多为冯.诺曼结构(Von Neuman)。冯.诺曼结构指的是将程序与数据统一编址,不区分存储器的程序空间和数据空间。而哈佛结构指将程序空间与数据空间分开编址,这样在DSP处理数据空间运算与数据传输的同时可以并行地从程序空间读取下一条指令。采用哈佛结构,将程序空间与数据空间分开编址的好处是速度快,读程序和读写数据可以同时进行。

DSP在内核设计方面还有一个特点是采用多重流水线结构,流水线结构的层次深度可以从3级到6级。程序的执行过程大致可分为读指令、指令译码、指令执行等几个阶段。DSP在第一个时钟周期内读第一条指令,在第二个周期译码第一条指令同时在第二个周期内读入第二条指令,在第三个时钟周期内执行第一条指令,译码第二条指令,同时读入第三条指令,这样虽然执行一条指令仍需要三个周期,可是由于并行的流水线处理,看起来好像每条指令都是在一个周期内完成的,这就是流水线结构。

DSP的特点

DSP在体系结构上与通用微处理器有很大的区别。下面是几个关键的不同点:

单周期指令:大多数DSP都拥有流水结构,它可以在一个时钟周期内执行一条语句。

快速乘法器:信号处理算法往往大量用到乘加(multiply-accumulate,MAC)运算。DSP有专用的硬件乘法器,它可以在一个时钟周期内完成MAC运算。硬件乘法器占用了DSP芯片面积的很大一部分。(与之相反,通用微处理器采用一种较慢的、迭代的乘法技术,它可以在多个时钟周期内完成一次乘法运算,但是占用了较少了硅片资源)。

多总线:DSP有分开的代码和数据总线(一般用术语“哈佛结构”表示),这样在同一个时钟周期内可以进行多次存储器访问——这是因为数据总线也往往有好几组。有了这种体系结构,DSP就可以在单个时钟周期内取出一条指令和一个或者两个(或者更多)的操作数。

地址发生器:DSP有专用的硬件地址发生单元,这样它可以支持许多信号处理算法所要求的特定数据地址模式。这包括前(后)增(减)、环状数据缓冲的模地址以及FFT的比特倒置地址。地址发生器单元与主ALU和乘法器并行工作,这就进一步增加了DSP可以在一个时钟周期内可以完成的工作量。

硬件辅助循环:信号处理算法常常需要执行紧密的指令循环。对硬件辅助循环的支持,可以让DSP高效的循环执行代码块而无需让流水线停转或者让软件来测试循环终止条件。

数据格式:除了标准的整数型格式外,DSP一般支持定点和(或)浮点数。对数据格式和精度的选择取决于应用程序所需,例如:

16位定点DSP可以满足语音信号处理和控制所需

24位和32位定点DSP可以满足高质量音频信号处理所需

32位浮点DSP可以满足图形和图像处理所需

DSP的特点:

DSP处理器采用哈佛结构和改进的哈佛结构。

哈佛结构就是将程序代码和数据的存储空间分开,各有自己的地址和数据总线。之所以采用哈佛结构,是为了并行进行指令和数据处理,从而可以大大地提高运算的速度。为了进一步提高信号处理的效率,在哈佛结构的基础上,又加以改善。使得程序代码和数据存储空间之间可以进行数据的传输,称为改善的哈佛结构。

采用流水技术。

流水技术是将各指令的各个步骤重叠起来执行。DSP处理器所采用的将程序存储空和数据存储空间的地址与数据总线分开的哈佛结构,为采用流水技术提供了很大的方便。

为了提高DSP处理器的运算速度,它们无例外地设置了硬件乘法器,以及MAC(乘并且累加)一类的指令。

DSP处理器都为DMA单独设置了完全独立的总线和控制器,这是和通用的CPU很不相同,其目的是在进行数据传输是完全不影响CPU及其相关总线的工作。

在DSP处理器中,设置了专门的数据地址发生器来产生所需的数据地址。数据地址的产生与CPU的工作是并行的,从而节省CPU的时间,提高信号的处理速度。

DSP处理器为了自身工作的需要和外部环境的协调工作。往往都设置了丰富的外设。如时钟发生器。定时器等。

定点DSP处理器和浮点DSP处理器。定点DSP中经常要考虑溢出问题,在浮点DSP基本上可以不考虑。与定点DSP处理器相比,浮点DSP处理器的速度更快,尤其是作浮点运算。在实时性要求很到的场合。往往考虑浮点DSP处理器。而浮点DSP处理器的价格比较高,开发难度更大。

为什么CCS需要安装Driver?

CCS是开放的软件平台,它可以支持不同的硬件接口,因此不同的硬件接口必须通过标准的Driver同CCS连接。

Driver安装的常见问题?

请认真阅读“安装手册”和Driver盘中的Readme。 1)对于SEED-XDS,安装Readme中的步骤,将I/O口设为240/280/320/340。 2)对于SEED-XDSPP,安装Readme中的步骤,将I/O口设为378或278。3)对于SEED-XDSUSB,必须连接目标板,安装Readme中的步骤,将I/O口设为A,USB连接后,主机将自动激活相应的Driver。 4)对于SEED-XDSPCI,安装Readme中的步骤,将I/O口设为240,PCI接口板插入主机后,主机将自动激活相应的Driver。 5)对于Simulator,需要选择不同的CFG文件,以模拟不同的DSP。 6)对于C5402 DSK,将I/O口设为请认真阅读“安装手册”和Driver盘中的Readme。 1)对于SEED-XDS,安装Readme中的步骤,将I/O口设为240/280/320/340。 2)对于SEED-XDSPP,安装Readme中的步骤,将I/O口设为378或278。注意主机BIOS中并口的型式必须同xds510pp.ini中一致。 3)对于SEED-XDSUSB,必须连接目标板,安装Readme中的步骤,将I/O口设为240/280/320/340,USB连接后,主机将自动激活相应的Driver。 4)对于SEED-XDSPCI,安装Readme中的步骤,将I/O口设为240/280/320/340,PCI接口板插入主机后,主机将自动激活相应的Driver。 5)对于Simulator,需要选择不同的CFG文件,以模拟不同的DSP。 6)对于C5402 DSK,将I/O口设为378或278。 7)对于C6211/6711 DSK,将I/O口设为378或278。 8)对于C6201/C6701 EVM,将I/O口设为0。

Link的cmd文件的作用是什么?

Link的cmd文件用于DSP代码的定位。由于DSP的编译器的编译结果是未定位的,DSP没有操作系统来定位执行代码,每个客户设计的DSP系统的配置也不尽相同,因此需要用户自己定义代码的安装位置。以C5000为例,基本格式为:

-o sample.out

-m sample.map

-stack 100

sample.obj meminit.obj

-l rts.lib

MEMORY {

PAGE 0: VECT: origin = 0xff80, length 0x80

PAGE 0: PROG: origin = 0x2000, length 0x400

PAGE 1: DATA: origin = 0x800, length 0x400

}

SECTIONS {

.vectors : {} >PROG PAGE 0

.text : {} >PROG PAGE 0

.data : {} >PROG PAGE 0

.cinit : {} >PROG PAGE 0

.bss : {} >DATA PAGE 1

}

如何将OUT文件转换为16进制的文件格式?

DSP的开发软件集成了一个程序,可以从执行文件OUT转换到编程器可以接受的格式,使得编程器可以用次文件烧写EPROM或Flash。对于C2000的程序为DSPHEX;对于C3x程序为HEX30;对于C54x程序为HEX500;对于C55x程序为HEX55;对于C6x程序为Hex6x。以C32为例,基本格式为:

sample.out

-x

-memwidth 8

-bootorg 900000h

-iostrb 0h

-strb0 03f0000h

-strb1 01f0000h

-o sample.hex

ROMS {

EPROM: org = 0x900000,len=0x02000,romwidth=8

}

SECTIONS {

.text: paddr="boot"

.data: paddr="boot"

}

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多