软件无线电[1][2]代表着包括无线通信在内的几乎所有的无线电电子信息系统的发展趋势,其核心思想就是将模数/数模变换器尽量靠近天线,在对信号充分数字化的基础上依靠软件来定义无线电的各项功能。在现阶段由于各种关键器件,特别是受ADC(模数变换器)和DSP(数字信号处理器)发展水平的限制,数字中频软件无线电[3]正成为理想软件无线电的一种经济、适用的折中选择。在数字中频软件无线电接收机中,ADC直接采样的是模拟中频信号,输出的高速数字信号经由数字下变频器(DDC)的变频、抽取(Decimation)和低通滤波处理之后成为低速的基带信号,供后续的DSP作进一步的处理。Intersil公司(1999年8月更名前为Harris公司)一直占据着商用数字中频标准产品市场的较大份额,尤其是DDC系列产品更是倍受青睐;HSP50214B PDCProgrammable Downconverter就是该公司继HSP50016、HSP50214和HSP50214A之后推出的单通道DDC中性能最好、功能最强的新款DDC产品。

1 结构组成与工作机理

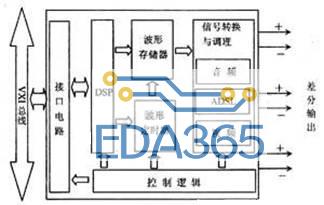

HSP50214B可大体分为13个功能模块:同步电路、输入模块、输入电平检测、变频模块(正交混频器与数控振荡器)、CIC(Cascaded Integrator-Comb)抽取滤波器、HB(Half-band)抽取滤波器、255阶可编程FIR滤波器、自动增益控制器(AGC)、重采样与HB内插滤波器、定时数控振荡器、坐标变换器、鉴频(幅)模块和输出模块。图1为HSP50214B的功能组成框图。

从其结构组成可见,HSP50214B可以完成通常DDC所应具有的三大功能:一是频率变换;二是采样率压缩(抽取);三是滤波整形。其中的变频功能由图1中所示的正交混频器完成,抽取和滤波功能则由图1中所示的CIC抽取滤波器、HB抽取滤波器、255阶FIR抽取滤波器、重采样和HB内插(Interpolation)滤波器级联完成。事实上,这里的变频和低通滤波合在一起就是带通信号的正交调制过程[5]。而其中的抽取功能实际上是通过采样率变换的多级级联实现的。就系统所需的运算量和存储量来说,采样率变换的多级实现通常要比单级实现更有效[5]。因此,HSP50214B工作机理的理论渊源就是带通信号的正交调制理论和采样率变换的多级实现理论。除了上述的三大功能以外,HSP50214B还可以完成诸如自动增益控制、片内和片间的同步控制、载波和码元跟踪以及对部分常规通信信号的解调等功能。

2 引脚描述与技术特性

HSP50214B是一个超大规模集成芯片,共有120个引脚,各引脚的说明如表1所示。

表1 HSP50214B 可编程下变频器的引脚说明

| 引脚 | 说明 | 引脚 | 说明 |

| Vcc | 电源输入正电压 | OEAH | AOUT总线高字节位输出使能 |

| GND | 接地 | OEAL | AOUT总线低字节位输出使能 |

| CLKIN | 输入时钟 | OEBL | BOUT总线高字节位输出使能 |

| IN(13:0) | 输入数据 | OEBH | BOUT总线低字节位输出使能 |

| ENI | 输入使能 | COF | 载频补偿输入 |

| GAINADJ(2:0) | 增益调整输入 | COFSYNC | 载频补偿同步输入 |

| PROCCLK | 芯片后端处理时钟 | SOF | 重采样补偿频率输入 |

| AGCGNSEL | AGC增益选择 | SOFSYNC | 重采样补偿频率同步输入 |

| SEROUTA | 串行输出总线A | SEL | 输出数据地址选择线 |

| SEROUTB | 串行输出总线B | C(7:0) | 与微处理器接口的数据总线 |

| SERCLK | 串行数据输出时钟 | A(2:0) | 与微处理器接口的地址总线 |

| SERSYN | 串行输出同步信号 | WR | 与微处理器接口的写脉冲 |

| AOUT(15:0) | 并行输出总线A | RD | 与微处理器接口的读脉冲 |

| BOUT(15:0) | 并行输出总线B | MSYNCO | 多芯片应用时的同步输出信号 |

| DATARDY | 输出使能信号 | MSYNCI | 多芯片应用时的同步输入信号 |

| SEROE | 串行输出使能信号 | SYNCIN1 | 前端刷新同步输入信号 |

| INTERRP | 中断输出 | SYNCIN2 | 后端刷新同步输入信号 |

| REFCLK | 参考时钟 | SYNCOUT | 同步脉中输出 |

概括地说,HSP50214B具有的技术特性如下:

· 前端处理速度CLKIN达到65MSPS,后端处理速度PROCLK达55MSPS。

· 全部处理过程的无虚假信号动态范围(SFDR)大于100dB。

· 在低通输出带宽为982kHz的时候输出速率可达12.94MSPS。

· 总抽取因子范围为4~16384,由于有了重采样级,抽取因子可以是非整数。

· 32-bit的可编程载频数控振荡器(NCO)可用于信道分选和载波跟踪,频率分辨率可达0.015Hz(CLKIN=65MSPS时)。

· 32-bit的重采样NCO可用于码元跟踪。

· 数字AGC可用于进一步扩大信号的位分辨率,增益容限可在0~96.332dB、增益调整速率可在0.000106~3.275dB/PS之内可编程,增益调整有固定和自动两种选择。另外还有输入电平检测器用来构成外部模拟增益控制环路。

· 输入分辨率为14-bit,输出分辨率为16-bit,支持直接串行、直接并行、FIFO式缓存和快照式缓存输出。

· 笛卡儿坐标到极坐标转换器和鉴频(幅)器可用于AM、SSB、FM、PM、ASK、FSK、PSK、QPSK和M进制QAM等信号的解调。

3 应用体会

HSP50214B的最大特点是通过其灵活的可编程性可获得功能的多样性。它可以与HSP50210数字科斯塔斯环(Digital Costas Loop)一起用于PSK信号的接收。当用于单信道软件无线电时,它可同时支持宽带和窄带处理。当应用于基站接收时,若通过适当的编程,HSP50214B可以满足各种各样的通信标准,如FDMA中的AMPS(IS-91);TDMA中的IS-54、GSM、PCN和北美TDMA IS-136;CDMA中的IS-95等等。它还可很好地用于第三代移动通信的各种应用研究中。

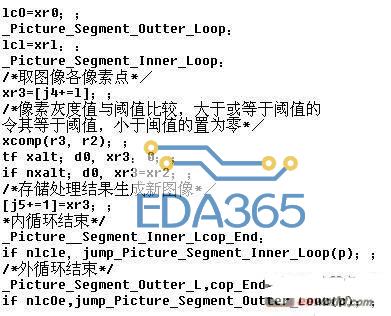

为了最优地配置HSP50214B,必须对该PDC芯片进行仔细地研究,既要了解整个PDC芯片的结构功能,又要明确芯片中各个模块在PDC中的地位、功能和特性。这是因为在芯片设计时,其中的每个模块都被赋予了特殊的作用。HSP50214B的核心是完成三大功能的两大模块:变频模块和采样率变换模块(兼有滤波整形功能);前者的配置相对简单一些,比较复杂的是后者。在采样率变换模块中,CIC抽取滤波器用来完成主要的抽取任务;5个HB抽取滤波器用来完成抽取因子为2的幂次的采样率压缩任务;255阶FIR抽取滤波器其实是指该FIR滤波器的最大可用阶数为255,整个采样率变换模块的滤波整形功能主要由它来承担,它还可用来补偿其前面的滤波器如CIC滤波器在通带内的衰减等;重采样级用来实现采样率的非整数倍变换;2级HB内插滤波器可以恢复由于前面对信号进行抽取而损失的时间分辨率,并且还可以让前面的255阶FIR滤波器工作在尽量接近Nyquist采样率的低采样率下,以使255阶FIR滤波器的可用滤波器阶数增大,从而更好地完成对信号的滤波整形处理[6]。在采样率变换模块的配置中需要特别考虑的还有PDC芯片的硬件制约因素,如各级间的接口速率是否匹配以及各级滤波器在进行滤波整形处理时能够正常工作的滤波器指标范围等。

此外,在PDC的配置中还必须考虑以下模块:使整个PDC芯片正常工作的AGC模块;解调各种常规通信信号的鉴频(幅)模块;使单片PDC内的各个模块以及在多片PDC联合使用时各PDC间都能协调工作的同步控制功能模块等。

4 一个实用的数字中频软件无线电实验系统

在此给出一个实用的数字中频软件无线电实验系统,如图2所示。其中用于中频采样的ADC为Analog Device公司的AD6644,接收机中频为10.7MHz。数字信号源是为了进行各种软件无线电的相关研究而设置的。PDC后的基带处理器既可以是通用DSP,也可以是高档PC机。前面的模拟接收机根据实际需要既可以挂接宽带接收机,也可以挂接窄带接收机。全部系统都是通过PC机控制运行的。通过实验,HSP50214B可以很好地完成变频、采样率压缩、滤波整形以及对几种常规通信信号如AM、FM、FSK和PSK等的解调。

事实上,不止是在通信领域,对于各种用途的无线电电子信息接收系统,都可以考虑应用象HSP50214B这样高性能的PDC芯片来开发具有软件无线电意义上的新一代产品。为了构建一个多通道系统,还可以在一个系统中应用多片HSP50214B。另外,Intersil于2000年最新推出了该公司的首片多通道PDC——HSP50216QPDC(Quad PDC),该PDC共有4个通道,每个通道的结构与单片HSP50214B基本相同,但在性能上有所提高,而且可以进行独立的配置。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多