随着SoC设计规模的与日俱增,其功能日趋复杂,芯片的验证阶段占据了整个芯片开发的大部分时间。为了缩短验证时间,在传统的仿真验证的基础上涌现了许多新的验证手段,如SDV(Software Driven verification)、BFM(Bus Function Model)等,以及基于FPGA的原型验证技术。

因FPGA工艺及技术的发展,其速度、容量和密度都大大增加,功耗和成本在不断的降低,使得基于FPGA的原型验证得到广泛的应用。基于FPGA的原型验证可以比软件仿真速度高出4~6个数量级,而且还可以提高流片成功率,并为软件开发提供了硬件平台,加速了软件的开发速度。

本文主要论述了FPGA基原型验证的实现方法,并且针对ARM1136为内核的SoC,如何快速而有效地搭建一个原型验证平台做了详细的论述,最后还以UART为例来说明一种简单、可重用性好、灵活性强的测试程序架构。

1 基于ARM1136的SoC设计

本文验证的SoC芯片是定位于手持视频播放设备、卫星导航产品的高性能应用处理器,采用了ARM1136作为内核,ARM11在提供超高性能的同时,还能保证功耗、面积的有效性。

同时在这个架构中还采用了ARM公司的AMBA(Advanced Microcontroller Bus Architecture)总线,它是一组针对基于ARM核的片上系统之间通信而设计的标准协议。在设计中,对于一些处理数据和通讯速度要求较高的设备挂在AHB总线上,而那些对总线性能要求不高的设备挂在APB总线上。

为了能够提高一些设备间的数据传输速度,该设计加入了DMA,其支持存储器到存储器、存储器到外设、外设到存储的传输。

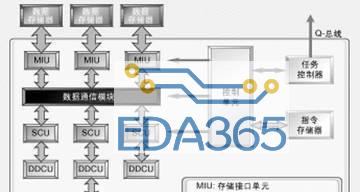

基于ARM11设计的SoC系统构架如图1所示,这个系统还包括了USB控制器、LCD控制器、图像处理单元GPU、视频处理单元VPU、GPS、I2S、通用异步串口UART、同步串口SPI、TIMER、PWM、实时时钟(RTC)、I2C总线和功耗管理单元(PMU)等。

2 FPGA原型验证平台的快速搭建

FPGA的发展为SoC的原型验证提供了巨大的发挥空间,面对复杂的SoC系统,传统的一些验证方法和单一的验证技术已经不能满足设计的要求。本文所设计的平台不仅能加快开发速度,提高流片成功率,而且还具有低错误率、快速和简易的特点,因此特别适合用于RTL代码更改频繁的设计中。

2.1 FPGA原型验证平台的硬件环境设计

FPGA原型验证平台的硬件设计应该考虑FPGA的逻缉资源、应用资源、扩展能力、PCB信号质量、调试难度、组态和成本等方面的因素。本原型系统设计的FPGA开发板采用的是Terasic公司的DE3开发板,其FPGA芯片是StratixIII EP3SL340,扩展板是根据SoC整体验证方案而设计的PCB板。FPGA原型验证平台的硬件架构如图2所示,为了使FPGA的调试性能增强,该平台加入了ICE在线调试器,它可以让验证人员和软件开发人员观察到ARM内核和设计中各个寄存器的状态信息,并且可以进行单步运行、在线调试等。

2.2 FPGA原型验证平台的软件环境设计

SoC芯片采用的是ASIC工艺流程,ASIC和FPGA在实现结构上是不同的,AISC通常使用综合工具将RTL级代码映射到芯片制造厂提供的标准单元上。这些标准单元包括完成逻辑功能的与非门、非门、或非门等基本门单元和完成存储功能的各类触发器、锁存器,以及其它的宏单元。而FPGA器件为了实现可编程功能,通常使用查找表结构实现电路的逻辑功能。本文原型设计流程如图3所示,在图示中仅是将部分模块列出,如PMU和GPIO。

2.2.1 设计代码的转换

虽然FPGA和ASIC所用资源和实现方式不同,但在进行原型设计中需要遵循的一个原则就是“尊重原设计”。在FPGA现有资源情况下实现SoC时,尽可能地少改动原SoC设计,在此基础上需要对原设计做如下转换:

(1)存储模块。存储单元是必须进行代码转换的,ASIC中的存储单元通常用代工厂所提供的Memory Compiler来定制。如果直接将ASIC代码中的存储单元作为FPGA的输入,通常综合器是综合不出来的,即使能综合出来,也要花费很长时间,并且资源消耗多、性能不好。而FPGA厂商一般提供经过验证并优化的存储单元,因此存储单元要进行代码转换。在设计里用FPGA的RAM宏单元来替换ESRAM,SoC芯片里面的DDR PHY是模拟的模块,此要替换成Altera公司的PHY的IP核。

(2)时钟和门控。数字电路中,时钟是整个电路最重要、最特殊的信号。在ASIC中,用布局布线工具来放置时钟树,利用代工厂提供的PLL进行时钟设计。而FPGA中通常已经配置一定数量的PLL宏单元,并有针对时钟优化的全局时钟网络,一般是经过FPGA的特定全局时钟管脚进入FPGA内部,后经过全局时钟BUF适配到全局时钟网络,这样的时钟网络可以保证相同的时钟沿到达芯片内部每一个触发器的延迟时间差异可以忽略不计,因此时钟单元需要采用FPGA的PLL宏单元和专门的时钟布线资源来替换。

为了减少功耗,SoC设计中使用了门控时钟(clockgating),如图4所示,对于FPGA来说这种门控时钟容易产生毛刺,导致数据不正确,所以在FPGA设计中要使用时钟使能寄存器代替门控时钟。

2.2.2 设计综合

综合是将较高级抽象层次的描述转换成较低层次描述,在这里就是把HDL程序转化成标准的门级结构网表。本设计采用的EDA工具是Sy-nopsys公司的Synplify,将SoC的各个模块分别进行综合,综合时要加约束文件和Altera公司的相应器件的库文件,产生一个FPGA网表文件。

[page]

2.2.3 等价性检查

形式验证(Formal Verification)主要用来在覆盖所有可能输入情况下,检查是否与给定的规范一致。等价性检查(equivalence check-ing)是形式验证中的一部分,它主要是检查两个门级网表(gate-level netlisf)之间是否一致,保证网表处理后不会改变电路的功能,或者检查RTL和门级网表之间是否一致,保证网表能正确地实现RTL代码所描述的功能,或者检查RTL间是否一致,保证两种RTL描述逻辑一致。这种方法主要是用来寻找实现(Implementation Design)中的缺陷,而不是设计中的缺陷。由于芯片开发中,设计代码将不断的更改,都需要

更新FPGA的镜像文件,这样在频繁的镜像制作过程中,可能会因为环境和设计的更改引出许多实现过程中的错误,而本文为了减少这些错误,采用的Synopsys公司的Formality工具,主要用于检查网标和RTL间是否一致,把RTL设计作为Reference Design,而把网标作为Imple-mentation Design,在进行等价性检查时要加入Altera器件综合过程中需要的相关库文件。

2.2.4 设计整合和布局布线

把多个设计文件转换合并到一个设计库文件中,并把整合后的设计输入到Altera公司的QuartuslI工具,将综合过的网表中的逻辑门映射到FPGA的内部资源中,如ALUT等。

布局是指从映射取出定义的逻辑和输入输出块,并把它们分配到FPGA内部的物理位置,布线是指利用自动布线软件使用布线资源选择路径试着完成所有的逻辑连接。

2.2.5 时序分析

在设计实现过程中,在映射后需要对一个设计的实际功能块的延时和估计的布线延时进行时序分析。而在布局布线后,也要对实际布局布线的功能块延时和实际布线延时进行时序分析。时序分析不仅可以检查出我们代码设计中的时序问题,还可以检查出由于布局布线产生的时序问题。在本设计中用Altera公司的TimeQuest来进行时序分析,通过对原型设计增加时序约束,提高了工作主频和减少了关键路径的延时。在设计中经常存在时序违约的情况,这时需要查看违约的关键路径,然后查找原因,进行修改后再进行时序分析,重复整个过程直到满足要求。

2.2.6 镜像文件的生成和下载配置

QuartusII经过整合、布局布线等一系列操作后,最终会生成一个配置FPGA的位流文件(.sof洛式),然后利用QuartusII的Programmer工具,通过USB Blaster下载到FPGA,此时FPGA实现了原SoC设计的功能,原型验证环境搭建完成。

3 FPGA原型验证测试激励的设计

测试程序在FPGA基原型验证中起至关重要的作用,现在的SoC设计很多都采用IP复用的方式,本文所设计出的测试程序有可重用性好、功能覆盖率高和调试简易等特点。

测试程序的基本框架如图5所示,具体模块的测试程序只需要根据框架所提供的接口进行编写相应的测试程序即可,代码主要由以下四部分组成:

(1)系统启动部分。主要包含系统的异常向量表和系统启动后设置ARM内核的配置程序,如各种模式下的堆栈设置、开启或关闭FIR和IRQ、设定中断向量表等,在Boot_gfd.s中提供了跳到测试程序的接口。

(2)模块测试部分。在此部分根据各个模块的功能,编写相应的测试函数,系统在执行时会调用这些函数,完成我们各个模块的功能测试。

(3)头文件部分。为了方便代码的编写和理解,在tyoedef.h文件中对系统的数据类型做了重新定义并包含了部分公用函数的宏定义。一个SoC系统中拥有大量的寄存器,在本设计中用Register.h文件来存放这些寄存器地址的宏定义。

(4)Scatter文件部分。scatter文件是用来描述删连接器生成映像文件时需要的地址映射信息和加载域信息。

下面以UART模块为例,在此框架下根据其接口编写相应的测试程序。

验证计划:通过待验UART与PC进行通信来验证其功能是否正确,主要验证的功能点有:1)寄存器读写;2)三种工作模式普通模式、自流控模式、LoopBack模式;3)奇偶校验;4)波特率;5)FIFO触发级。

测试程序:根据上边的功能点可以划分两个测试的基本的函数,一个是寄存器读写的测试函数UART_RWTst(),还有一个就是UART工作配置函数UART_Config(),这个函数提供一个接口,通过这个接口可以配置UART的工作模式、奇偶校验方式、波特率大小、FIFO触发级。在更高层的测试应用程序中调用配置程序,变化配置参数,使其与PC进行收发数据,然后查看或比对数据,判别其功能是否正确。测试程序文件结构如图5所示。

验证结果:当待验UART向PC发送数据时,在PC的超级终端会显示这些数据,UART功能验证结果可通过观测或数据比对来判断,如图6所示。

4 结论

同样的测试激励程序在此原型平台的执行速度要比SDV(Software driven verification)平台快4~6个数量级。本验证平台的搭建过程中对其进行了形式验证和时序分析,大大减少了在原型设计中由于FPGA实现而导致的错误。本平台的软件测试程序具有接口简单、易调试、可重用性好等特点,笔者在此原型平台下完成了部分模块的验证,有效地提高了验证效率,缩短了项目的开发周期,加大了流片成功率。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多