1 引言

数据采集技术是信息科学的一个很重要的分支,它研究信息数据的转换,采集、存储、处理以及显示等作业,在信号处理、智能仪器以及工业自动控制等领域起到巨大的作用。如工业生产过程中常常需要对湿度、温度、压力、流量等各种工艺参数随时进行检测和监控,同时还要将检测到的数据及时传递给上位机,以实现对于参数的随机查询,对信息的存储与处理,及时调整控制方案,提高生产效率和产品质量。

但是,在许多其他领域如:雷达通信,地理信息,图像传输,军工及医疗化工,为了捕捉,采集,存储,处理,传输和再现瞬间变化的模拟信号(类似脉冲信号),则对数据采集速度及效率提出了更高的要求。本文应用单片机89C51作为主控制来实现模拟信号的高速采集、存储及再现。应用中,单片机只对信号进行中转不对数据进行处理,采集的数字信号传给DA转换器后,由DA转换器将信号还原成模拟信号。

2硬件组成

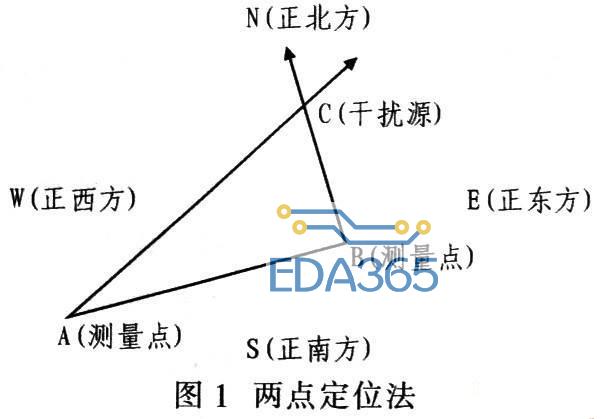

设计的方案主要用于瞬间信号的采集,要求选用的A/D转换芯片转换速度比较快,经过考虑选用MAX114。89C51单片机的指令执行时间(us级)与AD转换芯片的转换时间往往不同步[1],因此在单片机与AD转换器间加入高速缓存IDT72041,用高速缓存来连接单片机与AD转换器。系统整体结构框图如图1所示。

图1 系统整体结构框图

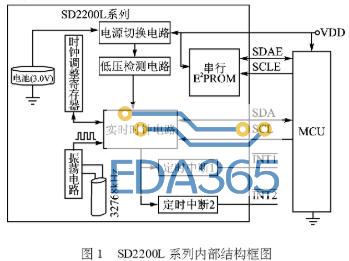

实际应用中,须将瞬间的连续的模拟信号转换成便于存储与分析的数字信号。在这个过程中应尽量避免模拟信号的失真,这就与AD转换芯片的转换精度与转换速度有极大的关联。在模拟信号的频率很高时,AD芯片的转换速度就显得尤其重要。MAX114芯片对输入的模拟电压有一定的要求,必须对输入的模拟电压进行放大以满足AD转换芯片的要求[2]。MAX114的前置放大电路如图2:

图2 放大与滤波电路

高通滤波只允许一定频率的信号通过,清除杂波的影响。MAX114的引脚REF+,REF-所接旁路电容消除干扰。MAX114为四通道的A/D芯片,而我们只需要一个通道转换数据,因此A1,A2必须接数字“0”。根据需要选择模式“0”状态来转换数据,引脚“5”MODE也必须接数字“0”。其真值表如表1所示: www.51kaifa.com

表1 MAX114真值表

AD转换芯片MAX114将转换出来的数字信号传送给高速缓存IDT72041。MAX114的工作时钟由内部时钟电路提供的时钟脉冲,缓存写控制信号也是由该芯片的 “INT”来控制,在AD芯片转换完毕后,“INT”产生一个低电平,这一低电平被传送给缓存芯片,数据即被写入缓存中并按照先入先出的规则进行保存。只有当缓存引脚(FF)为高电平,(EF)为低电平时,AD转换出来的数据才能被写入[3]。

IDT72XX系列是IDT公司推出的先进先出(FIFO)存储器芯片,它具有双口输入输出,采集传输速度快和先进先出的特点,能满足高速数据传输的要求[4]。

高速缓存IDT72041有这样一个特点:当缓存芯片被写满后,缓存芯片就不再接受外来的写信号,同时缓存IDT72041的满位FF变为低,同时会触发单片机的外部中断。单片机接收到中断信号后运行片选程序,第二块缓存开始读入A/D转换数据。以此类推,当所有的缓存芯片中的数据被全部写满后,单片机经运用程序传输缓存中的数据再进行处理。缓存中数据全部处理完后重新启动A/D转换,开始数据的采集。

为了保证数据采集的连续性和采集足够的数据,必须有较大的存储空间来存放数据,为此,本系统中将IDT72041芯片扩展了8片[5]。扩展中的第一个芯片用FL/RT端接地来表示,其它芯片的FL/RT端接高电平。且每个芯片的“XO”端必须接到下个芯片的“XI”端。并将每个芯片的 “EF”标志相“或”以构成新的空标志,每个芯片的“FF”端也相“或”在一起构成新的满标志。RT和HF在字深的扩展中不起作用。这里采用的方式是将8 块芯片的“ FF”端分别接在单片机的P2口,由单片机来控制写满。

在设计中,当IDT缓存芯片4K的存储空间被写满,缓存的引脚“FF”为低,MAX114转换的数据不能再写入。同时FF向89C51发出中断请求,单片机接收到中断信号后,用P0口来实现与缓存芯片的数据传送,然后由单片机对存储于IDT72041中的数据进行初步处理。经单片机P3.6口(WR)的片选,再将处理过的数据传给DAC0832[6]。

在硬件电路中,单片机控制IDT72041和DAC0832,MAX114开始采样时,要用到IDT72041中的D0~D7数据线、写控制端口 WR;当数据采样结束,即数据已经存储到IDT72041中,单片机就要从IDT72041中读取数据,要用到Q0~Q7线,读控制端口。在实际的运用中,通过QE脚和/DIR脚置不同的电平来解决信号串扰的问题。通过置QE脚不同的电平可以实现三态的功能,同时由/DIR脚来确定信号传输的方向。

3系统软件

3.1程序功能www.51kaifa.com

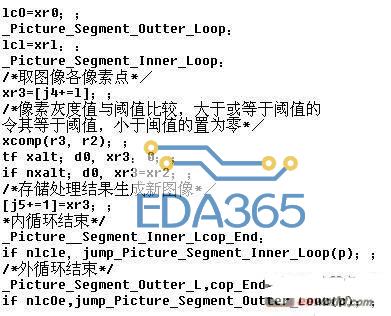

此程序的功能是实现AD芯片MAX114、缓存IDT72041之间的通信以及采样频率的控制,各功能分别用进程完成[6]。程序主体分为五个部分:单片机初始化及对外围器件的设置、对缓存的全满标志位判断以及该条指令的循环、对缓存的片选以及将缓存的数据传给单片机寄存器A、对DAC的片选以及将暂存器的数据传给DAC、判断缓存是否为空以及跳转。

3.2程序各部分的实现

第一部分是单片机的初始化及对外围器件,主要是对IDT72041的设置,开始是对89C51的P0、P1和P2口所有的端口置1,接下来是P1.1清“0”,实现IDT72041的复位,对P1.1清“0”,实现对MAX114进行片选,指令如下:

START:SETB P0

SETB P1

SETB P2

CLR P1.0

CLR P1.1

第二部分主要是判断缓存是否被写满。输入的模拟信号进入该系统,由放大电路先进行放大、整流,进入A/D(MAX114)进行转换,由于A/D芯片的INT脚在每转换结束一次将产生一个低电平,此低电平驱动缓存(IDT72041)进行写入数据,由于使用8片缓存,所以会出现数据先被写入哪个缓存的问题,为了提高单片机处理效率,在硬件上将前一个芯片的XO端接下一个芯片的XI端,逻辑“1” 芯片的FL/RT接地,其它芯片的FL/RT接高电平,这样就可以实现将8个缓存芯片组成一个存储整体,这样数据将从第一个芯片一直写到最后一个芯片,8 个缓存的写满端“FF”被接在单片节的P2口,用来判断每个缓存是否被写满。在硬件连接上,将8个缓存已经组成了一个整体存储体,所以在软件方面,只需判断P2.7是否为“0”来确定缓存是否被写满[7],即:

ST:JNB P2.7, ST

第三部分判断缓存是否写满,如果写满就中止A/D转换,已被转换的数据将全部被存储到缓存中,指令如下:www.51kaifa.com

SETB P1.1

第四部分对DAC的片选以及将暂存器的数据传给DAC。将首地址存入DPTR数据指针寄存器,从缓存中顺序读取数据并存入外部RAM,经由单片机初步处理后传送到DAC。指令如下:

MCADTS:MOV DPTR, # 7000H

CLR P2.6

MOVX A,@DPTR

MOV DPTR, #5000H

CLR P2.0

MOVX @DPTR,A

第五部分判断缓存是否为空,如果不为空将继续读取数据,否则程序跳转到初始位置,重复上述过程,实现对数据的不断采集及还原。指令如下:

SA: JNB INT1, MCADTS

SJMP START

结语:

本文作者创新点为:

本系统运用简单的MCS-51单片机来实现复杂的数据采集与还原电路。在操作过程中,将该应用系统按其功能分成各个模块,对电路进行焊接以及调试,并进行仿真测试。该系统设计方案电路简单,可靠性好,实现了高速数据采集的目的。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多