0 引 言

FIR滤波器的结构主要是非递归结构,没有输出到输入的反馈。并且FIR滤波器很容易获得 严格的线性相位特性,避免被处理信号产生相位失真。而线性相位体现在时域中仅仅是h( n)在时间上的延迟,这个特点在图像信号处理、数据传输等波形传递系统中是非常重要的。此外,他不会发生阻塞现象,能避免强信号淹没弱信号,因此特别适合信号强弱相差悬殊的情况。其主要的不足之处是,其较好的性能是以较高的阶数为代价换来的。因此,在保证相同性能的前提下,努力降低其阶数是FIR数字滤波器设计的重要因素之一。

下面介绍应用Matlab和DSP芯片来实现FIR滤波器的通用模式。

1 FIR滤波器的设计方法

通常采用窗函数法设计FIR滤波器方法简单,但是这些滤波器的设计还不是最优的。 首先 通带和阻带的波动基本上相等,虽然一般需要δ2

最优化设计是将所有的采样值作为变量,在某一优化准则下,通过计算机进行迭代运算得 到的最优结果。其优化准则可以使用均方误差准则。但实践证明,应用最大误差最小化准则 的等波纹迫近法是更为实用的方法,应用他设计时,阶数、通带和阻带的边缘以及误差的加 权函数都可以自由选择,十分灵活,设计得到的滤波器,其误差在整个频率范围内均匀分布 ,因而可以以最低的阶数迫近提出的指标要求。

设待设计滤波器的幅频特性为HdA(ω),实际得到的滤波器的幅频特性为HA(ω),目的是使HA(ω)最好地迫近HdA(ω)。等波纹最佳一致迫近是根据设计要求,导出一组条件,使整个迫近频率区域上的迫近误差绝对值为最小,定义一个加权函数W(ω),W(ω)在不同的频带下可以取不同的值,可用他自由决定各个频 带中误差的权重。优化设计时,W(ω)为已知函数,这样,加权误差函数E(ω)可定义为:

由于Q(ω)是一个已知的三角函数,故除在点ω=0,π外,上式处处有效。令:

则可得到如下数学模型:

据此,可以把FIR滤波器的设计问题,归纳为如下的加权契比雪夫迫近问题:寻找P( ω)的一组系数a(n)(或 使E(ω)的最大绝对值在整个频带上都达 到最小。即:

其中:B表示整个有意义的频带。

求解契比雪夫迫近问题的依据是交错定理(这里不再介绍)。

2 用Matlab设计FIR数字滤波器

Matlab信号处理工具箱采用Remez算法实现线性相位FIR滤波器的等波纹最佳一致逼近设计 。与其他设计方法相比,其优点是:设计指标相同时,使滤波器阶数最低;阶数相同时,使 通带最平坦,阻带最小衰减最大;通带和阻带均为等波纹形式,适合设计片段常数型滤波器 。其调用格式如下:

remezord函数用于估算FIR数字滤波器的等波纹最佳一致逼近设计的最低阶数N,从而使 滤波器在满足指标的前提下造价最低。基本调用格式如下:

其返回参数供remez函数使用。编制程序(略)FIR数字滤波器的滤波仿真程序:

设有一个正弦叠加信号:x=sin(2*pi*100*t)+sin(2*pi*200*t)+sin(2*pi*3 00*t);经过带通滤波器后,滤除频率为100 Hz和300 Hz的信号,如图1所示。结果如图2所示。

3 用DSP线性缓冲区和带位移的双操作数寻址方法来实现不同阶数的FIR数字滤波器

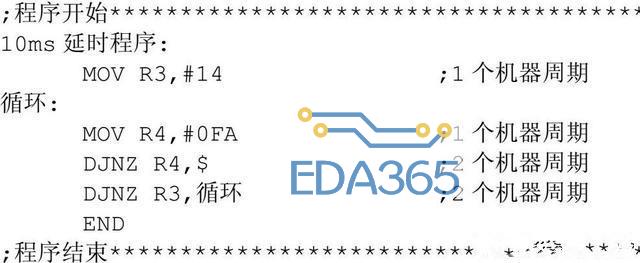

实现的核心器件采用美国德州仪器公司生产的DSP芯片TMS320C5402。对于N级FIR滤波 器,在数据存储器中开辟一个称之为滑窗的N个单元的缓冲区,存放最新的N个输入样本 。从最老的样本开始,每读一个样本后,将此样本向下移位。读完最后一个样本后,输入最 新样本至缓冲区的顶部(见图3)。FIR滤波器的主程序(程序流程图见图4),其中包括3个子程序Variableinc,Bfunction.asm,Filter_coeffinc。Variableinc程序的主要作用是:将TMS320个寄存器定义为全局符号,这样就可以直接引用寄存器(符号)。Bf unction.asm程序的主要作用是:初始化FEC和初始化C54。Filter_coeff.inc程序提供滤波器的系数,其系数用Q15格式表示。

4 结 语

实践证明,该滤波器准确度高、稳定性好,易于移植使用,具有较强的实用性与灵活性。Mat lab可方便地设计出FIR数字滤波器,并且修改系数方便。由于DSP的可移植性好,所以能从不同方法得来的滤波器系数写入filter_coeff.inc子程序中,从而得到不同的滤波效果。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多