随着技术的进步和大量外设的增加,不仅要求计算机并行口可以连接打印机,而且可以连接到其他外设,并要求能够双向传输数据,对高速外设还要求高速数据传输,如DPS。在科技飞速发展的今天,DSP的处理能力和速度也快速提高,广泛用户在科学研究、军事及通信等电子领域。在这些应用中免不了要和PC机进行高速数据传输。计算机并口传统的传输模式为SPP(标准并口),数据传输方向是从计算机到外围设备,只能输出数据,不能输入数据。这就限制了并行口高速数据通信的应用。于是我们在EPP模式下设计了一种实现DSP与PC机之间进行高速数据传输的方案。

在EPP模式下实现数据传输

EPP协议是一种与标准并行口兼容且能完成双向数据传协议。该协议定义的并行口更像一个开放的总线,给用户提供了强大的功能和灵活的设计手段。

它有四个数据传输周期:数据写周期;数据读周期;地址写周期;地址读周期。数据周期用于主机与外设之间的传输数据,地址周期一般用于传输地址、通道、命令和控制信号。这引起周期也可以看成为两种不同的数据周期。

EPP模式最主要的特征之一是整个数据传输过程发生在一个ISAI/O周期内。也就是说,用EPP协议来传输数据,系统可以获得500K-2M字节/秒的传输率,即并口的外围设备有接近ISA总线插板的性能。利用联锁形式的握手信号,数据的传输由接口中最慢的设备来决定,既可以是主机,也可以是外设。这种“速率适应性”对主机和外设来说都是透明的。所有的并行口传输方法都利用了联锁握手信号。用这种方法,外围设备可以控制其本身操作所需的建立时间。同时由于EPP模式传输数据的过程简单易实现,所以我们决定采用双向并口的EPP传输模式来实现高速数据传输。

当并口向ADI公司的DSP芯片ADSP21060传输数据时,通过数据锁存器锁住一个字节的数据,然后给ADSP21060一个中断信号,使其读取数据;同样,当ADSP21060向并口传输数据时,先让锁存器锁住数据,再给并口一个中断,使其读取数据,这样就完成了数据的双向通信。可是,用这种方法,无论数据向哪一个方向传输,只能传一个字节就引起一次中断,再使PC机或ADSP21060读取,然后再传下一个字节,这就占用了CPU的大量时间,降低了CPU的工作效率。为此我们利用两个FIFO来提高CPU的工作效率。

EPP模式下基于FIFO实现高速数据传输

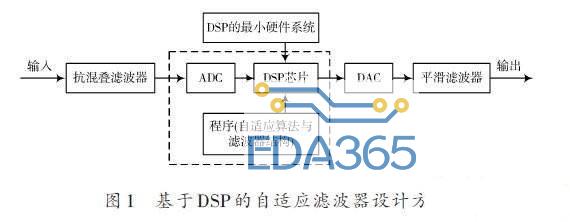

EPP模式下基于FIFO实现高速数据通信的原理框图见图1。

它的通信过程是:当并口向ADSP21060传输数据时,并口音先将输出FIFO复位,然后,将要传输的数据成批写到此FIFO中再给ADSP21060一个中断信号,通知它从输出FIFO读取数据;

当ADSP21060向并口传输数据时,首先将输入FIFO复位,然后,将要传输的数据成批写到此FIFO中再给计算机并口一个中断信号,通知它从输入FIFO读取数据,这样就完成了数据的双向通信。

这种设计具有块传输数据的优点,同时在传输大量数据时,占用并口和ADSP21060的时间非常少。

图中主要逻辑关系如下:

输出FIFO的读(AR)=RD and A0 and A1 and MS01;

输出FIFO的写(PW)=nWrite or nDstrb;

输入FIFO的读(PR)=not (nWrite)or nDstrb;

输入FIFO的写(AW)=WR and A0 and A1 and MS01。

在此电路设计中,有两个问题值得注意:

(1)nWait信号需要通过nDstrb和nAstrb的逻辑关系来产生。其逻辑关系为:nWait=not (nDstrb and nAstrb)。

(2)由于EPP和SPP兼容,在EPP模式下,需要将并口命令字中nWrite、nDstrb格nAstrb对应的位设置为无效。

计算机EPP并口程序设计

我们所选用的电可编程逻辑器件(EPLD)是Altera公司的EPM7128,关于它的详细介绍请参考Altera公司的器件手册,在这里仅给出AHDL语言写的控制程序如下:

FIFO存储器清零子程序,给FIFO送一个清零脉冲:void fifo_rst(void);设置命令字子程序:void command(void);写数据到FIFO子程序:void data_out (void);从FIFO读数据子程序:void data_in(void);

在访问EPP寄存器之前,软件必须写零到控制寄存器的0,1,3位;写数据时将指针ptr中的number个数据通过数据端口写入输出FIFO存储器中,然后引起ADSP21060中断;读数据时通过数据端从输入FIFO存储器读number然后将数据读到指针ptr中。

#define BASE_ADDR 0X378

#define ADDR_PORT 3

#define DATA_PORT 4

#define CONTROL_PORT 2

#define CONTROL_ININT 2

#define SET_BIT(x,b) ((x)=(1<

#define CLEAR_BIT(x,b) ((x)&=~(1<

void fifo_rst()

{

char control;

vontrol=inportb(BASE_ADDR+CONTROL_PORT);

CLEAR_BIT(control,CONTROL_ININT);

outportb (BASE_ADDR+CONTROL_PORT,control);

SET_BIT(control,CONTROL_ININT);

outportb (BASE_ADDR+CONTROL_PORT,control);

}

void command(void)

{

int com;

com=0;

control=inportb(BASE_ADDR+CONTROL_PORT);

control=control & oxf4;

outportb(BASE_ADDR+CONTROL_PORT,control);

}

void data_out(int number,char *ptr)

{

int i;

fifo_rst();

for(i=0;i

outportb(BASE_ADDR+ADDR_PORT,0);

}

void data_in(int number,char *ptr)

{

int i;

for(i=0;i

}

结论

本文给出了一种采用EPP模式下的FIFO和ADSP21060进行高速数据通信的实现方案。该电路能够完成ADSP21060和计算机并口的高速数据传输,且占用ADSP21060和计算机的时间非常少。另外,文中编制的子程序对于其他与PC机间进行高速数据通信的电路有参考价值。经调试证明此方案是可行的。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多