摘要:采用TMS320C54x芯片实现扩频通信系统中的核心进程——扩频编码与调制。该方案具有参数修改方便、简单易行,可根据实际信道要求迅速调整扩频增益和调制频率的优点。

关键词:DSP 扩频通信 卷积码 m序列

引言

TMS320C54x(简称"C54x)是TI公司于1996年推出的一种定点数字信号处理器。它采用先进的改进型哈佛结构,片内有8条总线、CPU、在片存储器和在片外围电路等硬件。它具高度专业化的指令系统,能够迅速地完成累加、乘积等运算功能。它具有功耗小、高度并行等优点,已被广泛应用于通信等众多领域。

本方案与常规的扩频实现方式相比,常规的扩频实现方式是用硬件来构造扩频通信系统,具有结构不灵活,调试不方便等不足之处。本方案充分发挥"C54x的强大功能,把直接序列(direct sequence)扩频通信中的m序列扩频和卷积编码等核心进程用软件予以实现;把扩频通信的核心算法用一片TMS320C54x芯片集成。它能够根据实际运用场合和传输信道的特征灵活更改参数,能最大限度地利用和发挥DSP芯片的优势,满足了高速数字通信系统中实时处理的要求,不但大大简化了系统设计,而且缩短了设计周期。

一、扩频通信

扩展频谱通信(spread spectrum communication),简称“扩频通信",是一种信息传输方式。其特点为:传输信号带宽远远大于发送出去的数字信息带宽。利用扩频技术,系统频率利用率比频分系统要高。

扩频技术是以仙农(shannon)公式作为理论基础而发展的。

仙农公式:C=W log2(1+P/N)

根据该公式可导出:在保持信息传输速度C不变的情况下,可以用不同频带宽度W和信噪功率比P/N来传输信息;如果增加频带宽度W,就可以在较低的信噪比P/N的情况下来传输信息,甚至在信号被噪声湮没的情况下,只要相应地增加信号带宽,也能保证可靠地通信。

按照扩展频谱的方式不同,现有的扩频通信基本方式分为:直序列(direct sequence)扩频、跳频(frequency hopping)、跳时(time hopping)、线性调频(chirp)以及上述几种方式的组合。

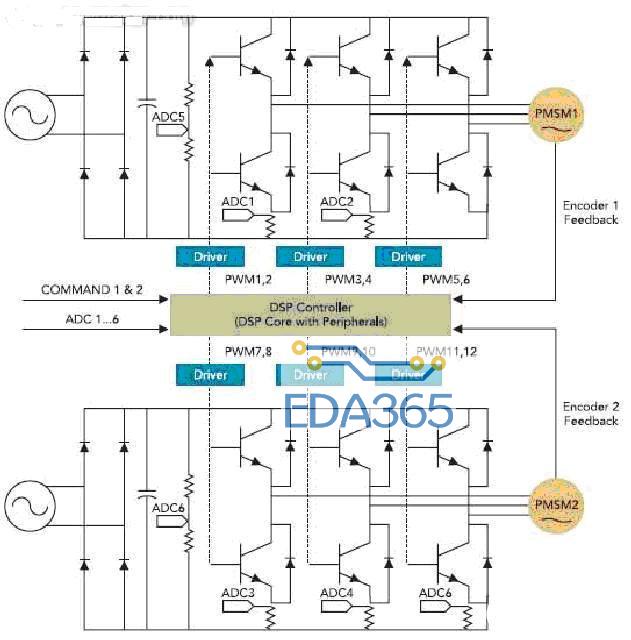

扩频通信的一般原理如图1所示。

在发端输入的信息先经信息调制形成数字信号,然后由扩频码发生器产生的扩频码序列去调制数字信号以展宽信号的频谱。展宽后的信号调制到射频发射出去。接收端则采用与发射端同步的代码进行相关检波,把被展宽有用频谱收集起来,所形成的信息码送给后端进行解码。

二、扩频信号的产生

结合考虑系统带宽、通信速率和研究的通用性以及实现的复杂性等因素,本方案确定采用直接序列扩频方法。该方法的原理框图如图2所示。

数据经过卷积码编码后,与伪随机序列发生器产生的扩频码序列进行模2加,产生的码序列通过调制器转换产生比数字信息的频谱宽得多的调制信号。系统中最重要的两个流程是编码器和伪随机序列发生器。本文采用TMS320C54x来实现这两个核心流程。

1.编码器

卷积码被广泛用于无线通信中的差错控制编码中,它的解码端可采用成熟的Viterbi解码算法。"54x芯片能够快速地执行算法所需的加一比一选操作(ACS指令)。实践证明采用卷积编码是一个良好的方法。

本方案中采用(2,1,5)的编码方案,相应的编码多项式为:

G1(D)=1+D3+D4 G2(D)=1+D+D3+D4

用TMS320C54x实现的程序片段如下:

start:STM #a0,AR1

RPT #4

MVPD table,*AR1+

STM #yn1_coef,AR1

RPT #4

MVPD table+5,*AR1+

STM #yn2_coef,AR1

RPT #4

MVPD table+10,*AR1

STM #a0,AR3

STM #yn1_coef,AR4

STM #yn2_coef,AR5

STM #5,BK

STM #1,AR0

LD #x,DP

PORTR PA1,*AR3 ;读入数字信息

CON:PRTZ A,#4

MAC *AR3+0%,*AR4+0%,A;

AND #1h,A

STH A,@yn1

PORTW @yn1,PA0 ;输出编码信息

RPTZ A,#4

MAC *AR3+0%,*AR5+0%,A

AND #1h,A

STH A,@yn2

PORTW @yn2,PA0 ;输出编码信息

BD CON

PORTR PA1,*AR3+0%

2.伪随机噪声序列产生器

最长线性反馈移位寄存器序列简称m序列,是一种最常用的伪随机序列。其序列长度为L=2n-1位,具有良好自相关性。一般由带有线性反馈的m阶线性移位寄存器产生。本研究利用DSP芯片特有的移位指令,代替原有的复杂电路,具有方便、简洁的优点。

这里实现的m序列发生器的本原多项式为x14+x10+x6+x+1,序列周期可达到32767位。

用TMS320C54x实现的程序片段如下:

strat:SSBX FRCT

STM #xn,AR1

ST #1,*AR1

RPT #12

ST #0,*AR1+

STM #a0,AR2

RPT #13

MVPD table,*AR2+

STM #14,BK

STM #xn,AR3

STM #a0,AR4

STM #1,AR0

LOOP:PORTW *AR3,PA0 ;输出PN码值

PRTZ A,#13

MAC *AR3+0%,*AR4+0%,A

AND #1,A

STL A,*AR3+0%

B LOOP

总结

该项目的优点在于它充分利用了TMS320C54x芯片优越的并行处理功能,在一片芯片上实现了卷积编码、频谱展宽以及多进制调制的整个过程。由于它采用软件实现,可以利用现有的成熟算法,如解码端采用维特比算法 ,因而最大限度地发挥了软件实现的优势。该方法被应用于水声信道的数据传输上。仿真实验证明是行之有效的。它可根据信道特征灵活修改参数、改变扩频增益、满足实际需求,缩短了整个开发周期。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多