ΣΔ调制器采用过采样和噪声整形技术,已经广泛运用在模数转换器(ADC)中,它避免了元器件失配对ADC精度的限制,能够实现高精度的ADC。ΣΔADC以速度换取精度,由于过采样的特性,使得ΣΔADC只能用在低速、高精度数字信号处理如音频处理等应用中,速度成为其更广泛应用的瓶颈。

多通道时间交织技术采用多个并行工作在低速的系统来实现高速系统,已经在NyquistADC(如pipelinedADC,FlashADC)中广泛应用[1]。对于M通道的NyquistADC,M个通道工作在M个不同相位的时钟下,如果每个通道的工作频率为Fs,则整个ADC转换速度为MFs,速度提高了M倍,实现了高速ADC。多通道时间交织技术是一种基于抽样率变换理论的技术,通过下采样和上采样来实现的。ΣΔ调制器采用过采样和噪声整形技术,在抽样率变换过程中,会出现信号频谱的混叠和镜像,所以,多通道时间交织的思想并不能直接应用到ΣΔ调制器中[2]。

本文从抽样率变换和滤波器组基本理论出发,通过多抽样率系统的恒等变换[3,4],推导了两通道滤波器组无混叠的条件。对传统ΣΔ调制器结构进行等效变换,得到两通道时间交织ΣΔ调制器的系统结构,理论上运算速度提高到单通道的2倍[5]。采用SIMULINK对二阶两通道时间交织ΣΔ调制器进行了建模仿真。

1 两通道滤波器组

[page]

则其等效的两通道时间交织结构如图2(b)所示,此时该系统还是一个不可物理实现的非因果系统(系统环路包含非因果项z)。把非因果项z与每个通道的z-1项合并,得到如图2(c)所示的等效结构。如果图2(a)的系统工作频率为Fs,图2(c)等效结构量化器的工作频率也为Fs。图2(c)所示结构可以进一步等效于图2(d)的结构,此时,除了采样电路和输出电路工作频率为Fs,其他电路全工作的频率是Fs/2。

[page]

3 两通道时间交织调制器结构及其仿真

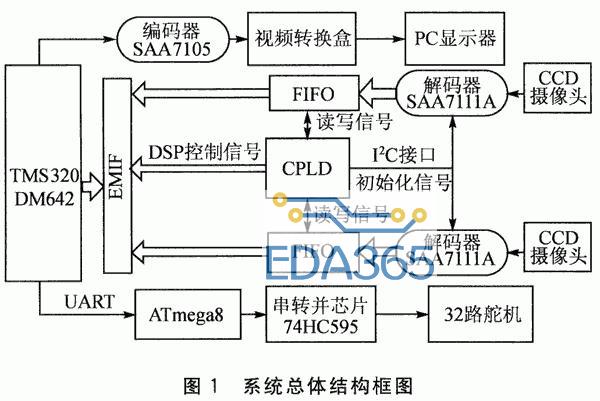

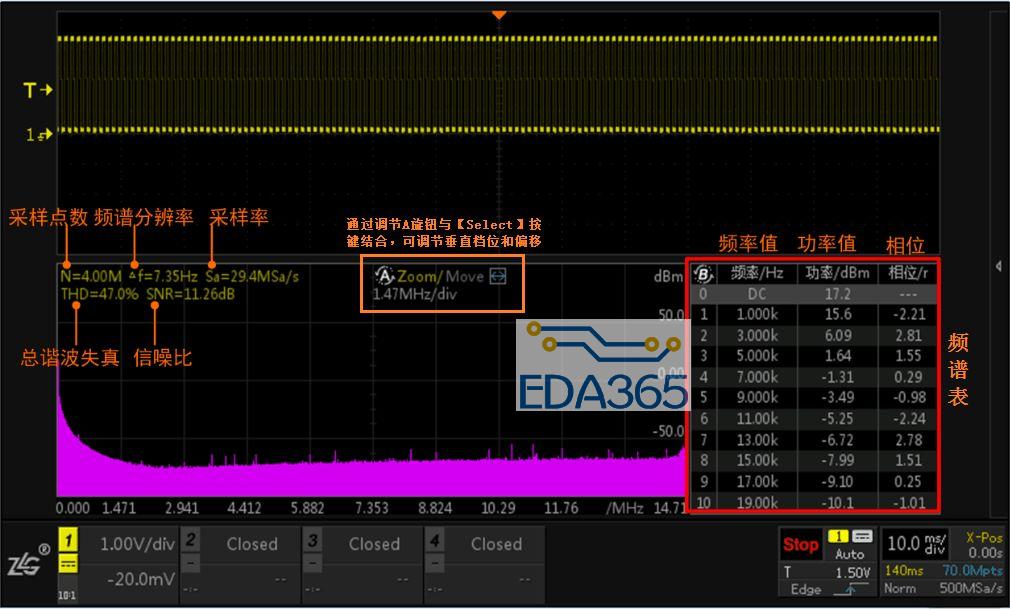

假设图3(a)的传统调制器工作频率为Fs=64MHz,图3(b)两通道时间交织调制器每个通道工作频率也为Fs=64MHz。采用SIMULINK分别对两种调制器结构进行建模仿真,输入信号为频率Fin=1.9921875e+005,幅值为-4dB满刻度幅度的正弦信号,内嵌ADC与DAC为1bit。两种调制器输出信号的功率谱如图4所示,从图4可以看出,两通道时间交织调制器结构具有更好的噪声整形效果。如果传统调制器结构和两通道时间交织调制器结构的每个通道的工作频率相同,并且信号带宽一样,则两通道时间交织调制器结构OSR为传统调制器结构OSR的2倍,即相当于OSR提高了1倍。理论上,假设调制器的量化噪声为白噪声,根据ΣΔ线性模型,可以得到,调制器的OSR每提高1倍,其SNDR增加(6L+3)dB,其中L为调制器的阶数[7]。图5(a)为传统调制器的OSR=64,两通道时间交织调制器的OSR=128,即两种调制器的信号带宽一样时,两种调制器的SNDR与输入信号幅值的关系。图5(a)表明,两通道时间交织调制器的SNDR比传统调制器提高了大约15dB,这与理论值相符。图5(b)为传统调制器的OSR=64,两通道时间交织调制器的OSR=64,即两通道时间交织调制器的信号带宽为传统调制器的两倍时,两种调制器的SNDR与输入信号幅值的关系。从图5(b)可以看出,当两通道时间交织调制器的信号带宽为传统调制器的2倍时,其SNDR几乎不变。这表明两通道时间交织调制器的速度能提高1倍,而其精度不变。

本文在两通道滤波器组无混叠的条件下设计了一种二阶两通道时间交织ΣΔ调制器,并采用SIMULINK对其进行了仿真。仿真结果表明:在不提高每个通道工作频率的条件下,调制器的信号带宽增加两倍,调制器精度几乎不变,相当于调制器的速度提一倍;如果保持信号带宽相等,其SNDR能提高大约15dB。在本文的基础上,可以进一步对多通道时间交织ΣΔ调制器结构进行研究与设计。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多