1 引言

一些设计、生产年代较早的非相参常规脉冲雷达因其数据处理能力不是很强而使得雷达的回波在经过检波后存在视频积累,而这种视频积累以前主要依靠显示器荧光屏及雷达操从员的眼、脑来识别和检测。这种人工观测存在主要缺点是掌握目标的批次有限,容易疲劳。针对以上缺点,笔者在某型常规脉冲雷达系统中增加了自动检测功能,其中一个重要的内容是门限检测,也就是将视频信号与一门限电平进行比较,以将其量化成数字信号来判定目标的有无,而门限值是根据恒虚警率的要求来设计的。另外,由于自动检测并能剔除噪音所形成的虚假目标,这样对后续雷达数据处理会造成影响。为此笔者在对量化噪音电平进行具体分析的基础上,专门设计了数字脉冲宽度鉴别电路,从而对进一步剔除量化后噪音电平起到了明显的作用。

2 数字脉冲宽度鉴别电路原理与实现

经过对比较器噪音电平的分析,发现其存在着没有周期性,随机出现,而且脉冲宽度较窄的特点,其脉冲宽度一般在20ns(因为所用比较器LM360的输出最短建立时间为20ns)至200us之间。由于所研究雷达的发射脉冲宽度为700ns,而回波信号的宽度一般大于500ns。所以可以利用真实回波与噪音信号在脉冲宽度上的差别,采用本文所介绍的脉冲宽度鉴别电路来滤除掉脉宽在320ns以下的数字信号。

数字脉冲宽度鉴别电路可通过可编程器件实现。设计的电路中采用的是Lattice公司的ispLSI1016E-80LJ。该器件的特点如下:

●包含2000个逻辑门:

●内含96个寄存器、32个输入输出I/O以及4个专有输入;

●输入、输出信号与TTL电平兼容;

●具有电擦除和在系统可编程。

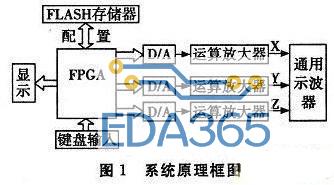

图1是此器件的引脚功能图。

该器件所用的开发工具是ispEXPERT,支持原理图与语言输入,可对设计进行高效适配,并可进行功能、时序的仿真,以缩短设计时间。

本文利用原理图输入的方式来完成电路的设计,其具体的数字脉冲宽度鉴别电路原理如图2所示。该电路主要由16位串入并出移位寄存器、16输入与门和D触发器组成。

对于脉冲宽度小于320ns的数字信号,移位寄存器的输出端不可能全部为“1”(高电平),也就是说有“0”(低电平)存在。这样,经16输入与门后亦为“0”输出,因而不能触发D触发器(FD21),从而使其输出端不会有“1”输出。

当输入信号的高电平宽度大于320ns时,移位寄存器的输出端全部为“1”,这样经16输入与门后输出为“1”,从而触发D触发器以使其输出端输出为“1”。输入信号经过若干个50MHz时钟节拍(节拍个数取决于信号的宽度)后,使移位寄存器最后一位为“0”,并经反相器输出到D触发器的清除端(这里D触发器的清除端有效电平为“1”),此时触发器输出“0”,这样就完成了信号宽度鉴别,从而将高电平宽度低于320ns的信号滤除。并使输入与输出信号的延迟时间为320ns,而其延迟时间则可由后续的数据处理程序在软件上加以补偿。

设计时,可以根据需要增加或减小移位寄存器的位数来滤除任意宽度的信号,例如要滤除宽度小于500ns的信号,就需将移位寄存器的位数增加至25位。

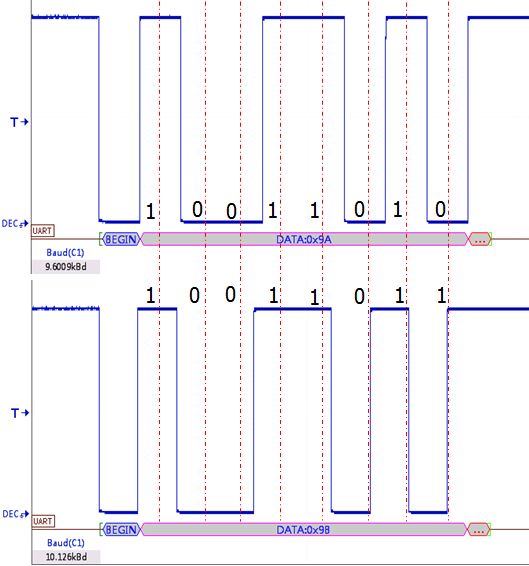

为了保护设计的正确性,可利用Lattice Logic Simulator软件工具对电路进行逻辑仿真,图3所示为仿真波形示意图。

从图中可以看到:输入信号中存在5个脉冲宽度小于320ns的脉冲,这些脉冲将被认为是噪音干扰,在经过脉冲宽度鉴别器后这5个脉冲将全部被滤掉,而输入信号中宽度大于320ns的信号将不受损失,只是增加了延迟时间而已。

3 结束语

将此利用iSPLSI 1016F设计的数字脉冲宽度鉴别电路应用在雷达视频量化之后,极大地降低了噪音的干扰,减少虚假目标的产生,增强目标的可信度,从而提高了雷达数据处理的速度。因该电路由可编程器件实现,故整体结构紧凑,可靠性高,具有较强的实用性。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多