本文的电源芯片指DC-DC和LDO芯片。

EN即enable,意为使能,指的是激活该管脚,电源芯片才会有输出。

在EN脚上设计不同的外围电路,可以实现电源芯片多种上电功能,别看一个小小的EN管脚,设计不好,同样影响电源芯片的正常工作。

接下来一起看一下EN管脚有那些玩法吧!

▉玩法1:EN脚悬空

某些DC_DC的ENpin支持悬空使能,也就是说EN不用接任何器件,只要有输入,就会有输出。

为什么悬空也能使能?

带floattoenable的DC-DCEN管脚内部会有一个内置上拉源接到输入VIN上,在EN脚悬空时,利用0.9uA的上拉源来开启电源。

▉玩法2:用CPU的GPIO控制EN管脚

通过单片机GPIO输出高低电平来开启/关闭DC-DC,一般ENpin会有一个阈值,超过这个值,开启DC-DC,低于这个值关闭DC-DC。

设计时建议预留两个分压电阻,提高兼容性,更换不同IO电压的CPU时可做到有的放矢。

但同时也要注意不能超过EN管脚耐压最大值。

▉玩法3:EN脚通过两个分压电阻接到VIN上

那有人说了,我不用CPU的GPIO控制,想上电DC-DC就有输出,可以通过VIN接两个电阻分压到EN管脚,这种多见于DC-DC芯片,一般VIN和EN电压不在一个水平上,VIN电压较高需要进行分压,见下左图。

VIN和EN处于同一电压水平的,这种多见于LDO芯片,可通过电阻R1上拉到VIN,见下中图。

或者VIN和EN直接短接相连,将R1换作一根导线,这个时候电源的开启和关系取决于VIN输入的UVLO阈值,见下右图。

▉玩法4:EN脚通过两个分压电阻调整UVLO阈值

通过分压电阻接到EN管脚的好处是可以设置DC-DC的启动电压和关闭电压,Vstart和Vstop电压值至少高于DC-DC的UVLO值,不然设置分压电阻没有意义。

UVLO的全称是undervoltagelockout,顾名思义就是低电压锁定,即欠压保护。

UVLO是针对DC-DC的输入VIN来说的,当电压低于某一定值,DC-DC直接锁定保护,UVLO限制了电源芯片的最低输入电压,一定程度上可以保证芯片不会产生不稳定的震荡,提高电源芯片工作时的稳定性和可靠性。

UVLO的阈值通常都是小于VIN最小输入电压值的,且是由芯片内部寄存器控制,在某些应用场合,如果不希望UVLO这么低,通过调整分压电阻阻值,可以设置电源启动电压和停止电压。

r1的计算公式为:

r2的计算公式为:

Vstart为启动电压,Vstop为关闭电压;

Vena为EN阈值电压;

Ihys为迟滞电流,I1为EN上拉源电流;

r1和r2为外部分压电阻;

要求不高,可以直接采用公式:

高于Vstart电源开启,低于Vstart电源关闭。

为使DC-DC稳定使能,可以将Vena设置为比其阈值大一些(介于阈值和其最大值之间即可),根据阈值和想要的开启电压,选择合适的r1和r2取值。

▉玩法5:EN脚外部加RC延时电路

某些电路有多个LDO,且LDO上电有时序要求,此时可以在ENPin上加RC,通过设置RC的大小,来满足要求,如下的VOUT1如果要求比VOUT2先上电,即可将R1C1参数设置比R2C2小即可。

EN管脚也可以换作用两个GPIO控制,利用两个GPIO的控制延时来满足时序要求。

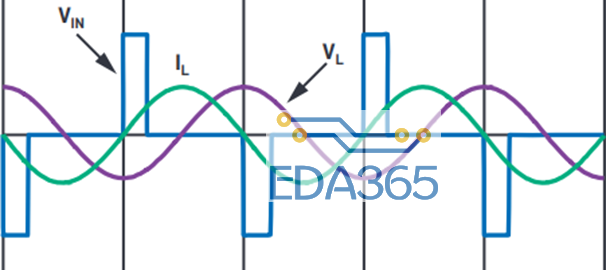

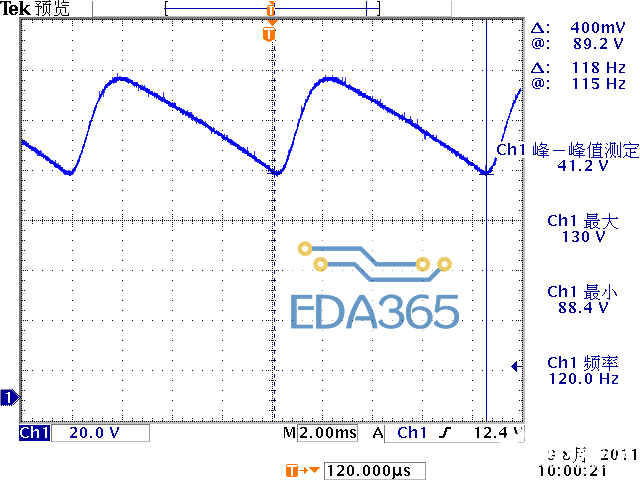

为避免一些场合输出电压受到刚上电时输入电压波动的影响(T1~T2),利用分压电阻或者RC延时电路,使输入电压上升到70~80%*VIN时,再开启使能EN(T2后),以得到更稳定的输出电压。

▉玩法6:多电源协同作战

有一些电路使用多种电源时,可以用上一级电源的PWRGD管脚来drive下一级电源的ENPin,达到有福同享有难同当的目的,即上一级电源开,下一级电源才开,上一级电源异常,下一级电源也无法开启(同时开,同时关),此电路也可以满足时序的要求,即VOUT2比VOUT1上电慢。

上图中的PWRGD是开漏输出,电源异常时,此脚会被拉低,指示电源是否good的管脚。

如下是EN1、PWRGD1、VOUT1、VOUT2的上电波形,可以看出,在前级电源完全上电之后,即PWRGD1管脚变为稳定的高电平时VOUT2才开始缓慢上升。

▉更多玩法等待你们解锁

介绍了这6种玩法,大家可以举一反三,还有很多EN管脚设计方法就不一一列举了,设计好EN管脚的目的就是为了相应功能的实现和电源芯片稳定可靠的工作。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多