人群的监控与监测已经成为当前的一个重要领域。政府和安全部门都已经开始寻求在公共场所智能监测人群的更先进的方式,从而避免在来不及采取行动之前检测到任何异常活动。但是在有效达成这一目的之前还需要克服一些障碍。例如,如果需要一天 24 小时同时监测整个城市里所有可能的人群活动,仅靠全人工监测是不可能的,尤其在安装有数千部 CCTV 摄像头的情况下更是如此。

这个问题的解决方案在于开发全新的智能摄像头或视觉系统,借助先进的视频分析技术自动监测人群的活动,从而能够立即向中央控制站报告任何异常事件。

设计这种智能摄像头/视觉系统不仅需要标准的成像传感器 和光学设备,还需要高性能视频处理器来执行视频分析工作。使用这种功能强大的板载视频处理器的原因在于先进视频分析技术具有较高的处理要求,大多数此类技术通常会使用计算密集型视频处理算法。

和光学设备,还需要高性能视频处理器来执行视频分析工作。使用这种功能强大的板载视频处理器的原因在于先进视频分析技术具有较高的处理要求,大多数此类技术通常会使用计算密集型视频处理算法。

FPGA 非常适合于此类高性能要求的应用。借助赛灵思Vivado Design Suite 中高层次综合 (HLS) 功能实现的 UltraFast 设计方法,现在可以为 FPGA 轻松创建理想的高性能设计。此外,赛灵思 MicroBlaze等嵌入式处理器与 FPGA可重配置逻辑的完美融合,让用户现在能够将具有复杂控制流的应用方便地移植到 FPGA 上。

鉴于这种情况,我们使用 Vivado HLS、赛灵思嵌入式开发套件 (EDK) 和 ISE Design Suite 中基于软件的EDA工具,设计出一种用于人群运动分类和监测系统的原型。这种设计方法基于我们所认为的软件控制和硬件加速架构。我们的设计采用低成本的赛灵思 Spartan-6 LX45 FPGA。我们在较短时间内即完成了总体系统设计,其在设计的实时性能、低成本和高灵活性方面均展现出颇有前景的结果。

系统设计

总体系统设计分两个阶段完成。第一阶段是开发人群运动分类算法。在这个算法的验证完成后,接下来是把它实现到 FPGA 中。在开发的第二阶段,我们主要关注基于 FPGA 的实时视频处理应用的架构设计方面。具体工作包括开发实时视频流水线、开发硬件加速器,最后将二者集成并实现到算法控制和数据流中,从而完成系统设计。

下面介绍每个开发阶段,首先从简要介绍算法设计开始,然后详细介绍如何将算法实现到 FPGA 平台上。

算法设计

就人群监视和监控而言,文献中提出了多种算法。大多数此类算法从在人群场景中检测(或布置)特征点

开始,然后随时间推移跟踪这些特征点,采集运动统计数据。随后把这些运动统计数据投射到一些之前预先计算好的运动模型上,用来预测任何异常活动 。进一步改进包括聚集特征点,跟踪这些集群而非单独的特征点。

本文的人群运动分类算法基于相同的概念,除了我们优先使用模板匹配方法进行运动估计,而不是采用 Kanade-Lucas- Tomasi (KLT) 特征跟踪器等传统方法。该模板匹配方法经验证表明,增加一些计算量能显著改善低对比度或对比度不断变化情况下的运动估计。

为将这一方法用于运动估计,我们将视频帧划分为更小矩形贴片组成的网格,然后使用基于加权绝对差之和 (SWAD) 的方法对每个贴片的当前图像和之前图像进行运动计算。每个贴片相应地提供一个运动向量,用于说明该特定位置两帧之间的运动范围和方向。结果就是需要在整个图像上计算超过 900 个运动向量。计算这些运动向量涉及的具体步骤如图1所示。

图1:计算运动向量的步骤,从图像采集开始(上)

此外,我们使用加权高斯内核实现图像中遮挡区和零对比度区的可靠性。而且,用于计算一个运动向量的一个贴片处理工作独立于其它贴片的处理工作,因此该方法非常适合使用 FPGA 上的并行实现方案。

在计算完整个图像上的运动向量后,该算法随即计算它们的统计属性。这些属性包括平均运动向量长度、运动向量数量、运动的主导方向和类似指标。

另外我们还计算了运动向量方向的 360 度柱状图,进一步分析其标准偏差、平均偏差和偏差系数等属性。这些统计属性随后被投射到预先计算好的运动模型上,从而将当前运动分类到几大类别之一。随后我们运用多个帧来解释这些统计属性,从而确认分类结果。

预先计算好的运动模型采用加权决策树分类器的形式构建,其充分考虑了这些统计属性来对所观察到的运动进行分类。例如,如果观察到运动速度快而且场景中有动量突变,同时运动方向随机或超出图像平面,就可以分类为可能的恐慌情况。该算法的开发工作使用微软 Visual C++ 配合 OpenCV 库完成。算法的完整演示请参阅本文文末提供的 Web 链接。

FPGA 实现方案

系统设计的第二阶段是该算法的 FPGA 实现过程。这一步实现工作有自己的设计难题,例如 FPGA 设计现在要包括视频输入/输出和帧缓存。此外,有限的资源和可用性能可能需要必要的设计优化。

鉴于这些设计特点和其它架构考虑,整个 FPGA 实现方案被分为三个部分。第一部分是在 FPGA 上开发通用的实时视频流水线,用于处理必要的视频输入/输出和帧缓存。第二部分是开发算法专用硬件加速器。最后在设计的第三阶段,我们把它们集成到一起,实现算法控制和数据流。这就完成了整个基于 FPGA 的系统设计。

下面对这个过程的每一阶段进行更详细的介绍。

实时视频流水线

在为 FPGA 平台开发任何视频处理应用时,实时视频流水线都是最重要的构建模块。这个流水线对用户隐藏了视频输入/输出和帧缓存相关的复杂存储器管理工作,而是提供了简单的访问界面以供用户处理视频帧数据。

虽然在这方面目前有几种先进的、商业许可的视频流水线,我们选择构建针对这个用途的定制视频流水线。我们基于赛灵思 EDK 构建该流水线,使用定制视频采集/显示端口处理视频输入/输出数据。这个流水线也可以方便地进行配置,从而用于其它赛灵思 FPGA 系列。

视频采集端口负责解码来自视频 ADC 的输入视频流数据并在本地缓存。随后该数据被转发至主存储器,用于创建视频帧。与此类似,视频显示端口负责对本地缓存中存储的视频帧数据进行编码,然后将其转发到视频 DAC 中供显示使用。视频输入输出端口连接到 MicroBlaze 主机处理器的主外设总线,该处理器负责处理与主存储器之间的视频数据流量。

视频端口能够生成中断,以通知 MicroBlaze 处理器在视频输入端口有可用的新数据或视频输入端口需要新数据。两种视频端口采用“往复式”缓存管理方案,这样即使是 MicroBlaze 处理器都无法立即响应视频端口,也不会发生缓存溢出或欠载。图2所示是视频端口与 MicroBlaze 处理器之间的互联。

图2:视频端口及其互联

视频端口设计用于检测和生成视频行数量、场 ID(如果是隔行视频)和视频输入/输出流中的其它控制信息。当有足够数量的视频数据被视频输入端口缓存,或当视频显示端口请求的数据达到足够数量时,该信息就会通过视频端口的中断服务例程 (ISR) 传递给 MicroBlaze 处理器。这些服务例程相应地通过 DMA 完成视频端口本地存储器和主存储器之间的视频数据传输。

除了视频端口 ISR,还有我们称之为“视频帧队列 API”的一套高级视频帧队列管理功能在这些 ISR 和用户层应用之间工作。该 API 负责维持多个采集帧和显示帧的队列,以支持双帧或三帧缓存方案。在MicroBlaze上运行的用户应用能轻松获得视频采集帧,或利用“视频帧队列 API”功能提供视频显示帧。图 3 显示了在层级结构中各级别的相关功能。

图3:视频端口 ISR 和视频帧队列 API 功能

将 MicroBlaze 用作主机处理器以连接系统中的各个构建模块能产生众多优势。例如我们可以使用 MicroBlaze 方便地连接各种外部存储器(SRAM、SDRAM 等),加载或存储来自视频端口的视频帧数据。类似地,我们可以使用 EDK 中的 DMA 控制器,在视频端口和主存储器之间传输视频数据。此外,我们还可用 MicroBlaze 处理器以同样方式连接定制硬件加速器。

这些“视频帧队列 API”功能加上视频端口 ISR 和视频输入输出端口让设计中的视频处理流水线的构造更加完善。图 4 所示的是使用 FPGA 上的本视频流水线采集、处理和显示实际的视频帧。它还显示了通过计算出的运动向量缩小视图实现的画中画功能。

图4:右下被运动向量网格覆盖的、经过 FPGA 处理后的实际帧

基于 Vivado HLS 的硬件加速器

在前文介绍的人群运动分类算法中,最为耗时、计算最密集的工作是计算运动向量。另一项系统工作——进行分类——因不涉及像素级的处理,非常简单而且易于实现。注意到设计的这个方面,我们为计算运动向量构建了一个硬件加速器。我们借助赛灵思 Vivado HLS,用 C/C++ 语言在 RTL 中对该加速器进行了设计、测试和综合。

Vivado 生成的 RTL 代码的关键特征之一是其在很大程度上已经过了精心优化。Vivado HSL 把阵列存取(例如存储在阵列中的像素数据)综合到存储器接口中,通过分析代码自动生成所需的地址。Vivado HSL 还可分析预先计算好的偏移和常量,从而非常快速地执行所谓的“跨步式”存储器访问。跨步式存储器访问从图像的多行数据访问开始(就如同在 2D 卷积中)。

设计基于 Vivado 的加速器的主要考虑因素是并行处理运动向量的计算,最大限度地提高从主存储器中的数据读取。为此目的,我们使用八个 Block RAM 并行加载和存储视频帧数据。硬件加速器的内核能够并行计算四个运动向量,而且在计算中它会用到所有八个 Block RAM。从主存储器传输到这些 Block RAM 的数据由 MicroBlaze 通过 DMA 加以控制。

Vivado HLS 生成的硬件加速器具有部分自动生成的握手信号,这些信号对于启停硬件加速器必不可少。这些握手信号包含“启动”、“繁忙”、“闲置”、“完成”等标志。这些标志通过 GPIO 传送到 MicroBlaze 处理器以完成握手。图 5 所示为该硬件加速器、八个 Block RAM 和 MicroBlaze 处理器主外设总线之间的互联。

图5:基于 Vivado HLS 的硬件加速器及其互联

图 5 中分别被命名为 SA1、TA1 到 SA4、TA4 的这些 Block RAM,每个的容量为 16KB。每对 SA1、TA1 到 SA4、TA4 能够保存计算一个完整行的运动向量所需的数据。因此硬件加速器在完成运行后,会输出四行运动向量写回到相同的 Block RAM 存储器中。这些计算完的运动向量随即由 MicroBlaze 处理器读回,然后把结果以运动向量网格的形式复制到自己的主存储器中。(图 4 所示的是被硬件加速器计算出的运动向量网格覆盖的实际帧)。该硬件加速器在 200MHz 频率下工作,计算整个图像的运动向量所需的全部处理任务能够在不足 10 毫秒内完成,包括与存储器之间的所有数据往来传输。

算法控制和数据流

在视频流水线和硬件加速器开发就绪后,完成该系统的最后一步是把这两个单元与 MicroBlaze 主机处理器集成,并使用赛灵思软件开发套件 (SDK_,用 C/C++ 实现用户层应用的算法控制和数据流。在赛灵思 SDK 中实现算法控制和数据流能为设计带来极大的灵活性。这是因为用户可以用相同的方式设计和集成新的硬件加速器,同时还可以修改必要的控制和数据流以集成新的硬件加速器。最终得到的就是一种软件控制、硬件加速的设计,其灵活度可媲美纯软件实现方案,同时其性能可媲美纯硬件实现方案。

本文介绍的人群运动分类算法的控制和数据流从通过视频帧队列 API 功能采集视频帧开始。当视频帧获取完毕,用户应用把当前的和之前的视频帧数据传输到硬件加速器,完成运动向量的计算。

此时系统在软件中计算运动向量的统计属性和分类结果。这样做的原因是这些步骤不涉及任何像素级处理,只会增加很少的处理开销。当分类结果计算完成时,用屏幕显示(OSD)功能把结果和运动向量显示在处理后的帧上。这些屏幕显示功能也是在赛灵思 SDK 中用 C/C++ 语言实现的。

这些构建模块(实时视频流水线、硬件加速器和算法控制/数据流)全部就绪后,总体系统设计即告完成。随后我们对基于 FPGA 的实现方案进行了测试,并与之前的桌面 PC 型实现方案比较结果的准确性。两个结果是完全一致的。我们使用来自明尼苏达大学数据库(/zixunimg/eepwimg/mha.cs.umn.edu /proj_recognition.sht-ml)和来自www.gettyimages.com的各种测试视频对本系统进行了测试。

实现方案结果

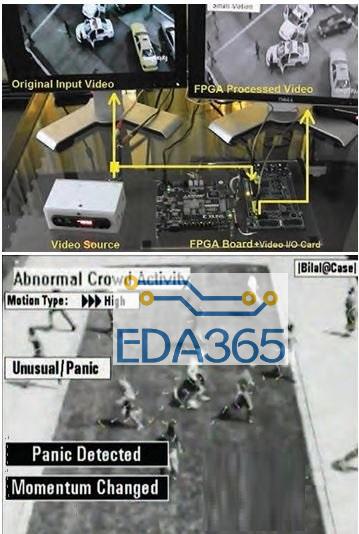

整个设计只使用了 Spartan-6-LX45 FPGA 上 30% 的Slice LUT、60% 的 BRAM和12% 的 DSP48E 乘法器资源。图 6 所示是硬件设置(上)和实际系统输出。硬件设置由 Digilent Atlys Spartan 6 FPGA 板和定制视频接口卡组成,利用视频 ADC 和 DAC 可为 FPGA 提供视频输入/输出功能。

图6:硬件设置(上)和把场景分类为惊恐的实际 FPGA 处理后的帧

巨大的未来潜力

FPGA 是面向实时视频处理等需要高性能的应用的理想平台。开发这种应用要求进行一定的架构考量,以充分发挥所选 FPGA 的性能优势。此外使用 EDK 和 Vivado HLS 等先进工具,能够以比过去高得多的效率和更短的开发时间实现总体系统设计。

因此正如我们在本文中所展示的,利用上述工具在 FPGA 上实现性能关键型应用有着巨大的潜力。有这样成功运行的平台作为先例,我们期望把这一成果推广用于解决更多的技术问题,例如自动化交通监测、医院中的自动病患观察等更多的应用。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多