引言

超低失真和噪声的高性能、全差分运算放大器是支持 高速、高性能模/数转换器(ADC)实现高分辨率和较低总谐 波失真(THD)的关键所在。运算放大器,我们在本文中简称 为驱动器,在ADC的前端执行各种操作。驱动器处理缓冲 和幅值放大,将单端输入转换为差分输出并连接到ADC的 差分输入,通过其VOCM引脚上的电压设置调节ADC的共模 输入信号以及对信号进行滤波。

本文讨论如何有效保护ADC,不被运算放大器驱动器 引起的输入过压损害。新MAX44205为180MHz、低噪声、低 失真、全差分ADC驱动器,内置箝位功能,使驱动器输出 摆幅在ADC的规定电源范围内。硬箝位电路保护ADC不受 其输入上过压的损害;驱动器和ADC之间无需附加外部分 立式元件,即可实现箝位保护。与传统的保护二极管方式相 比,该设计既节省空间又节约成本。

1 ADC输入过压保护的重要性

高性能ADC的价格较高,系统设计者必须选择能够保 护ADC不受过压损害的驱动器。当今的18位/20位ADC使用 不超过3.3V的基准电压/电源电压,但ADC驱动器通常使用±5V双电源甚至更高电压。驱动器VSS引脚的负电压用于支 持整个ADC满摆幅输入信号摆动。其中有一个问题:根据 驱动器输入信号的不同,其输出会超过ADC的输入电源。如果我们不将驱动器输出电压箝位到ADC电源电压范围之内,会永久损坏ADC。

市场上的大多数ADC的两个电压轨的输入上都有ESD保护二极管,但这些二极管不能处理大于20mA至50mA的电 流,持续时间超过几秒即会永久损坏。甚至内部ESD二极管 上较长持续时间的漏电流也会损坏二极管和ADC。大多数设计者在驱动器输出上使用齐纳二极管或肖特基 二极管,限制ADC的输入信号摆动。这种箝位方案中,需要 四个分立式二极管和限流电阻。有一种替代方案。MAX44205 为180MHz、低噪声、低失真、全差分运算放大器驱动器,内 置箝位电路,将其输出摆幅限制在ADC电源范围之内。从而 能够保护ADC不受输入过压的损害。该驱动器的箝位功能省 去了四个附加分立式元件,节省PCB空间和成本。

2 用分立式元件实现箝位

设计者利用肖特基 二极管箝位ADC的输入 电压。 这是一种不错的 方法, 因为根据通过的 电流不同, 这些二极管 的最小正向压降为大约

0.25V至0.4V。使用肖特 基二极管有另外三项重 要优点:1.) 反向漏流非 常 小 ; 2 . ) 寄 生 电 容 较 小;3.) 反向恢复时间非常快。 在肖特基二极管

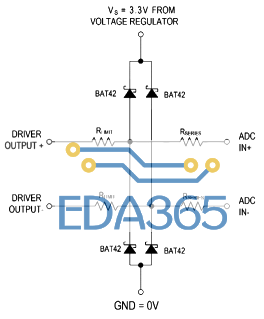

图1 利用肖特基二极管实现基本电压箝位的原理图

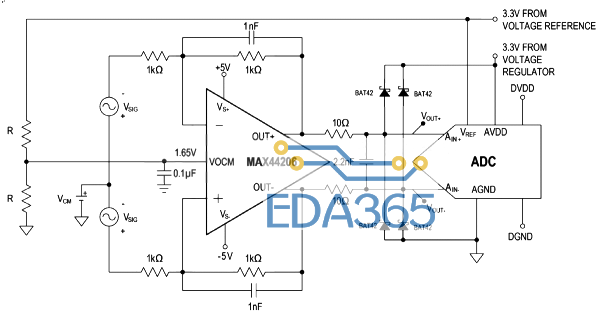

图2 使用四个外部肖特基二极管的箝位驱动器输出,保护ADC不受驱动器输出过压的损害

的三项优点中,低反向漏流和较小的寄生电容对于高精度ADC 应用非常关键。如果二极管开始箝位和退出箝位的速度非常关 键,那么第三项优点,快速反向恢复时间,就非常有用。

尽管肖特基二极管的寄生电容较小,但设计者必须选 择反向电压变化时电容变化最小的二极管。这种非线性效应 对于谐波失真非常重要的应用很关键。当箝位要求不太高时,也使用齐纳二极管进行电压箝 位。尽管可以使用,但齐纳二极管的反向漏电流较高,造成 其对ADC应用的效率较低。

图1所示为利用肖特基二极管将ADC输入箝位到预定电 压的基本方式。

图1中使用两个BAT42 Vishay ®肖特基二极管。ADC驱动 器输出超过ADC的正电源时,每路输出至正电源电压上的 两个肖特基二极管开始导通;二极管将这两个节点的电压维 持在3.3V加二极管正向压降。注意,根据二极管额定功率不 同,肖特基二极管的正向压降有所变化。所以,选择正向压

降指标较低的肖特基二极管,其正向连续电流指标要与应用相匹配。

四个电阻中,RLIMIT限制通过肖特基二 极管以及稳压器提供的3.3V电源轨的电流, RSERIES保护ADC的内部ESD保护二极管。设 计者必须调整这些电阻的大小,使电流保持 在满足具体应用的合理水平。

RLIMIT电阻也有助于减小流入到稳压器 即3.3V电源轨的电流。如果不限制该电流,稳 压器的输出电压会增大并损坏使用电路板上 相同稳压器输出的其它IC。如果您确认ADC 驱动器不会输出超过约100mA电流,有一种 替代方法。串联电阻不使用限流电阻。驱动 器和ADC之间的RC抗混叠滤波器将限制通过 外部肖特基二极管的电流,使其达到10mA左 右的合理水平。

所以同样,RLIMIT电阻有助于限制流 入3.3V电源轨的电流。此外,与肖特基二极 管电容一起,形成低通滤波器,将降低电路 带宽响应。对于需要较高带宽的ADC应用,这是一个问题,不利于ADC操作。

3 保护电路示例

外部肖特基二极管硬箝位

现在,我们介绍使用四个肖特基二极管的电路(图2), 保护ADC免受驱动器输出过压的损害。高性能16位至20位 ADC需要低噪声、低失真驱动器,以保证输入信号的质量 以及ADC的总体转换精度。本例中,一对7.5Ω电阻和一个

1nF电容组成抗混叠滤波器,提供21.22 MHz截断频率。为简 洁起见,我们不讨论如何确定低通滤波器元件的大小,本文 仅限于介绍ADC的过压保护。

图2所示为MAX44206运算放大器,配置为增益等于1V/ V的差分放大器配置,±5V双电源,VOCM = 1.65V。每路输 出通过直流电平转换至1.65V,也就是ADC的中间电压,以 充分利用ADC从0V至3.3V的完整转换范围。±5V双电源使 驱动器提供在0V至3.3V整个转换范围内摆动的输出电压。驱 动器输入上使用的输入信号通常幅值相等,相差180°,以 实现最大的差分输出信号摆幅。现在,每路输出直流电平转 换至1.65V,每路输出的幅值相等,基于输入信号摆幅,分 别相差180°。

图5 本电路中,不使用外部肖特基二极管或分立式元件对驱动器输出进行箝位

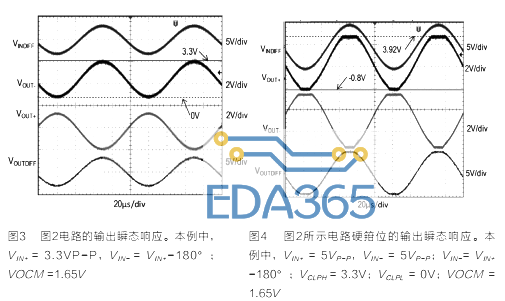

在我们的实验中,进行了两项测试:

1.每路输出上的电压摆幅设置为3.3VP-P,使用1.65VDC

偏置电压每路输入为3.3VP-P,相差180°,两路输入上的实际 差分输入电压(VINDIFF)为6.6VP-P。由于增益为1V/V,所 以每路输出也为3.3VP-P,相差180°,输出上的差分电压为6.6VP-P (图3)。

从图3的示波器曲线中可以看出,由于每路输出的最大 和最小电压分别为3.3V和0V,尚未启动箝位,如VOUT曲线 所示。这是可以理解的,二极管尚未导通来保护ADC。

2. 每路输出上的电压摆幅设置为5VP-P,使用1.65VDC

偏置电压每路输入为5VP-P ,相差180°(图4)。两个输入上的实 际差分输入电压(VINDIFF)为10VP-P。由于增益为1V/V,每 路输出则应为5VP-P,相差180°;输出上的差分电压应为10VP-P。每路输出在1.65VDC偏压下的5VP-P意味着输出摆 幅为4.15V至-0.85V。实际上,只要每路输出超过3.3V加二极管正向压降,二极管即打开,开始导通,将驱动器输出电压箝位到3.92V。类似地,二极管也将驱动器输出箝

位到-0.8V。

在图2的配置中,肖特基二极管导通的硬箝位 状态期间,消耗的电源电流大约为15mA。大多数 ADC的输入电压绝对最大额定值高于上轨0.3V以 及低于下轨- 0.3V。

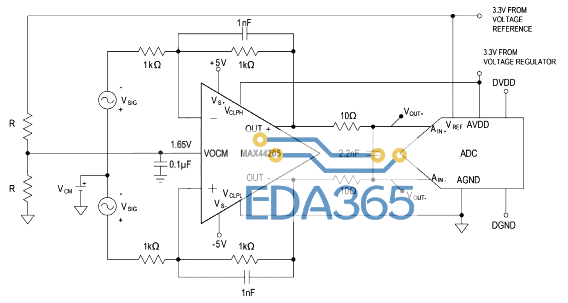

无外部分立式二极管硬箝位

现在,我们介绍不使用外部二极管的驱动器 输出过压保护电路(图5)。该方案不仅节省PCB空 间,也节省肖特基二极管的成本。图5所示的电路 与图2相同,但缺少了四个二极管。

图5中的MAX44205运算放大器有两个输出箝位引脚, VCLPH和VCLPL,可用于将输出电压限制到预设电压。将 ADC电源轨连接到这些箝位引脚时,驱动器输出被箝位到 ADC电源轨范围之内,与驱动器的输入电压摆幅无关。

同样,我们进行了两项测试:

1. 每路输出上的电压摆幅设置为3.3VP-P,使用1.65VDC

偏置电压

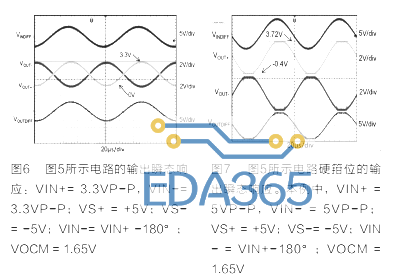

同样,每路输入为3.3VP-P ,相差180°(图6)。由于增 益为1V/V,每路输出也为3.3VP-P,相差180°。在示波器曲 线中(图6),驱动器每路输出的摆幅为3.3V至0V,与ADC电压轨严格相同,所以至此尚未进行箝位。

2.每路输出上的电压摆幅设置为5VP-P,使用1.65VDC

偏置电压

每路输入为5VP-P,相差180°;两路输入上的实际差 分输入电压(VINDIFF)为10VP-P,如图7所示。由于增益为

1V/V,每路输出也应为5VP-P,相差180°。同样,每路输 出在1.65VD C偏压下的5VP-P意味着输出摆幅理论上应为

4.15V至-0.85V。MAX44205运算放大器对输出进行箝位,将 其正向摆动限制到3.72V,负向摆动限制到-0.4V,如VOUT+ 踪迹所示(图7)。

MAX44205运算放大器拥有专利箝位方法,硬箝位状态 下通过VCLPL的耗流只有92µA。与图4所示分立式设计的毫 安级电流持续10s相比,这毫不逊色。MAX44205在箝位期间 的输出电压限值为VCLPH + 0.34和VCLPL - 0.42。不建议严 格箝位到ADC的电源轨,因为驱动器输出需要无失真摆动 到ADC的电源轨。如果将驱动器输出严格箝位到VCLPH和 VCLPL,箝位电路需要在输出等于ADC电源时打开,这将造 成失真。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多