【导读】电源完整性设计的水平直接影响着系统的性能,如整机可靠性、信噪比与误码率及EMI/EMC等重要指标。板级电源通道阻抗过高和同步开关噪声SSN过大会带来严重的电源完整性问题,这些会给器件及系统工作稳定性带来致命的影响。PI设计就是通过合理的平面电容、分立电容、平面分割应用确保板级电源通道阻抗满足要求,确保板级电源质量符合器件及产品要求,确保信号质量及器件、产品稳定工作。

电源噪声问题

随着超大规模集成电路工艺的发展,芯片工作电压越来越低,而工作速度越来越快,功耗越来越大,单板的密度也越来越高,因此对电源供应系统在整个工作频带内的稳定性提出了更高的要求。电源完整性设计的水平直接影响着系统的性能,如整机可靠性、信噪比与误码率及EMI/EMC等重要指标。板级电源通道阻抗过高和同步开关噪声SSN过大会带来严重的电源完整性问题,这些会给器件及系统工作稳定性带来致命的影响。PI设计就是通过合理的平面电容、分立电容、平面分割应用确保板级电源通道阻抗满足要求,确保板级电源质量符合器件及产品要求,确保信号质量及器件、产品稳定工作。

芯片内部有成千上万个晶体管,这些晶体管组成内部的门电路、组合逻辑、寄存器、计数器、延迟线、状态机、以及其他逻辑功能。随着芯片的集成度越来越高,内部晶体管数量越来越大。芯片的外部引脚数量有限,为每一个晶体管提供单独的供电引脚是不现实的。芯片的外部电源引脚提供给内部晶体管一个公共的供电节点,因此内部晶体管状态的转换必然引起电源噪声在芯片内部的传递。

对内部各个晶体管的操作通常由内核时钟或片内外设时钟同步,但是由于内部延时的差别,各个晶体管的状态转换不可能是严格同步的,当某些晶体管已经完成了状态转换,另一些晶体管可能仍处于转换过程中。芯片内部处于高电平的门电路会把电源噪声传递到其他门电路的输入部分。如果接受电源噪声的门电路此时处于电平转换的不定态区域,那么电源噪声可能会被放大,并在门电路的输出端产生矩形脉冲干扰,进而引起电路的逻辑错误。芯片外部电源引脚处的噪声通过内部门电路的传播,还可能会触发内部寄存器产生状态转换。

除了对芯片本身工作状态产生影响外,电源噪声还会对其他部分产生影响。比如电源噪声会影响晶振、PLL、DLL的抖动特性,AD转换电路的转换精度等。

电源噪声来源

绝大多数芯片都会给出一个正常工作的电压范围,这个值通常是±5%。例如:对于3.3V电压,为满足芯片正常工作,供电电压在3.13V到3.47V之间,或3.3V±165mV。对于1.2V电压,为满足芯片正常工作,供电电压在1.14V到1.26V之间,或1.2V±60mV。这些限制可以在芯片datasheet中查到。这些限制要考虑两个部分,第一是稳压芯片的直流输出误差,第二是电源噪声的峰值幅度。

电源系统的噪声来源有三个方面:

第一,稳压电源芯片本身的输出并不是恒定的,会有一定的波纹。这是由稳压芯片自身决定的,一旦选好了稳压电源芯片,对这部分噪声我们只能接受,无法控制。

第二,稳压电源无法实时响应负载对于电流需求的快速变化。稳压电源芯片通过感知其输出电压的变化,调整其输出电流,从而把输出电压调整回额定输出值。多数常用的稳压源调整电压的时间在毫秒到微秒量级。因此,对于负载电流变化频率在直流到几百KHz之间时,稳压源可以很好的做出调整,保持输出电压的稳定。当负载瞬态电流变化频率超出这一范围时,稳压源的电压输出会出现跌落,从而产生电源噪声。现在,微处理器的内核及外设的时钟频率已经超过了600兆赫兹,内部晶体管电平转换时间下降到800皮秒以下。这要求电源分配系统必须在直流到1GHz范围内都能快速响应负载电流的变化,但现有稳压电源芯片不可能满足这一苛刻要求。我们只能用其他方法补偿稳压源这一不足,这涉及到后面要讲的电源去耦。

第三,负载瞬态电流在电源路径阻抗和地路径阻抗上产生的压降。PCB板上任何电气路径不可避免的会存在阻抗,不论是完整的电源平面还是电源引线。对于多层板,通常提供一个完整的电源平面和地平面,稳压电源输出首先接入电源平面,供电电流流经电源平面,到达负载电源引脚。地路径和电源路径类似,只不过电流路径变成了地平面。完整平面的阻抗很低,但确实存在。如果不使用平面而使用引线,那么路径上的阻抗会更高。另外,引脚及焊盘本身也会有寄生电感存在,瞬态电流流经此路径必然产生压降,因此负载芯片电源引脚处的电压会随着瞬态电流的变化而波动,这就是阻抗产生的电源噪声。在电源路径表现为负载芯片电源引脚处的电压轨道塌陷,在地路径表现为负载芯片地引脚处的电位和参考地电位不同(注意,这和地弹不同,地弹是指芯片内部参考地电位相对于板级参考地电位的跳变)。

如何解决电源噪声-电容去耦

采用电容去耦是解决电源噪声问题的主要方法。这种方法对提高瞬态电流的响应速度,降低电源分配系统的阻抗都非常有效。

对于电容去耦,很多资料中都有涉及,但是阐述的角度不同。有些是从局部电荷存储(即储能)的角度来说明,有些是从电源分配系统的阻抗的角度来说明,还有些资料的说明更为混乱,一会提储能,一会提阻抗,因此很多人在看资料的时候感到有些迷惑。其实,这两种提法,本质上是相同的,只不过看待问题的视角不同而已。为了让大家有个清楚的认识,介绍一下这两种解释。

(1)从储能角度看电容去耦

在制作电路板时,通常会在负载芯片周围放置很多电容,这些电容就起到电源去耦作用。

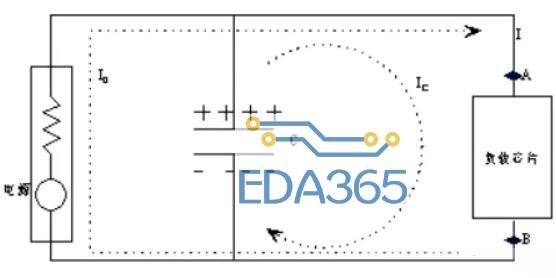

负载电流不变时,其电流由稳压电源部分提供,即图中的I0,方向如图所示。此时电容两端电压与负载两端电压一致,电流Ic为0,电容两端存储相当数量的电荷,其电荷数量和电容量有关。当负载瞬态电流发生变化时,由于负载芯片内部晶体管电平转换速度极快,必须在极短的时间内为负载芯片提供足够的电流。但是稳压电源无法很快响应负载电流的变化,因此,电流I0不会马上满足负载瞬态电流要求,因此负载芯片电压会降低。但是由于电容电压与负载电压相同,因此电容两端存在电压变化。对于电容来说电压变化必然产生电流,此时电容对负载放电,电流Ic不再为0,为负载芯片提供电流。根据电容等式:

要电容量C足够大,只需很小的电压变化,电容就可以提供足够大的电流,满足负载瞬态电流的要求。这样就保证了负载芯片电压的变化在容许的范围内。这里,相当于电容预先存储了一部分电能,在负载需要的时候释放出来,即电容是储能元件。储能电容的存在使负载消耗的能量得到快速补充,因此保证了负载两端电压不至于有太大变化,此时电容担负的是局部电源的角色。

从储能的角度来理解电源去耦,非常直观易懂,但是对电路设计帮助不大。从阻抗的角度理解电容去耦,能让我们设计电路时有章可循。实际上,在决定电源分配系统的去耦电容量的时候,用的就是阻抗的概念。

(2)从阻抗角度看电容去耦

将图中的负载芯片拿掉,从AB两点向左看过去,稳压电源以及电容去耦系统一起,可以看成一个复合的电源系统。这个电源系统的特点是:不论AB两点间负载瞬态电流如何变化,都能保证AB两点间的电压保持稳定,即AB两点间电压变化很小。

我们可以用一个等效电源模型表示上面这个复合的电源系统,如下图所示。

对于这个电路可写出如下等式;

总结

我们的最终设计目标是,不论AB两点间负载瞬态电流如何变化,都要保持AB两点间电压变化范围很小,根据公式,这个要求等效于电源系统的阻抗Z要足够低。在图中,我们是通过去耦电容来达到这一要求的,因此从等效的角度出发,可以说去耦电容降低了电源系统的阻抗。另一方面,从电路原理的角度来说,可得到同样结论。电容对于交流信号呈现低阻抗特性,因此加入电容,实际上也确实降低了电源系统的交流阻抗。

从阻抗的角度理解电容去耦,可以给我们设计电源分配系统带来极大的方便。实际上,电源分配系统设计的最根本的原则就是使阻抗最小。最有效的设计方法就是在这个原则指导下产生的。

APP下载

APP下载 登录

登录

热门文章

热门文章