蔡教授推断,忆阻器代表着电荷与磁通量之间的关系。忆阻器的电阻会随着通过的电流量而发生变化,就算电路断电、电流停止,其电阻值仍然会被保留,直到有反向电流通过才会返回原状。通过控制电流的变化可改变其阻值,如果把高阻值定义为“1”,低阻值定义为“0”,这种电阻就可以实现存储数据的功能。

忆阻器是下一代神经网络最有前景的硬件单元

大脑在许多方面都优于传统的计算机,脑细胞使用的能量更少、处理信息更快、更具有适应能力。人脑中的逻辑和记忆紧密关联,其密度和多样性是现代计算机的数十亿倍。对于下一代神经网络和神经形态计算来说,最有前景的硬件单元就是忆阻器。

荷兰格罗宁根大学的物理学家们在研究忆阻器时发现,他们利用系统切换电阻,通过施加电压脉冲控制电阻,并利用一个低电压,读出不同状态的电流,脉冲的强度决定了设备的电阻,实现的电阻比至少是1000,而且随着时间推移测量所发生的情况,电阻状态随时间发生变化。通过不同的方式“训练”设备,采用不同的脉冲,可以改变它的行为。电阻随着时间变化,就像人的大脑一样,可以将时间作为一个参数。

忆阻器的出现为科学工作者提供了一个具有全新电路行为的基本无源器件,与之相应的应用领域也蓬勃发展,忆阻器研究涉及微电子、凝聚态物理、材料学、电路与系统、计算机、自动化、人工智能和神经生物学等多学科领域,属于新兴交叉学科。

高指标测试结果推动忆阻器研究进程

目前,国内忆阻器研究在材料体系、物理机制、性能优化、规模集成、非线性电路和类脑神经形态计算等方面取得了令人鼓舞的进展,但在忆阻器可靠性、阵列的控制电路设计,以及CMOS集成工艺等方面还需要研究者和广大工程技术人员协同攻关,更需要针对忆阻器不同研究阶段的专业的测试系统保驾护航。

忆阻器备受关注的重要应用领域包括:非易失存储(Nonvolatile memory),逻辑运算(Logic computing),以及类脑神经形态计算(Brain-inspired neuromorphic computing)等。这三种截然不同又相互关联的技术路线,为发展信息存储与处理融合的新型计算体系架构,突破传统冯·诺伊曼架构瓶颈,提供了可行的路线。

忆阻器的基础研究测试

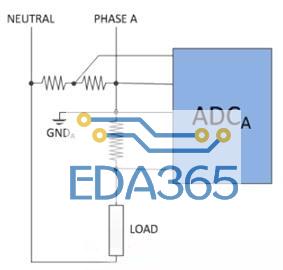

忆阻器基础研究测试系统需要包括交流特性、直流特性、脉冲特性测试,需集成信号源、高速任意波发生器、SMU、示波器功能于一身。虽然忆阻器基础研究的主要测试项目可以手动操作完成测试,但如果有自动化测试软件,还是可以大大提高测试效率的。

忆阻器性能研究测试

获得高性能忆阻器件,是将忆阻器推向应用的前提。虽然忆阻器研究已经取得很多成果,但距大规模商用还存在较大距离,其实现机理仍不清楚,可靠性不足,涨落大,模拟阻变特性需要优化。忆阻器主要应用于非易失存储、逻辑运算以及类脑神经形态计算,非易失存储是逻辑运算的基础。部分电阻状态保持不佳的忆阻器,类似人脑中信息短时程记忆的现象,可以用于神经形态计算。

尽管基于忆阻的非易失性存储器件的研究已经较为成熟,但要在功耗、擦写速度、集成度和可靠性等各方面性能指标上超越现阶段商用化存储器,还需要学术界与工业界共同努力。在逻辑运算和类脑神经计算应用虽已取得较大进展,但研究尚不系统、成熟。因此,对忆阻器性能的研究,主要目的是提高忆阻器存储性能和模拟神经元的性能。

非易失存储器性能测试。对非易失存储器性能研究的目的是提高忆阻器的循环次数或耐久力(Endurance)和数据保留时间(Data Retention)。对非易失存储器,数据保持能力是其最重要的电学可靠性,保留时间是存储器非常重要的一个性能指标。对一般的存储器,要求在85℃温度下保持十年的寿命,有统一的测试规范。然而对忆阻器而言,由于其机理研究还处于百家争鸣的状态,尚未建立统一的测试规范。目前对忆阻器的数据保留时间测试,主要基于高温老化测试法,并通过电阻阻值外延法和阿列纽斯方程(Arrhenius Equation)推导其数据保留时间。

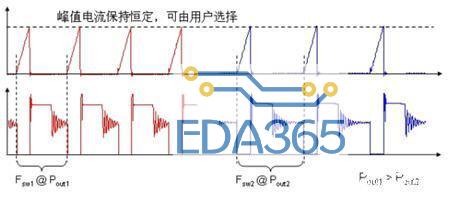

神经突触阻变动力学测试。忆阻器的导电态可以用来表示突触权重的变化 (导电性增加和减小分别对应突触权重的增大和减小),通过改变刺激脉冲电压的形状、频率、持续时间等参数来模拟不同突触功能相应的神经刺激信号的特点,测量瞬态电流可以了解阻变动力学过程,获得神经形态特性的调控方法。

基于交叉阵列的神经网络单元研究将是未来重要方向

忆阻器单元集成结构是实现集成忆阻器的关键,忆阻器的集成一般分为无源阵列与有源阵列两种类型。在无源阵列中,存储单元是由相互垂直的字线和位线交叉点阵结构组成的,存储功能层位于字线和位线之间。有源阵列一般通过采用场效应晶体管、二极管、选通其等有源器件,构成诸如1T1R、1TNR、1D1R、1S1R等结构,并在集成阵列中利用字线和位线来达到选通存储单元的目的。

阻变存储器测试面临最大的挑战是测试时间问题,因为阻变存储器阵列在擦写过程中需要对每个单元反复校验,以抑制涨落和弛豫效应对tail bits的影响。单器件的测试程序很容易开发,但是阵列级的验证自动测试方法则是未来急需的工具。为抑制串扰,还需要开发灵活的阵列测试系统,可以多通道同时加电压。

基于交叉阵列的神经网络单元研究将是未来相当长时间内的重要方向,神经网络最基本的操作是在所有WL上同时加不同幅值的电压,同时在所有BL上读取电流,需要输入多通道的模拟电压值,同时能够多通道同时读取模拟电流值。目前类似的过程都是靠电路或者FPGA完成的,灵活性差、周期长,不适合研发。通用阵列测试设备将大大提升研发效率。

支持忆阻器/神经元网络研究的测试系统

在忆阻器及神经元网络科研领域,吉时利的产品更是享有盛誉,其测试结果被全球权威学术期刊所认可。由于忆阻器/神经元网络测试 - 尤其是阵列测试,不仅仅需要高指标的测试仪器,更需要开发定制化的测试序列以满足复杂测试流程的需求,泰克公司中国研发中心可以为这一领域的客户提供定制开发及系统集成。

泰克忆阻器/神经元网络测试系统包含单元测试及阵列测试两大类,每一大类又包含不同的配置以满足不同研究阶段的测试需求。

泰克忆阻器/神经元网络测试系统的优势:同时提供忆阻器直流性能、交流性能、脉冲性能及高速脉冲性能测试;多种不同的配置方案,满足不同的客户需求;内置忆阻器性能测试、阻变动力学测试功能,可根据客户需求,定制开发特殊功能;提供阵列测试功能,可根据客户需求,定制开发;业内领先客户采用。

了解更多忆阻器测试细节,详见泰克忆阻器白皮书

关于泰克科技

泰克公司总部位于美国俄勒冈州毕佛顿市,致力提供创新、精确、操作简便的测试、测量和监测解决方案,解决各种问题,释放洞察力,推动创新能力。70多年来,泰克一直走在数字时代前沿。欢迎加入我们的创新之旅,敬请登录:tek.com.cn

责编:Demi

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多