【导读】信号沿传输线向前传播时,每时每刻都会感受到一个瞬态阻抗,这个阻抗可能是传输线本身的,也可能是中途或末端其他元件的。对于信号来说,它不会区分是什么,信号所感受到的只有阻抗。如果信号感受到的阻抗是恒定的,那么他就会正常向前传播,只要感受到的阻抗发生变化,信号都会发生反射。这些因素可能包括过长的走线,末端匹配的传输线,过量的电容或电感及阻抗失配。

本文要点:

1,介绍信号分列反射的具体表现;

2,结合具体电路分析。

信号沿传输线向前传播时,每时每刻都会感受到一个瞬态阻抗,这个阻抗可能是传输线本身的,也可能是中途或末端其他元件的。对于信号来说,它不会区分是什么,信号所感受到的只有阻抗。如果信号感受到的阻抗是恒定的,那么他就会正常向前传播,只要感受到的阻抗发生变化,信号都会发生反射。这些因素可能包括过长的走线,末端匹配的传输线,过量的电容或电感及阻抗失配。

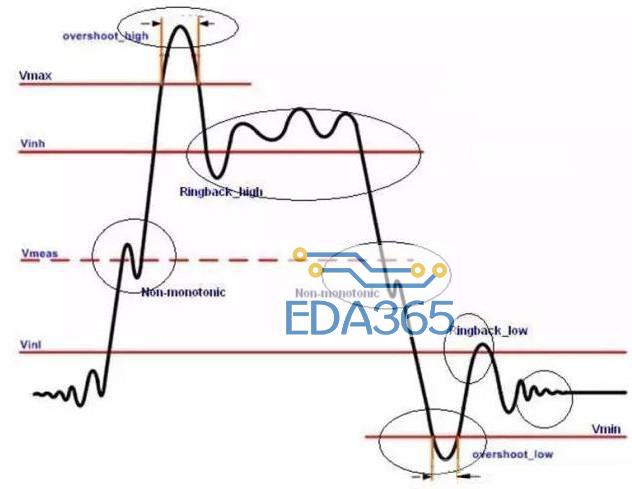

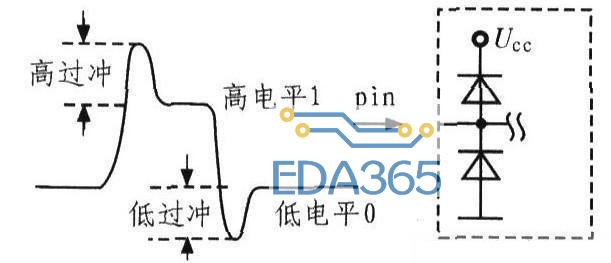

反射会造成信号过冲overshoot、下冲undershoot、振铃ringing、边沿迟缓也就是阶梯电压波。过冲是振铃的欠阻尼状态,边沿迟缓是振铃的过阻尼状态。当信号的第一个波峰超过原来设定的最大值。过冲是指信号跳变的第一个峰值或谷值,它是在电源电平之上或参考地电平之下的额外电压效应;

边沿迟缓我们也成为台阶,回勾现象,其危险主要是会造成误触发。

下冲是指信号跳变的下一个谷值或峰值。过冲与下冲都是不利的因素,过大的过冲电压经常长期性地冲击会造成器件的损坏,如上图所示。严重的下冲会超过接收器件的门限而导致电路的逻辑错误。

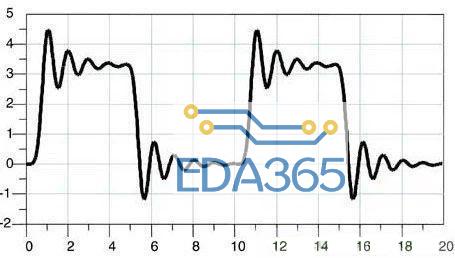

如果信号在驱动器和接收器之间来回多次反射,就会产生振铃现象,这增加了信号稳定所需要的时间,从而也影响了系统稳定的时序。

细节处如下图,

电路设计Tips:

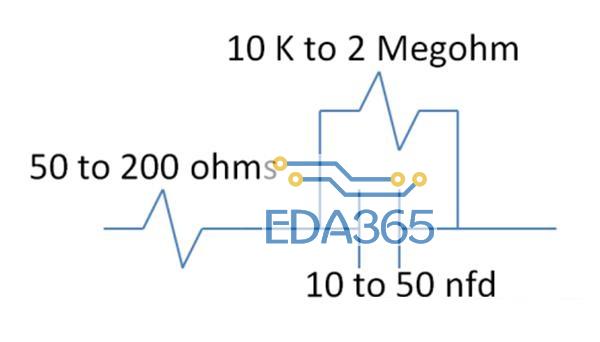

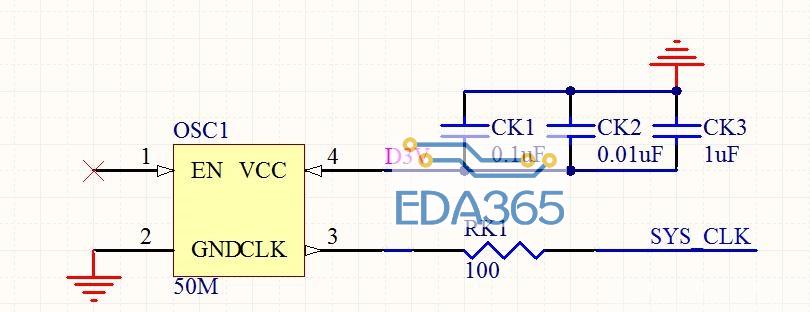

一般做电路设计中,如果时钟信号链路比较长,会在时钟输出信号上串接一个小电阻,比如22欧姆或者33欧姆。

至于为什么,很多成熟设计都是这么做,算是一个经验设计方法。实际上,其实这个小电阻的作用就是为了解决信号反射问题。而且随着电阻的加大,振铃会消失,但你会发现信号上升沿不再那么陡峭了,串联电阻是为了减小反射波,避免反射波叠加引起过冲。这个解决方法叫阻抗匹配,一定要注意阻抗匹配,阻抗在信号完整性问题中占据着极其重要的地位。

APP下载

APP下载 登录

登录

热门文章

热门文章