1. 整机原理图设计时各功能电路要区分明确,以便于电路分析。

2. 各部分是否尽量使用更低速的器件?(如74HC14的Tr=Tf=6ns而74AHC14的Tr=Tf≤3ns,这时我们就要考虑尽量选用74HC14而不是74AHC14.)

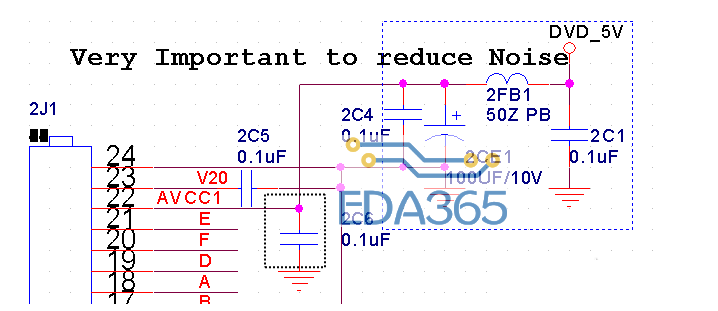

3. 对DVD机芯的干扰是否有EMI对策,原理图上要明确标注。

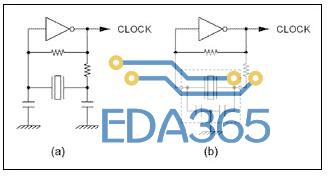

解释说明:DVD机芯的干扰主要是激光头电路本身产生的干扰(不同厂家的机芯干扰程度不一样),激光头的干扰通过较长的激光头扁平线形成天线辐射,所以要在电路上加小电容减少扁平线的天线效应,

如下图:

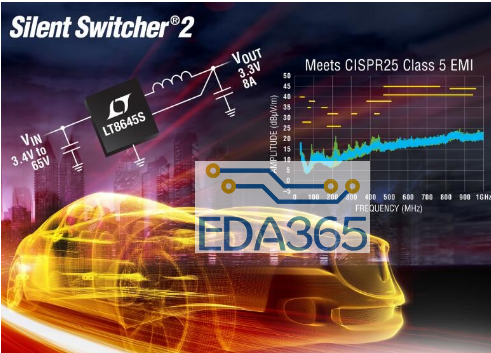

4. DVD机芯电源要有EMI对策,不但要明确标注而且要注明Layout 时的放置位置。

解释说明:由于激光头读取信息时电源瞬间变化所产生的干扰很大。机芯电源要求就近有能提供瞬态电流的电容。如下图虚线框内的EMI对策,有的机芯电路有好几个电源,每个电源都要有电容滤波,至少要有一个102---104的电容。

5. 原理图上要标注各功能块的工作电压,尤其是时钟信号工作频率要描述清楚?(如:解码芯片、RAM芯片、DC/DC等)

解释说明:原理图上标注清楚工作电压和信号频率不但有利于原理图的评审,对PCBLayout也有很大的指导作用。

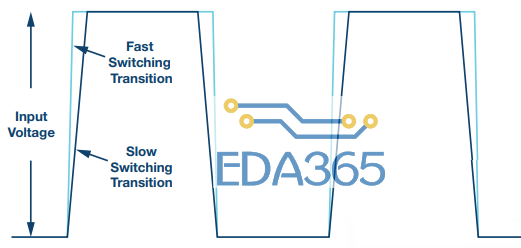

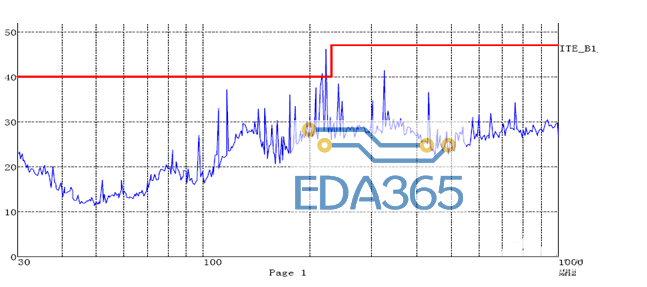

6. 对于干扰较大的3、5次谐波频率在230MHz左右的时钟频率能否调整?(要求F3、F5>230MHz+20MHz)

解释说明:因为CE辐射测试标准里有两个频率段(30MHz----230MHz和230MHz---1GHz),高段比低段要求低7Db。在EMC整改时要降7DB需要增加很多对策,尤其是针对LCD屏的干扰,我们很难对屏进行处理。

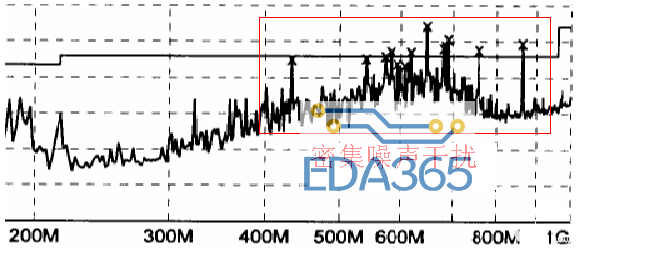

如下图有一个时钟的谐波在225MHz左右超标6db。如果时钟频率稍改大一点使其落在230MHz以后,那么EMC整改就容易多了。所以如果时钟频率能调的话,就尽量使干扰较大的频率其3、5次谐波大于230MHz。

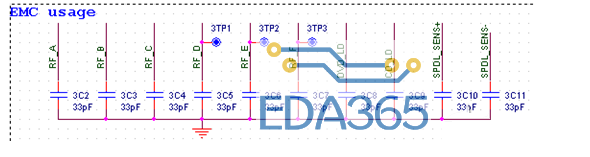

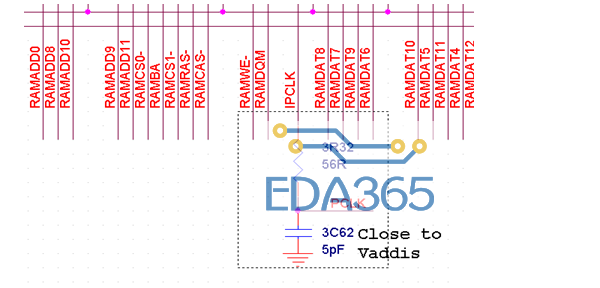

7. 对较高频率是否有EMI对策?如RAM时钟等。

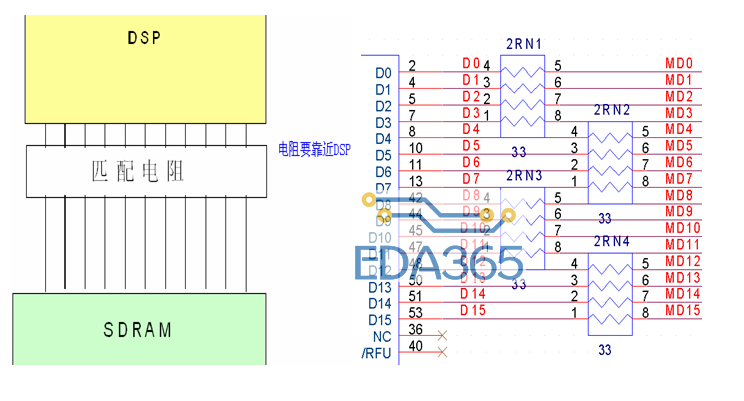

解释说明:工作频率比较高的时钟信号不但其产生的谐波辐射很大,其本身的基波辐射也很大,所以原理图上一定要有EMI对策。如MTK1389与DRAM的工作时钟, 频率为108MHz/128MHz/135MHz,在原理图上要串联电阻和并联电容到地。如下图所示。

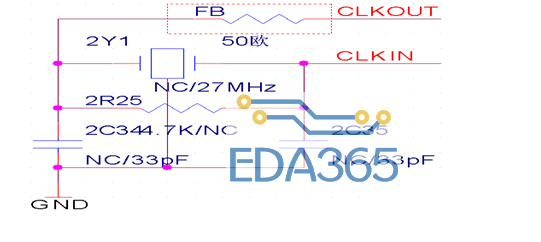

8. 振荡电路里晶振的输出脚要串联EMI磁珠。

解释说明:晶振的输出脚一般都会有谐波分量产生,EMI磁珠对高频信号存在很大的阻抗,使得时钟信号的基波通过,高频谐波分量被衰减,如下图虚线框内对策。

9. 地址/数据线要串联电阻。

解释说明:在EMI测试时常发现一些密集噪声干扰,如下图。密集噪声干扰与电路中的晶振、主频信号没有很大关系,属总线干扰。是因为总线匹配和布线的问题,适当调整匹配电阻,并在layout时有针对性地对地址/数据总线处理可有效减少总线上的干扰。见下图。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多