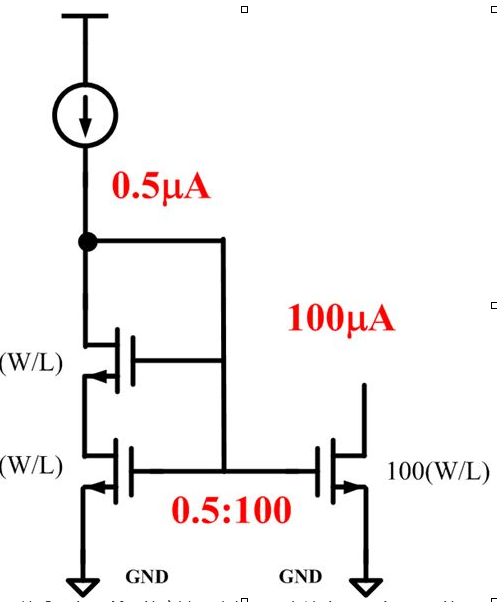

版图将会对模拟电路性能产生巨大的影响,针对matching要求很低,nmos的body-effect不可小视,current matching即使差到20%~40%,matching最后造成了接近50%的偏差,也就是差不多到了1:600。

当电流的matching不那么重要的时候,为了节省电流和面积,可以使用作者君采用的暴力巨大的ratio值。

然后还学了一招,针对matching要求很低的情况,为了节省面积:

可以采用上图所示的方法。当然了,左边上面那个nmos的body-effect不可小视,大家根据自己的实际情况掂量着用吧!

本人的design存在严重缺陷,因而才导致了下面将会谈到的这个问题,正常情况下的current ratio,大概会尽量保持在十以内。如果出现这样的情况:

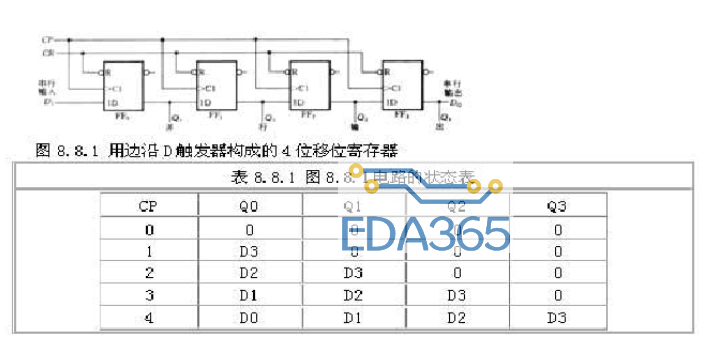

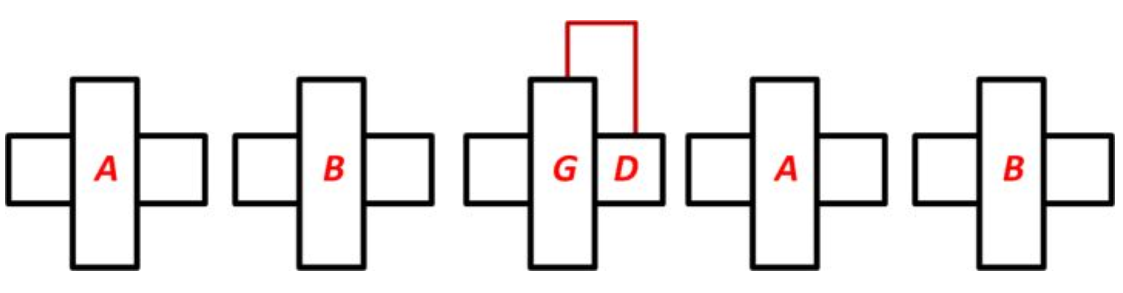

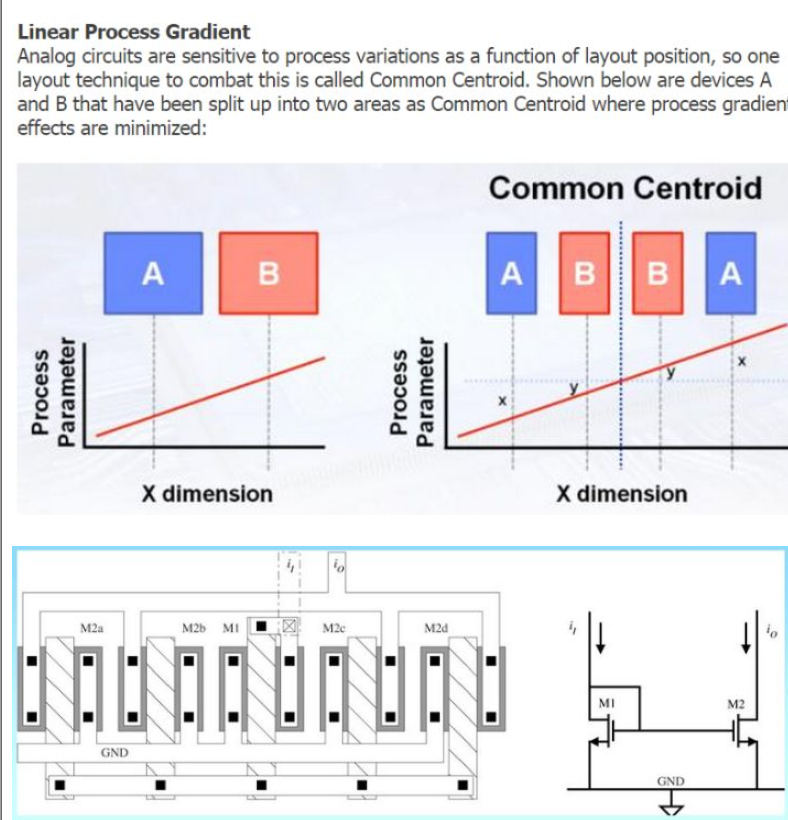

基于一般的经典common-centriod的layout结构:

而不是下面作者所采取的做法。

作者当时并不很担心自己的current matching,因为觉得即使差到20%~40%(1:400变成了1:240到1:560),都是可以忍受的。结果后仿的结果显示,matching最后造成了接近50%的偏差,也就是差不多到了1:600.

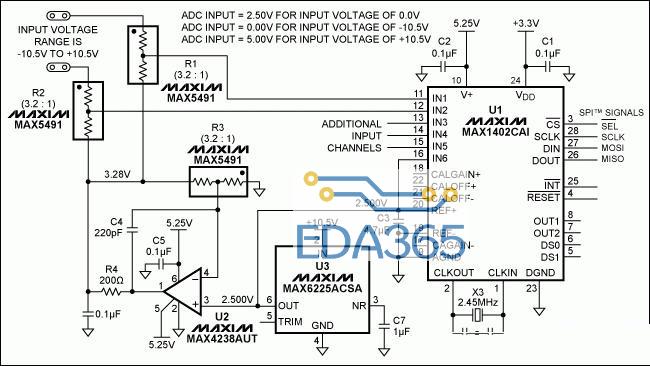

下面是一个comparator的pre-amplifier。

因为作者以前都是做low power的电路,很少遇到需要烧电烧到几百uA的情况。

所以上面那个200uA的pre-amplifier,让作者郁闷了一下下。

M59和M63的W/L ratio是1:400。

一开始做layout的时候,我们layouter问我,这个M59摆在哪里?

我当时没有过脑子的就脱口而出:“随便摆!”

话确实说得气壮山河,可结果却是有些难过……

之后我拿着coupleC和decoupledC去跑后仿。之前跳得好好的,Von和Vop的DC op应该是500mV。结果我跑了个DC,发现变成了200多mV……结果可想而知,下半部分全部出了saturation region……

我开始以为是提取寄生参数的时候出了问题,所以就跑过去找layouter。layouter说不可能啊!最后没有办法,我就去对比前仿和后仿的netlist。

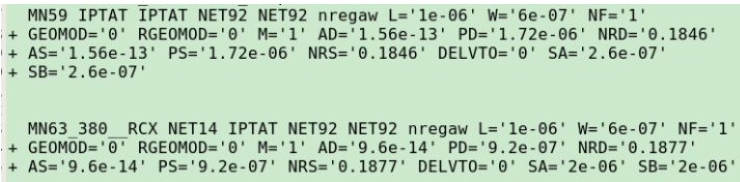

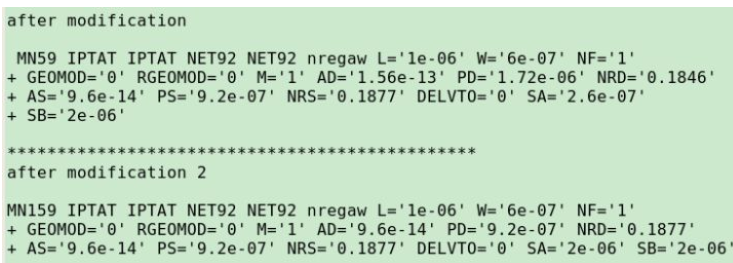

然后下面是后仿netlist里M59和M63的BSIM参数。

大家可以看出来,比如这个叫“AS”的参数,差别已经快一倍了。

后来我仔细琢磨了下,会不会是layout的问题呢?

然后我就去找layouter看这两个管子到底怎么摆的。

因为我当时随口说M59这个diode随便放,所以layouter就把M59跟M63没有放在一起。所以这个所谓的current mirror就完全没有了matching可言。

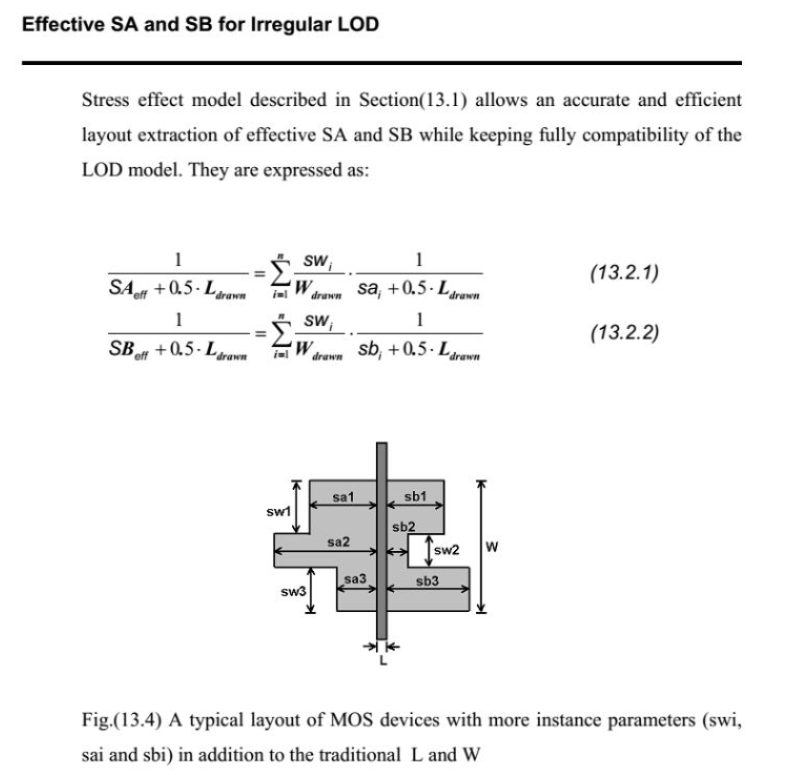

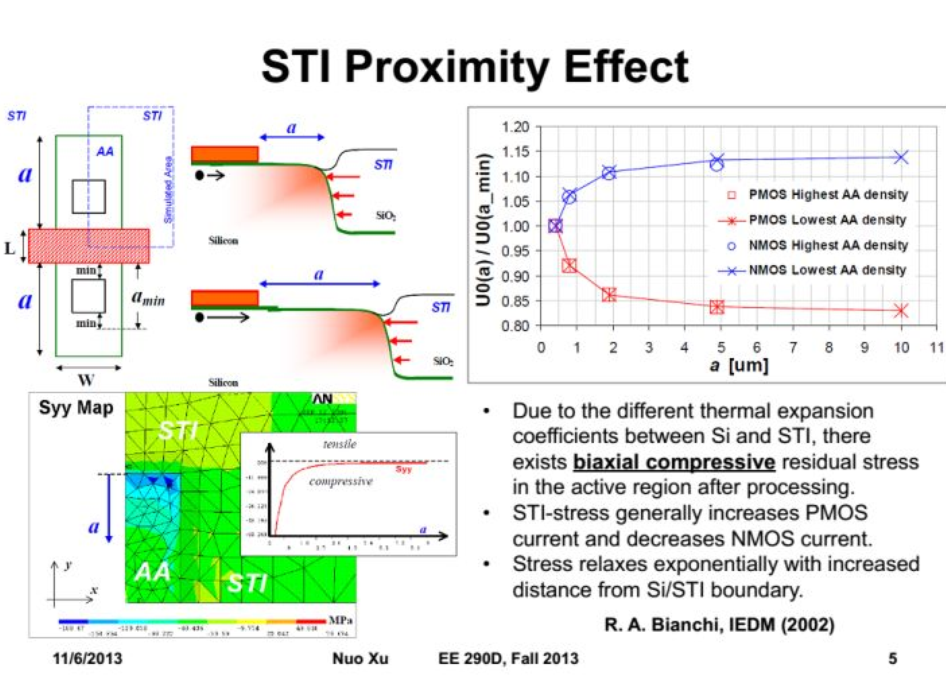

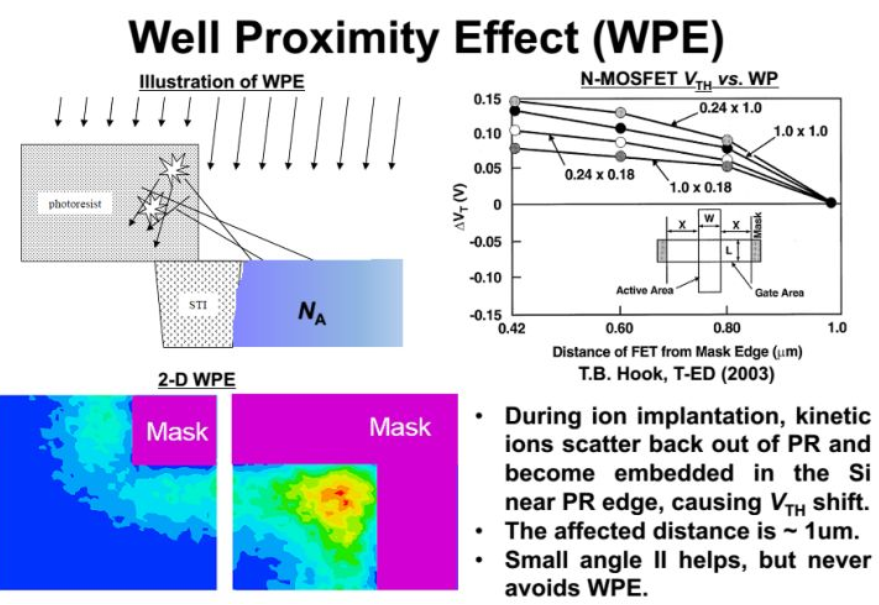

有些layout影响,如STI,WPE(Well Proximity Effect:During ion implantation, kinetic ions scatter back out of PR and become embedded in the Si near PR edge, causing VTH shift. 。The affected distance is ~ 1um. • Small angle II helps, but never avoids WPE.)之类的,就纷纷冒出来了。

发现了这个问题之后,我就让layouter把M59插到M63里面。M63不是有400 (multiplier=400)个吗?我就把M63的m改成了399,其中中间一个留给了M59(下面的netlist里面M59变成了M159)

之后再抽取寄生参数,大家可以对比看看,基本上M159就跟上面的M63一模一样了。

之后再跑后仿,就跟前仿结果所差不太多了。

所以一个模拟电路工程师,必须要具备良好的版图经验。大部分时候,都是电路工程师在告诉版图工程师应该如何画layout。

备注:

source:BSIM4.6.0 MOSFET Model - User’s Manual Mohan V. Dunga, Xuemei (Jane) Xi, Jin He, Weidong Liu, Kanyu M. Cao, Xiaodong Jin, Jeff J. Ou, Mansun Chan, Ali M. Niknejad, Chenming Hu Department of Electrical Engineering and Computer Sciences University of California, Berkeley, CA 94720 Copyright © 2006 The Regents of the University of California All Rights Reserved。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多