在2015年国际固态电路大会上,IMEC和Holst Centre展示了一款高速、紧凑和高度精确的逐次逼近型ADC(或SAR ADC)。这款13位的ADC在1V供电时,功耗仅46μW,相比同类产品,它具有最高的功效。该芯片的SNDR(或信噪比和失真比)为64.1dB。该设计的点睛之笔是采用了超低功耗的片上后台校准,该校准利用了冗余优化纠错方案。由于该技术是普适的,所以可被用于许多新的、用于超低功耗无线应用的ADC设计。

当今的无线电子系统在数字域中存储和处理信息。这些系统为与现实世界信号交互,就需要在模拟和数字信号间进行转换。因此,模拟-数字转换器(或ADC)的发展,就一直是这些无线系统得以成功的要素之一。为适用于各无线标准(如802.15.14g),这些ADC就必须要满足一些严苛的要求:必须低功耗;高的转换速率(以百万次采样每秒或MS/s表示);高分辨率(》10bit)。分辨率表示在整个模拟值范围,该ADC可以生成的离散值的数。由于这些值被以二进制格式存储,所以分辨率以位表示。

在实现ADC的许多方法中,SAR(或逐次逼近型)ADC以其出色功效而备受瞩目。SAR ADC使用一个比较器来逐次缩小包含该输入电压的范围。SAR ADC设计中的一个关键部件是一个内部数字-模拟转换器(或DAC),它用于驱动上述比较器。且该DAC的作用也很关键,因为SAR ADC的精度主要由DAC电容器的匹配来限定。该匹配主要受制造工艺和物理设计的影响。因此,就现代CMOS技术来说,SAR ADC的固有精度被限定在10至12位。

研究者在寻找解决方案以改进DAC匹配。一种方法是扩大器件的尺寸,但它以功效和速度为代价。一种替代方案是,引入校准,通过测量并校正导致的误差,来校正电路的缺陷。这些校准大多在片外实现,因为若在片上实现校准电路,其功耗相对要高。

IMEC和Holst Centre提出了一种创新方案,它成功地在片上实现了低功耗、全自动的后台校准。该校准利用了冗余优化错误检测和校正方案。

在模拟-数字转换过程中引入冗余是另一种流行的处理错误的方案。它与校准不同的地方在于:冗余既不测量也不纠正误差,而是由转换算法简单地决定容忍或抛弃转换结果。为使某些校准技术能发挥效用通常需要结合校准和冗余这两种方法。在我们的设计中,冗余不仅方便了上面提出的后台校准,它还放宽了对DAC建立时间的要求,并通过使用双模式比较器降低了功耗。

这款ADC共使用了15个周期来执行一个13位的转换。双模式比较器首先工作在低功耗模式(模式1),并在最后5个周期,切换到高精度模式(模式2),从而将功耗降低一半。但仍存在两个错误。首先,DAC匹配被限制在《10位,这是由于用于DAC电容器、用来减小面积的小元件(0.3 fF)的存在。第二,当比较器从模式1切换到模式2时,发生动态偏移。

自动化后台校准以可忽略不计的面积或功耗的代价,成功地解决了这两个错误。校准逻辑只应用于一组有限、适用于DAC或比较器校准的SAR代码。这样,就有效地减小了由动态比较器偏移造成的大的初始DNL(或差分非线性)误差,且同时抑制了由DAC失配造成的INL(或积分非线性)误差。

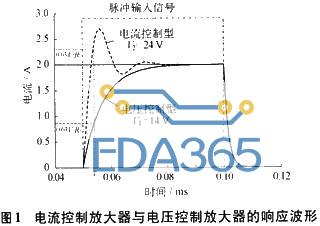

图1:ADC架构。该ADC架构包括比较器、SAR逻辑、反馈DAC和校准逻辑。

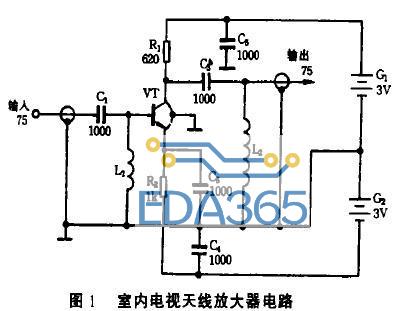

图2:ADC芯片的照片。一款由40nm CMOS工艺实现的超低功耗6.4MS/s、13位ADC。

通过使用这种创新的设计,IMEC和Holst Centre的研究人员采用40nm CMOS工艺实现了一款6.4MS/s的13位ADC。归功于低功耗校准,该ADC实现了10.4bit(或ENOB)的有效位以及先进的5.5fJ/每转换步骤(@6.4 MS/s)的能效。总体而言,该芯片功耗为46uW/1V工作电源。该ADC实现了64.1dB的SNDR(或信噪比和失真比)。将SNDR与ENOB综合起来看,显示出该ADC具有优异的整体动态性能。相比于类似器件,这款ADC实现了最佳能效,且同时还在片上整合了用于比较器偏移和DAC失配的后台校准技术。

表1:ADC结果,性能总结及与先进同类器件的对比。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多