由于项目需要,想设计一个威尔金森型功分器,工作频点在12GHz左右。先用ADS仿了一下,效果不太理想。一则隔离度非常差,只有不到-10dB,再则ADS的版图操作不是很灵活。希望在Ansoft Designer中验证一下,可是到处都搜不到相关的示例。百般周折,总算完成了仿真,于是写了几点总结,供旁人参考和指正。

提前声明,本仿真的结果未经过实验验证,因为通常认为,12GHz已经超出了威尔金森型功分器的适用频段范围(X波段以下),此时隔离电阻的寄生参数会对器件的性能产生不可预知的影响。本文目的仅在于总结软件的使用经验,尤其隔离电阻在版图仿真中的添加方法。

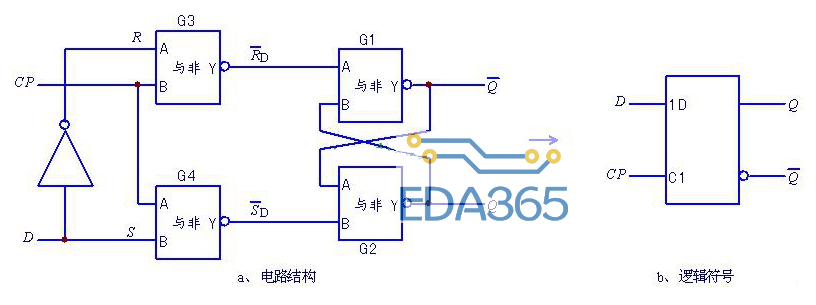

1. 在仿真Wilkinson功分器时,隔离电阻的添加是最大的困难。虽然Ansoft Designer的原理图元件库中提供了薄膜电阻(Components->Microchip->…),但是无法导入到版图中,因此版图中隔离电阻实际上是用一个2端口网络来代替,在Ansoft Designer的安装目录中的Examples文件夹中,有两个威尔金森功分器的示例,wilk_c和wilk_k,其中wilk_k是有隔离电阻的示例。

在Planar EM界面中,2端口网络可通过Draw菜单中的N-port项添加。若要令端口1与功分器微带线的某个边缘连接,需先通过按钮选中该边缘,然后按住Ctrl键,点选对应端口1,点击Connection按钮 就完成了连接。

关于2端口网络的设置,参照wilk_k中的参数。对S参数的设置本人尚未弄懂,望高手指点。

2. 在版图仿真之前,要通过Mesh Overlay选项查看一下网格的划分是否正常,如果存在因未对齐而导致的密集的小网格,必须调整版图,否则是肯定仿不出正确结果的。

另外,如果版图是从外导入进来的,一般都需要合并一下(全选->Merge Polygons->Union)

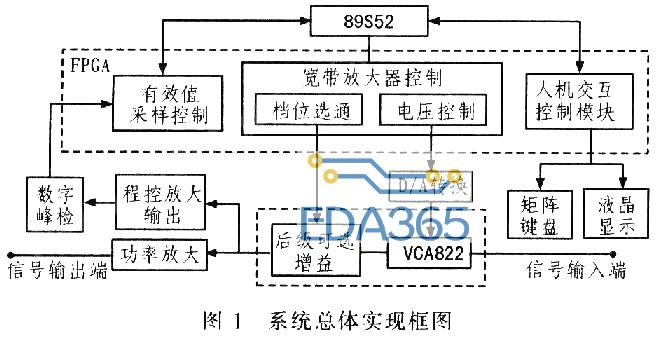

3.Ansoft Designer也能像ADS一样由原理图生成版图,方法是通过Circuit菜单中的Layout Editor项。但是生成的Layout文件不能执行版图仿真,还需要导入到一个Planar EM文件中,方法是先通过Ctrl+A全选Layout中的图形,然后点击Edit菜单中的Copy to Planar EM项。

下面是我绘制的版图及其仿真结果。12GHz频率太高了,1/4波长线特别短,所以采用了下面所示的形状。隔离电阻附近,两路走线的对应线段为垂直关系,希望对降低两路的耦合有所帮助。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多