行为模型助力 设计/测量同时进行

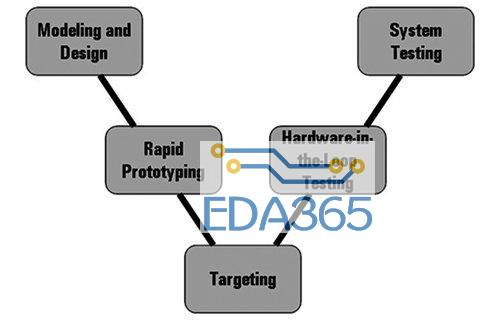

在整合设计与测试实例的第二个趋势,就是利用EDA所产生的行为模型,加速开发产品检验/认证,并製作测试软件。在此之前,让产品设计程序效率低落的塬因之一,就是特定产品的测试程序代码开发缓慢,甚至要等到首次测试实体塬型之后。不论是特性描述或生产测试程序代码,若要能加快开发程序,最好透过软件製作既定设计的塬型并直接做为DUT。透过此方式,工程师将可以于产品设计期间同时,开发特性描述与生产测试软件,进而加速上市时间。

以美敦力(Medtronic)为例,该公司最近就针对心率调节器开发而选用此设计方式。美敦力透过特殊设计的新软件套件衔接EDA环境与测量软件,连接软件环境之后,工程师可于製作实际硬件之前就开发出测试工作台,而透过此设计方式而达到的平行机制,让工程师能因此加速产品上市时间。

在提升工程设计完整度的过程中,整合“设计实例”与“测试实例”的重要度将越来越被突显。由于EDA与测量软件间越来越紧密,工程师将能于未来数年之内更有效利用EDA软件,以取得更完整的模拟作业,并让EDA模拟功能强化检验与生产测试的程序。

FPGA启动下世代测量仪器革命

过去20多年来,“微处理器架构、可由使用者设计程式的测量演算法”已成主流概念,让测试系统可迅速接受不断变动的客製化测试需求。此方法亦即所谓的虚拟仪控,且供应商亦继续设法设计其他仪器优势--更高效能、提高客製化程度、更广泛采用现成技术、降低测试系统成本等。

如果说微处理器带动虚拟仪控的革命,那么现场可编程闸阵列(FPGA)就又启动了下个阶段。FPGA用于仪器之中已有数年,举例来说,目前高频宽示波器虽可蒐集大量资料,但使用者并无法迅速分析所有资料。这些装置上的硬件定义演算法一般均建置于FPGA,以执行资料分析与缩减(平均、触发、波形数学)、运算统计(平均值、标准差、最大值、最小值)、处理资料以利显示,最后为使用者呈现有意义的结果。这些功能虽然确有其价值,但却无法突显FPGA潜在功能,在大部分条件下,使用者并无法将客製化测量演算法部署至FPGA。

测量硬件上的开放式FPGA,可为仅有处理器的系统提供多项优势。基于FPGA的强大运算功能,将可达到更高的测试传输率与更广的测试範围,进而缩短测试时间并降低投资成本。微处理器所无法达到的测试作业,亦可透过FPGA的低延迟特性而建置。FPGA既有的平行机制,可达到真正的多执行序测试,甚至超越多核心处理器。在即时测试的硬件排序与待测物控制程序中,FPGA更扮演关键角色。

由产业研究公司Frost & Sullivan所发表的2011年模组化仪控市场研究指出,由Altera与赛灵思(Xilinx)等公司对FPGA功能的提升,将对测试与测量应用影响深远,对需要高精确度与快速处理功能的客户而言尤为如此,目前市场上有越来越多的开放式FPGA产品。

虽然市面上已有许多硬件可供选择,但大多数的测量演算法都是针对虚拟仪控的微处理器部分所开发。基于资料形态、程式设计模型、特定硬件属性(如时序限制) 等的不同,并无法简单移至FPGA继续使用。厂商要开发专业且稳定的FPGA测量硅智财(IP)须具备专业知识并耗上大量时间,因此,目前仪控硬件中的大多数FPGA仅使用供应商定义的固定演算法,无法由使用者自行设计程式。

2011年业界就已经开始讨论异质运算(Heterogeneous Computing),意即将演算法分配至多种运算架构(中央处理器(CPU)、图形处理器(GPU)、FPGA、云端系统)中,找出最佳的演算法建构资源。除硬件架构本身的强大功能考量之外,异质运算代表各种系统的程式设计难题,且测量演算法难以在系统之间“携带”,复杂度确实有所影响。

业界最近针对测试工程领导厂商的全球调查指出,约有54%受访者认为未来技术发展将可提升测试传输率并降低系统成本,进而缩短开发时间。为克服此难题,产业界正积极开发相关工具,以期能跨硬件系统使用演算法,并且让FPGA可普及于测试系统。

此种跨硬件的系统将可提供硬件描述语言(HDL)抽象化。HDL是以文字方式描述逻辑闸层(Gate)与讯号层(Signal-level)的行为,而 HDL抽象化(Abstraction)工具则透过图形或简图的呈现方式,撷取更高层级的设计(图3)。与HDL相较,虽然这些工具确实降低FPGA技术的门槛,但仍无法完全省略某些FPGA设计的特定硬件属性,如资源分配、数位讯号处理器(DSP)分割架构、管线流通(Pipelining)、内建记忆体(On-chip Memory)等。在这些情况下,仍须重新设计/检验演算法才能衔接FPGA,也促成开发工具的未来发展。

图3 开发软件必须能跨执行系统,而达到更高的硬件抽象化与灵活度,以达更高效能、更高成本效益,且更能迅速上市。

挟多重优势 开放式FPGA普及于测量系统

高阶合成(High-level Synthesis, HLS)工具可于较高阶层撷取演算法,并为既有建置独立分配其效能属性,如延迟、时脉率、传输率、资源利用等。由于特殊建置并不属于演算法定义,如此也降低演算法的可携性。此外,开发工程师在设计硬件特性(管线流通、资源仲裁等)时,并不须顾虑特定硬件。HLS的概念已存在超过20年,但市面上的工具是最近才渐趋成熟。这些工具确实提供相关优势,但仅针对FPGA或特定应用积体电路(ASIC),并未纳入如GPU与微处理器的其他运算平台。为突破这些 HLS工具的限制,业界提供测试版软件,整合既有的LabVIEW资料流程式图与HLS优点,以因应FPGA设计作业。如此一来,建置FPGA亦可纳入大量LabVIEW测量与控制演算法,而不受制于微处理器的执行情况,亦不须针对FPGA部署作业而重新设计大量演算法。此软件目前仍在测试中而无法普及,但最后的目标结果可期。

创新开发工具的最后一步,就是让跨硬件系统整合运算/设计的多种模型。这些运算模型包含LabVIEW资料流程式图、DSP简图可用于RF与通讯应用中的多重速率讯号处理、文字式数学可撷取类教科书的方程式、状态机器用于数位逻辑与协定等。

举例来说,如赛灵思Zynq可延伸处理平台所建构的系统单芯片(SoC)系统,未来将整合双核心安谋国际(ARM)微处理器与FPGA。此芯片具备极高的异质运算潜力,但由于微处理器与FPGA分别需要不同的运算语言/模型,所以程式设计作业的难度极高。在理想状态下,工程师应拥有多样的运算模型以支援所有系统,并以更有效的方式撷取演算法,最后部署至最佳执行系统。根据业务需求的不同,这裡的“最佳”可能代表最高效能、最高成本效益,或最短上市时间。若要让工具搭配非特定硬件的运算模型,仍有一段开发的路要走,而且必须能满足目前测试系统的开发需求。

开发软件必须能跨执行系统,而达到更高的硬件抽象化与灵活度,以达更高效能、更高成本效益,且更能迅速上市。

虽然非特定硬件的测量演算法与高阶合成工具尚未晋升主流,但开放式FPGA正逐渐普及于自动化测试系统中。FPGA在测试作业中的优势,已值得许多厂商投入更多开发资本,而且只要提升软件工具,将连带缩短开发时间并降低复杂度,促成更多相关应用。如同微处理器与相关 的软件开发环境/测量演算法,带动了虚拟仪控的革命,使用者可设计的FPGA亦将带动图形化系统设计(GSD)的下一波革新,催生未来的测试系统。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多