摘要:设计一种低电压低静态电流的线性差稳压器。传统结构的LDO具有独立的带隙基准电压源和误差放大器,在提出一种创新结构的LDO,把带隙基准电压源和误差放大器合二为一,因而实现了低静态电流消耗的目的。设计采用CSMC0.5 μm 双阱CMOS工艺进行仿真模拟,这种结构LDO在轻负载情况下静态电流仅为1.7 μA,输出暂态电压最大变化为9 mV.

随着过去几十年里掌上智能终端快速发展,低压差的线性稳压器(Low Drop-out Regulator,LDO)因其具有低功耗、高的电源抑制比、体积小、电路设计简单等优点得到大量应用。LDO大部分时间工作在低负载应用,因此,其在低负载情况下的静态电流消耗决定着电池的寿命。当今的LDO发展趋势是低电压、低静态电流来延长电池使用寿命。然而,低静态电流会导致不稳定性,带来大的输出电压暂态变化,必须在静态电流和输出暂态特性进行合理的折中。相比于传统LDO采用分立结构的带隙基准电压源和误差放大器,本文给出一种创新结构的LDO,将带隙基准电压源和误差放大器两个模块合二为一,因此更容易实现低静态电流消耗,低暂态电压变化。

1 LDO电路分析

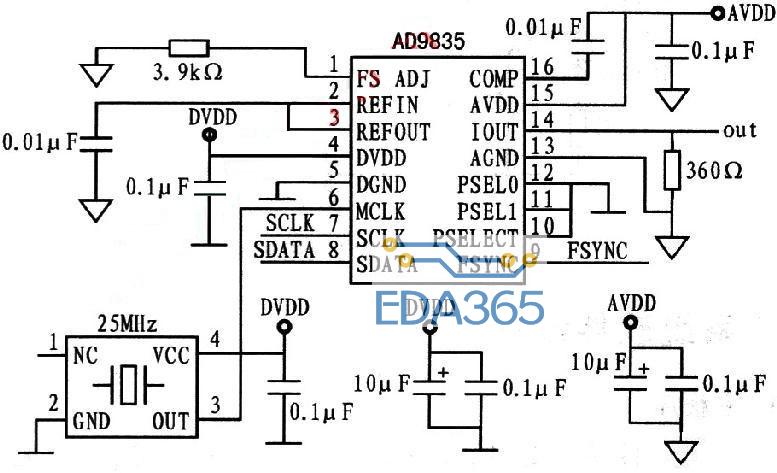

图1给出精简结构的LDO,仅仅包括4条主要的电流支路,分别是:增益级、缓冲级和2个PTAT电流源。

相比传统结构LDO,精简结构将带隙基准电压源和误差放大器合二为一,因此在其他性能不变情况下,可将电路静态电流消耗减小到原来1 2 左右。

这个电路存在两个缺点:输出电压为带隙基准电压不可调;需要使用NPN晶体管,而标准CMOS工艺中并不存在NPN晶体管。由于如今的SoC趋向工作在低电压环境,因此这种结构能够有充足的应用场合。第二个问题在单片设计时候,采用双阱CMOS工艺,只需增加一道掩膜工艺,费用增加不多,因此两个问题实际应用并不明显。

1.1 带隙基准电压分析

三极管基射级电压和热力学电压分别具有负、正温度系数,因此带隙基准电压的原理是叠加三极管基射级电压和热力学温度电压,达到在室温下的零温度系数。

在精简LDO结构中,晶体管Q3和电阻R2定义带隙基准电压,流过R2为PTAT电流。通过镜像流过晶体管Q1电流。晶体管Q3偏置到集电极电流。因此,在环路中,晶体管Q1和Q3将调整到相同的基射级电压值。尤其环路比较高的情况下,这种调整是相当精确的。因此,通过合理设计电阻R2和R3,晶体管Q1,Q2和Q3有相同的集电极电流。因此:

式中:IS 是三极管饱和电流;β2 是晶体管Q2的电流增益;n 是晶体管Q2和Q1射级面积比。通过式(1)可以得到PTAT电流:

因此通过晶体管Q3的基射级电压和R2电压叠加即可得到输出电压值:

调整电阻比值,使VT 系数值为17.2,即可得到温度系数为零的带隙基准电压。

1.2 LDO频率分析

精简结构LDO中包含三个低频极点,分别处在增益级的输出,缓冲级的输出和LDO的输出节点,分别如下:

式中:ro1 和C1 分别是增益级输出电阻和负载电容;ro2是缓冲级输出电阻;Cpar 是功率管寄身电容;rop 是LDO输出级的等效电阻;CL 为输出负载补偿电容。为了保证LDO有个良好的输出暂态特性,CL 取值一般很大,因此极点p3 为LDO环路的主极点。晶体管Q3集电极电流偏置为PTAT电流,因此增益级的输出阻抗随输出负载电流和输入电压变化不大,同时增益级的负载电容主要由缓冲级输入电容决定,所以极点p1 位置相对稳定,故可以采用一个左半平面的零点补偿。类似如传统LDO,本文采用一个电阻resr 与输出补偿电容串联方式,获得一个左半平面零点:

基于上述分析,精简结构LDO的开环传输函数为:

式中.其中:gmQ2 ,gmQ3 和gmp 分别代表晶体管Q2,Q3和功率管的跨导;Rπ 3 是晶体管Q3的输入电阻。当p1 和z1 匹配比较精确,LDO环路只有两个低频极点p2 和p3 。因此,为了获得60°的相位裕度,必须:

2 电路设计与实现

本文所提的低电压、低静态电流的精简结构的LDO如图2所示。LDO的输出级是一个A类共源级电路,包括PMOS功率管M1,三极管Q1、Q2,电阻R1,R2,R3,Resr和输出负载补偿电容C1.功率管M1有非常大的宽长比来驱动比较大的负载电流。因此M1的沟长选取最小的值,达到尽可能小的寄身电容和尺寸面积。为了获取好的暂态输出特性以及环路稳定,输出补偿电容取5 μF.带隙基准电路包括三极管Q1,Q2,Q3和电阻R1,R2,R3.选取Q2的射级面积为Q1和Q3的射级面积8倍,这是Q2面积和R2阻值折中结果。三极管Q3和晶体管M6构成一个共集电极的电路,为环路提供高增益。缓冲级包括晶体管M2,M3和M4.因为NMOS源跟随器,在低负载情况下并不能完全关断功率管,PMOS源跟随器并不适合本电路的1.35低电压环境,所以选用了二极管连结的PMOS负载共源级电路作为缓冲级。这种结构不仅获得低的输出阻抗,同时达到180°的相位偏移,使整个闭环环路构成一个负反馈。M3作用是在低负载电流的情况是为M4提供一些偏置电流,否则可能出现M4的栅源电压过低,导致三极管Q3进入饱和状态,降低Q3的电流增益,影响带隙基准电压的精确度。通过Q4和M7构成的偏置电路,使得三极管Q1,Q3有相等的集电极电流。晶体管M5,M8和M9构成LDO的启动电路。在刚有电压输入情况下,M8和M9构成一个反相器输出一个低电压信号,使M5导通来启动整个电路。

3 电路仿真结果

基于CSMC 0.5 μm 双阱CMOS 工艺仿真模型,采用Cadence仿真软件对精简结构LDO进行了三个工艺角(tt,ff,ss)下仿真验证。这个系统设计指标的是让LDO驱动最大30 mA的负载电流,同时保持输出电压稳定在1.14 V,输入电压最小为1.35 V.LDO 的温漂曲线如图3所示。

通过采用补偿电容外接串联电阻的方法,创造一个左半平面的零点来补偿一个非主极点,让电路获得比较好的环路相位裕度,在三个工艺角下,相位裕度都能达到70°(见图4)。

暂态输出电压变化如图5所示,当负载电流从0~30 mA瞬态变化时,输出电压变化最大仅为9 mV.

4 结语

本文给出了一种低电压1.14 V、低静态电流1.7 μA 的LDO,通过将带隙基准电压源与误差放大器合二为一获得精简结构的LDO.

因此实现了低静态电流消耗,同时获得较好的暂态输出电压性能,最大暂态电压变化仅为9 mV.

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多