2.2.2 定时误差检测设计

定时误差检测程序采用独立于载波相位偏差的GA-TED算法。该算法每个符号周期只需要两个插值,每个码元周期输出一个误差信号μτ (n) ,即:

其中,y(n) 表示第n 个码元选通时刻的内插值,前后两个内插值的插值代表误差方向;y(n - 1 2) 表示第 n 个和第n - 1 个码元的中间时刻内插值,代表误差大小。

FPGA实现时,为避免乘法运算,采用y(n) 和y(n - 1)的符号来代替实际值[8],即采用式(5)计算误差信息:

根据式(5)进行程序设计,误差的正负方向判断采用case 语句,当y(n) 和y(n - 1) 的符号位分别为“0”和“1”时,y(n - 1 2)的符号位不变;当符号位分别为“1”和“0”时,y(n - 1 2) 的符号位取反;当符号位为“0”“0”或“1”“1”时,令输出的μτ (n) = 0.TED程序在1 Ti 的时钟控制下进行运算,最终得到29位误差数据,并以1 T 的速率即码元速率输出至环路滤波器电路。

2.2.3 环路滤波器设计

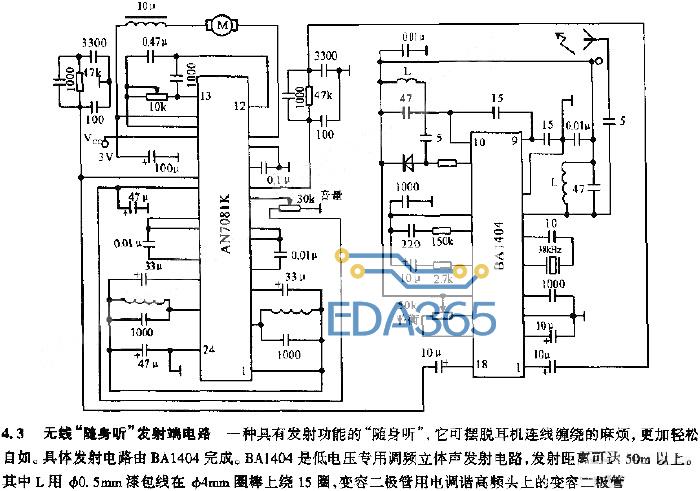

本文对Gardner算法中的环路滤波器进行了改进,根据通用位同步器的要求,采用二阶数字滤波器,并且开放滤波器参数(C1,C2 ) 和使能(c_en)端口,当码元速率变化时,通过外部控制器来改变参数,实现滤波器的通用性。滤波器结构如图5所示。

从图5可以看到,滤波器的输出为:

式中:Ko Kd 为环路增益;ζ 为阻尼系数,取ζ =0.707;T 为采样时间间隔,即相位调整间隔;ωn 为无阻尼振荡频率。

为减少资源占用,环路滤波器中的乘法运算均采用移位方式实现,处理后的误差信息送给内部控制器。

2.2.4 内部控制器设计

内部控制器根据定时误差信息,调整插值频率1 Ti和误差间隔μk ,并输出位同步脉冲BS,它包含NCO(Numerically Controlled Oscillator)和误差间隔计算两部分。该程序提供接口(频率字fw 和使能端fw_en),外部控制器可以通过该接口输入参数。

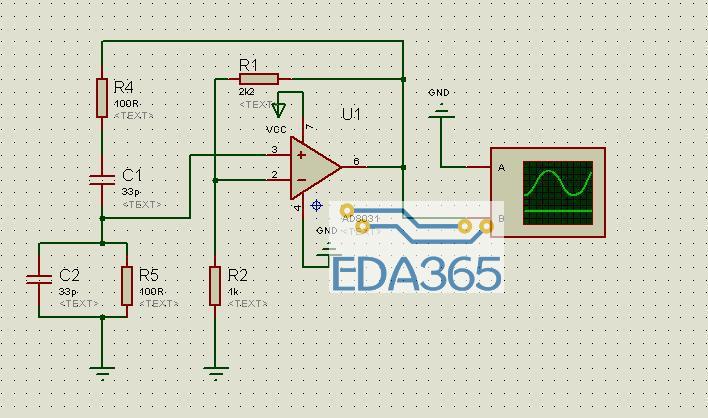

本设计中NCO 采用与文献[10]类似的DDS(DirectDigital Synthesis)结构,其频率控制字Fw 可由外部控制器设置,其结构如图6所示。

图6中,M 为频率控制字位数,N 为相位累加器和相位寄存器的位数。这里取M = N = 23,采用递减型的NCO,归一化后相位累加器的累加值为:

式中:Fw 为频率控制字;W (mk ) 为环路滤波器输出的误差信号,二者由环路滤波器提供,决定了NCO的溢出周期。其中,当:

NCO 溢出信号即为提取出的位同步信号的2 倍频(2BS),经2分频后可以得到位同步脉冲(BS)输出,2BS同时作为内插滤波器和误差间隔计算的使能信号。

误差间隔μk 在NCO 溢出后的下一个Ts 时刻进行计算,环路锁定时:

将其截断为8位数据送给内插滤波器。

本设计同时对代码进行了优化,数据有效位的截取、内插滤波器的结构优化、乘法采用移位计算代替等措施,有效地节省了硬件资源,优化前和优化后的资源占用情况对比见表1.

3 仿真和分析

3.1 Matlab仿真

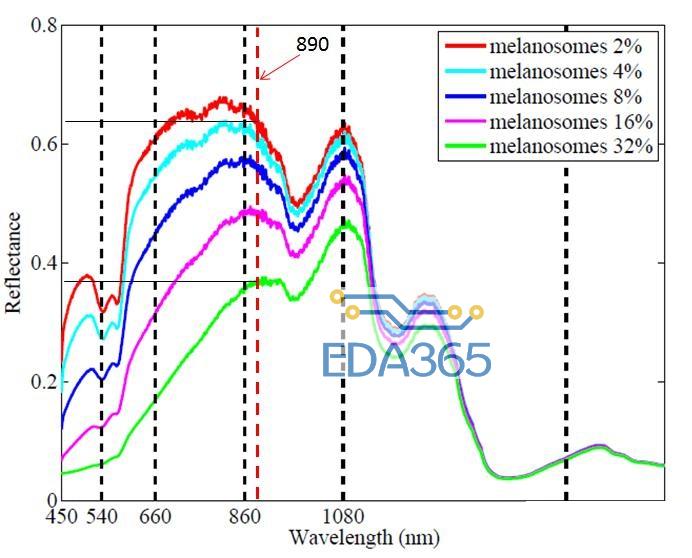

本文采用Matlab对算法进行理论仿真,输入采样值x(m) 为[-1,1]之间的随机码,采样频率上限为20 MHz,令码元速率分别为2 Kb/s,600 Kb/s,10 Mb/s,环路滤波器、内部控制器参数随码元速率变化。取内插滤波器的插值输出y(kTi) 做散射图分析,验证对不同速率的基带信号,内插值是否接近最佳判决值,如图7所示。

从图7可以看出,在基带速率和采样率满足奈奎斯特定理的条件下,该仿真输出的内插值均集中在理想值 -1和1周围,虽然有一定的模糊,且频率越高,模糊程度越大,但码元判决阈值在0值点,所以判决值无需严格为±1,该图表明对于较宽速率范围内的基带信号,输出的插值均能够较好地用于码元判决,即算法正确。

3.2 FPGA仿真

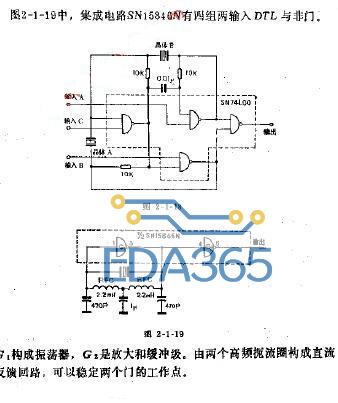

在Quartus下对本设计进行仿真。基带信号采用M 序列,由FPGA生成,令基带码速率分别为2 Kb/s,600 Kb/s,1 Mb/s,同时分频器、NCO 及环路滤波器参数也做相应设置,仿真结果如图8所示。

在图8中,x为基带码元序列,y为内插值输出,clk_t为基带码元时钟,clk_bs为提取出的位同步信号。从图中可以看到,clk_bs经过定时环路调整,其上升沿逐渐向clk_t的下降沿(即最佳判决点)靠近,且随着基带码元速率的变化,clk_bs也会随之变化,但其中心频率与clk_t相同,相位与最佳判决点相差不超过半个码元周期,可以进行码元判决,这表明本设计对2 Kb/s~1 Mb/s内的基带信号,均可实现位同步。

4 结语

本文提出了一种基于FPGA的通用位同步器的设计方案。该设计方案中的同步器在传统Gardner 算法的基础上进行了改进,其中,内插滤波器采用Farrow结构,定时误差检测采用GA-TED算法,环路滤波器和内部控制器参数可由外部控制器设置,因而实现了较宽速率范围内基带码元的位同步。仿真结果表明,该方案占用FPGA资源较少,并且在实际应用中具有可靠有效性。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多