QSPI概述

QSPI接口,是QueuedSPI的缩写。和之前谈到的SPI一样都是出自Motorola。QSPI在SPI基础上做了一些增强,且向下兼容SPI。QSPI相对SPI最显著的差异就是增加了发送接收数据队列,Queued的称呼就是这么来的。这样做的好处就是,无需每次数据传输都需要CPU参与,可以降低CPU的资源占用。

QSPI应用框图

图1为QSPI应用框图,同SPI最明显的区别就是多了队列Buffer和片选变为4个。QSPI通过片选直连的方式,最多可接4个外设,如果外挂4-16译码器可以扩展至16个外设。

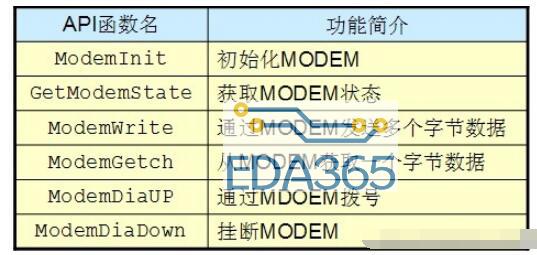

QSPI接口信号

如表1所示,QSPI在SPI原有4根信号基础上增加了4个外设片选信号PCS0~3,其中PCS0同SSn复用。因此QSPI总共7根信号线。

QSPI新增功能

QSPI是在SPI基础上进行扩展,其包含了SPI所有特性。其和SPI相同的特性,本文不再赘述,感兴趣的同学请点链接(常用数字接口(2)SPI)。QSPI相对于SPI新增如下功能:

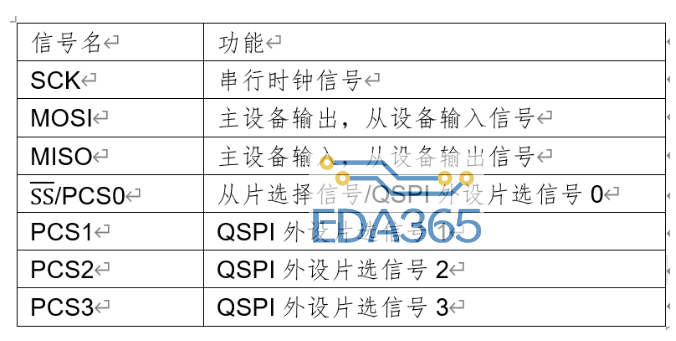

1、可编程Buffer

如图2所示,QSPI提供总共80字节的可编程Buffer。其中TxDataBuffer32字节,TxCMDBuffer16字节,RxDataBuffer32字节。RxDatabuffer存储接收数据,TxDatabuffe存储发送数据,Buffer深度均为16深度,数据位宽取决于单次访问位宽配置,配置范围8~16bit。TxCMDBuffer存储发送命令,Buffer深度为16,位宽8bit。

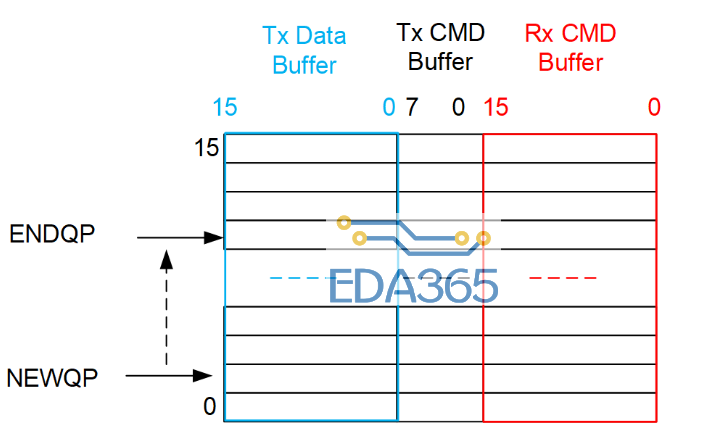

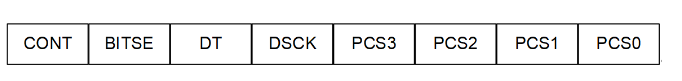

TxCMDBuffer每条命令格式如图3所示。

CONT:片选保持使能。1’b1,本次传输完成后PCS[3:0]输出保持本次传输时的状态;1’b0,PCS[3:0]输出与之复用的GPIO输出配置值。

BITSE:传输长度控制。1’b1,根据配置长度传输(可配置8~16bit);1’b0,固定传输8bit长度。

DT:每次传输完成后是否等待。1’b1,本次传输完成后等待一个可配置的时间;1’b0,不等待。

DSCK:PCS和SCK相对相位调整。1’b1,从PCS有效到SCK延迟一定时间(时间可配置);1’b0,固定为1/2SCK延迟。

PCS[3:0]:QSPI外设片选信号状态。当PCS0~3一对一连接至从设备时,QSPIMaster通过该命令可以选择访问4个外设中的哪个。当PCS0~3外接4-16译码器时,QSPIMaster可以管理最多16个从设备。

TxCMDBuffer和TxDataBuffer共享指针,即TxCMDBuffer中的命令和TxDataBuffer中的数据一一对应。通过配置TxCMDBuffer可以定义了每一次发送数据的行为,如发送数据长度、发送间隔进行定制。这种针对每次数据传输定义不同访问间隔、访问长度的方式,在访问不同类型外设时可以大大提高访问效率。

2、队列指针可编程

如图2所示,QSPI依据ENDQP(队列尾指针)和NEWQP(队列首指针)的配置,从NEWQP指定的行开始,按照TxCMDBuffer对应行中指定的行为发送TxDATABuffer中对应行的数据,直到发送/执行到ENDQP指定的行结束。该过程中,CPU仅需在发送开始前对Buffer中内容进行编辑,之后无需占用CPU资源由QSPI自动完成。当ENDQP比NEWQP小时,QSPI先从NEWQP对应的行开始执行,当执行到第15行时卷绕至第0行,然后再递增执行到ENDQP行停止。

3、自动回卷(Wraparound)功能

该功能使能后,QSPI按照EDNQP,NEWQP确定的传输队列重复发送数据。这种功能在对外设进行定时扫描时非常有用。

4、连续传输模式

该模式使能时,QSPI可在一次数据传输中,进行多达256bit的数据传输。

从上述4条增强功能可以看出,QSPI所有新增功能都是围绕尽量降低CPU资源占用的理念进行的。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多