一、1-Wire接口

1-Wire接口是由MaximDallas半导体公司(首页为/zixunimg/elecfansimg/www.maxim-ic.com)开发的异步半双工通信协议,也称为Dallas1-Wire®协议。其中,按照主-从通信模型,只使用单条信号线DQ实现通信。1-Wire总线的一个重要特征在于,该总线允许在信号线上传输能量。I2C从设备在信号线上使用内部电容器(其典型取值为800pF)来驱动设备。1-Wire接口支持在总线上连接单个主设备以及一个或多个从设备。

每台1-Wire设备都具有全球唯一可识别的64位识别码信息,存储在设备内部。对于多台从设备连接到1-Wire总线上的情况,通过解读唯一的识别码,可以寻址总线上存在的各台独立设备。识别码由以下三个部分组成:8位的类别码、48位的序列号以及前56比特数据的8位CRC校验结果。与1-Wire从设备通信的具体流程如下:

(1)主设备将复位脉冲发送到1-Wire总线上。

(2)总线上的从设备通过确认脉冲予以回应。

(3)主设备发送ROM命令(网络寻址命令,参数是设备的64位地址),从而寻址到需要发起通信的从设备。

(4)主设备发送读/写命令,对从设备的内部存储器或寄存器进行读/写操作。

(5)主设备将数据由从设备读出,或者是将数据写入从设备。

1-Wire总线上的所有通信都是由主设备发起的。其中,通信的最小间隔是时长为60微秒的时隙。复位脉冲占用8个时隙。在通信的开始阶段,主设备将1-Wire总线拉低到低电平,并持续8个时隙(即480μs),从而发出复位脉冲。如果总线上存在从设备,而且已经准备好进行通信,那么从设备将通过确认脉冲来回应主设备;也就是说,从设备将1-Wire总线拉低到低电平,并持续1个时隙(即60μs)。为了在1-Wire总线上写入位值1,需要总线主设备将总线拉低,其持续时间为1~15μs,然后在该时隙的其余时间段释放总线。

为了在总线上写入位值0,主设备需要将总线拉低,其持续时间至少为1个时隙(60μs),最多为2个时隙(120μs)。为了由从设备读出位值,主设备需要将总线拉低,并持续1~15μs。为了响应主设备的读数据请求,如果从设备想要发送位值1,那么从设备只需要在该时隙的其余时间段释放总线;如果从设备想要发送位值0,那么从设备需要在该时隙的其余时间段将总线拉低。

二、UART

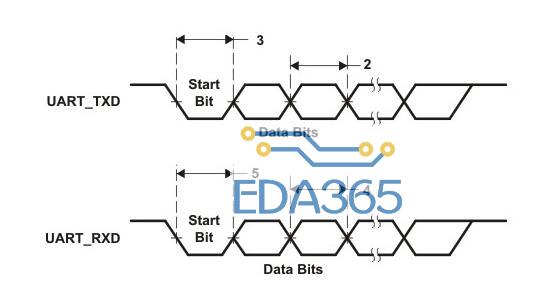

UART:通用异步串行口,按照标准波特率完成双向通讯,速度慢。

UART总线是异步串口,因此一般比前两种同步串口的结构要复杂很多,一般由波特率产生器(产生的波特率等于传输波特率的16倍)、UART接收器、UART发送器组成,硬件上由两根线,一根用于发送,一根用于接收。

UART是用于控制计算机与串行设备的芯片。有一点要注意的是,它提供了RS-232C数据终端设备接口,这样计算机就可以和调制解调器或其它使用RS-232C接口的串行设备通信了。作为接口的一部分,UART还提供以下功能:

将由计算机内部传送过来的并行数据转换为输出的串行数据流。将计算机外部来的串行数据转换为字节,供计算机内部使用并行数据的器件使用。在输出的串行数据流中加入奇偶校验位,并对从外部接收的数据流进行奇偶校验。在输出数据流中加入启停标记,并从接收数据流中删除启停标记。处理由键盘或鼠标发出的中断信号(键盘和鼠标也是串行设备)。可以处理计算机与外部串行设备的同步管理问题。有一些比较高档的UART还提供输入输出数据的缓冲区,现在比较新的UART是16550,它可以在计算机需要处理数据前在其缓冲区内存储16字节数据,而通常的UART是8250。现在如果您购买一个内置的调制解调器,此调制解调器内部通常就会有16550UART。

除了串行数据传输功能以外,UART还可以为控制串行数据流提供硬件握手信号支持。很多半导体厂商都提供了相应的UART芯片。如今,大多数微处理器/控制器都集成有UART功能,并为串行数据传输与接收提供内置式的指令支持。

三、并行接口

板上并行接口(parallelinterface)通常用于系统与外围设备之间的通信,其中,外围设备通过存储器映射到系统的主控端。只要嵌入式系统的主控处理器/控制器含有并行总线,支持并行总线的设备就可以直接连接到该总线系统上。外围设备与主控端之间具有控制信号接口,可以控制并行总线上的数据通信。这里,通信的控制信号包括读/写信号和设备选择信号。一般说来,外围设备具有设备选择线;只有当主控处理器选通该线的时候,该设备才是有效的。数据传输的方向可以是从主控端到外围设备,也可以是从外围设备到主控端;这是通过读和写控制信号线进行控制的。只有主控处理器能够控制读控制信号和写控制信号。一般说来,外围设备通过存储器映射到主控处理器,从而可以访问分配的地址范围。此时,设备需要使用地址译码电路来产生芯片选择信号。

当处理器选择的地址位于设备指定范围内的时候,译码电路对芯片选择线进行触发,从而激活设备。然后,处理器可以使能相应的控制线(分别是RD\与WD\),从而由设备读出数据,或者是向设备写入数据。为了实现并行通信,系统需要严格遵循时序规范。前面已经提到过,并行通信是由主控处理器启动的。如果某外围设备想要对通信进行初始化,那么可以向处理器发出中断,告知相关信息。为了实现上述功能,设备的中断线需要连接到处理器的中断线上,并且主控处理器需要触发相应的中断。需要说明的是,主控处理器的数据总线宽度决定了并行接口的宽度,可以是4位、8位、16位、32位、64位等。设备支持的总线宽度应该与主控处理器完全相同。并行数据通信为系统提供了高速数据传输能力。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多