高速串行信号带来的测试挑战

消费者对通信和计算机产品的要求越来越高,不断提升的速度、不断增长的容量,但却不能成正比变化的价格,成为用户决定是否掏钱购买新款产品的基本要求。这些来自终端客户的需求通过产业链逐级传递到产品研发工程师对测试仪器的需求层面。能设计出超高数据传输速率的通信产品,就一定需要性能匹配的信号测试工具,否则无法保证最终产品的性能、质量和一致性。

五年前,数据吞吐率在3.125Gb/s的通信系统背板只是停留在少数顶尖通信设备商预研阶段的概念,2.5Gb/s的PCI-Express G1协议也只是售价昂贵的高端通信产品才具备的内部互连总线。而如今,传输能力达6.25Gb/s高速背板已经非常普遍的应用在通信设备上,单对线吞吐率高达12Gb/s的串行背板总线在技艺精湛的工程师手上也即将变为现实。更高传输速率达5.0Gb/s的PCI-Express G2也早已是普通PC声卡、显卡的标准配置。而实际上,高达8Gb/s的PCI-Express G3总线标准也将在2009年正式面世,还有4.8Gb/s的USB3.0接口、6.4Gb/s的FB-DIMM存储器架构,乃至10Gb/s的Serial Rapid I/O串行协议等。

5Gb/s以上新串行协议层出不穷,面对这么高速的测试信号,需要全新的思维:因为测试仪器本身已经构成了工程师诊断问题的障碍,示波器主机、探头、测试夹具、电缆对被测信号哪怕是一点点的破坏,也可能让你得出与事实完全相反的结论,这不仅需要示波器具备更高放大器带宽和采样性能,而且能够去除由于测试设备的引入而对被测电路带来的负面效应;另一方面串行协议内容越来越复杂,需要更高级的分析软件和仿真模型来深入洞察问题的本质。这两方面催生工程师对测试设备的需求不断提高,同是也给测试仪器厂商带来巨大的挑战。

为工程师提供匹配眼下乃至未来一段时间内高速串行信号测试需求的数字示波器,降低工程师测试信号的难度和复杂度,让他们把主要精力集中在产品设计上,而不是产品测试上,是具有领导地位的测试仪器产商不可推卸的责任。

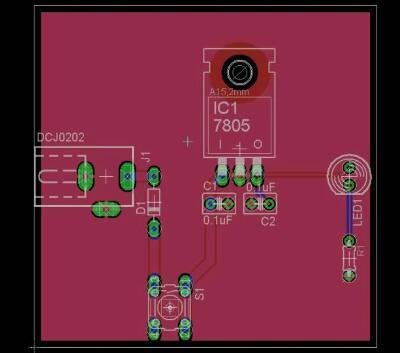

图1 QualiPHY串行协议一致性测试界面

APP下载

APP下载 登录

登录

热门文章

热门文章