每种架构都有其长处。通常情况是,每个系统供应商的设计决策归根到底都是平台的预期任务。从本质上讲,决策过程就是根据应用选择架构的过程。

数据包处理背景

数据包处理是数据密集型操作,需要优化的硬件。在宽带互联网出现之前,通用处理器既被用于控制会话处理又肩负用户流量的数据包处理。

但是,由数据和控制平面共享中央处理单元(CPU)资源的作法已被证明难以满足随带宽需求增长带来的更高要求。对于交换机和路由器来说,数据平面的数据包处理任务已转交给定制的固定功能ASIC或可编程网络处理器单元(NPU)。从而把通用CPU解放出来以专门应对控制平面任务。

有几家NPU供应商一直在试图针对2-4层包处理任务优化通用处理器,并提供集成了网络硬件(即物理层、媒体存取控制器和表存储器)以及用于特定任务(即散列)的硬件引擎的多核架构。在20世纪末20世纪初,MMC、C-Port和英特尔的IXP部门等机构开发了这类器件。

虽然这些产品各有不同,但它们的基本架构是相同的。通过降低复杂性,处理器核能够得到简化,从而使得器件内可以集成数十个处理器核以满足更高的并行要求。

除了极少数例外,这些NPU供应商在商业上都不成功。根本原因是这些NPU不能有效地满足超过10Gbps的网络应用对处理能力和存储器访问方面的要求。

现在,当我们迈进2010年,我们看到了旨在应对网络处理市场的新一代多核供应商的出现。虽然CMOS技术、存储器带宽和时钟周期性能得到了提升,但它们仍基于同样的基本架构。因此,这些新兴公司能期待获得更大的成功吗?

这将取决于它们针对的是哪类应用。现在的网络节点不仅处理2-4层的数据包,也需在更高层进行处理以支持服务和增加安全性。我们将研究其中的差异,以及对任何给定应用来说,为什么某些架构比其它架构效果更好。

线速包处理

2-4层数据包处理不同于其它网络应用(表1)。首先,能对所有大小的数据包进行线速处理是一个关键目标。现代路由器和交换机被设计为拥有广泛的网络功能,服务提供商期望能同时获得这些功能且不降低性能。

第二,数据平面将数据包视为独立个体,允许高度并行的处理。对一个100Gbps应用来说,网络处理器需要每秒处理1.5亿个数据包以确保线速性能。处理器10μs的延时相当于1,500个数据包的并行处理时间。

第三,数据平面程序需要高I/O存储器访问带宽以完成表查询转发、状态更新及其它处理。在高速平台上,数据包到达间隔时间非常短,因而对存储器延时提出了苛刻要求。对于小型数据包来说,执行这些任务的存储器带宽是链路带宽的数倍。

最后,当今网络的功耗很高。出于运营成本和环保两方面的考虑,服务提供商在煞费苦心地追求最佳的每瓦性能。考虑到包处理的特点,应以线速性能条件下、每瓦功率可实现的最高性能来衡量最有效的架构。

服务和安全处理特征

与数据包处理相近的市场是服务和安全处理。这些应用具有与2-4层数据包处理不同的特点。因此,可实施其它的硬件设计优化。

在客户机-服务器方式中,这些应用终止和处理主机至主机协议,或在中间网络节点(即防火墙、负载均衡器、入侵和防御系统)上处理重组的净载数据包数据。这些产品必须能够跨数据包边界工作,因为它们通常需要在更大的数据量上进行更大规模的操作,这将导致数据并行性较低。另一方面,相对所处理的数据而言,这类所需的I/O存储器带宽较低。

架构比较

NPU承诺可提供定制ASIC的性能,且具有通用处理器的可编程能力。但是,比较处理器的性能较困难,因为理论上的最大值通常与真实世界关联不大。此外,有效利用可用处理性能的能力,以及与处理容量相关的I/O存储器的利用情况也是影响处理器性能的因素。

因此,这种比较必须从设计层面开始。我们首先从一个通用多核NPU架构开始。多核NPU架构衍生于通用处理器架构,该架构希望通过增加处理器核来实现更高的并行处理能力。降低复杂性并移除当今通用处理器架构内不必要的功能(即浮点指令)可实现这一目标。

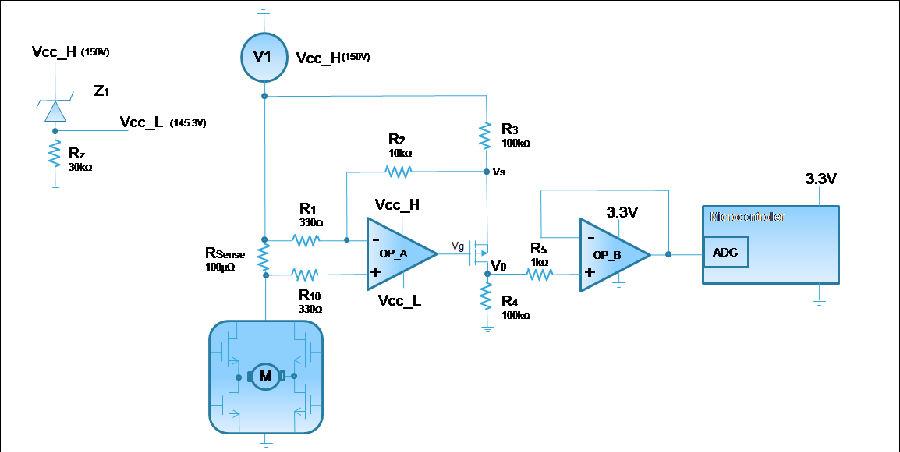

多核NPU架构对处理器核进行了专门分组。这些内核或被分组到各个并行池或以串行方式进行流水线排列(图1)。NPU供应商在设计时,允许架构对这种分组实施严格控制以优化性能。

图1:处理器核采用流水线或者并行池架构,混合模式也很常见。

如果定义得较松散,这种分组就允许程序员更自由地在内核间划分任务,最终结果是以性能控制为代价提供更大的灵活性。在许多情况下,多核网络处理器最终会以流水线和并行池的混合架构形态出现。

处理器核的分组对编程模式有重要影响。并行池带有相关的多线程编程模式,其中每个处理器核可运行一个或多个线程。从本质上讲就是程序获取一个数据包并对其执行一系列操作。

一旦处理完一个数据包,程序就准备好按顺序取用下一个数据包。程序员通过把数据包分配给不同的并行池来有效利用处理资源。线程之间的同步是程序员的另一个关键系统任务。

流水线模式处理数据平面应用,并将其划分为不同的处理任务(即:分类、修改、隧道处理以及状态更新)。然后,每个任务被映射到不同的处理器核,任务的执行或由架构强制完成,或交由程序员处理。由于吞吐量受限于速度最慢的部分,因此如何在各内核间有效地划分任务通常是个挑战。

通用多核架构内的数据包通常存储在共享存储器区域(图2)。在这种情况下,程序员必须将分类和数据包修改任务分别分配给处理资源的并行池和流水线。

图2:多核架构共享资源,以及用于处理器核和资源互连的高速总线或crossbar总线。

共享数据的复杂性

在并行数据包处理过程中,多个线程可能需要访问和更新诸如状态和ARP条目等共享数据。不同的线程需要进行同步以强制互斥并实现通用共享模式。但众所周知,同步并非易事而且会对性能造成影响。

为提高性能,许多多核处理器采用硬件缓存。虽然这可以极大缩短平均存储器访问延迟,但架构会变得更难以预测。

缓存一致性协议保证了采用缓存层次结构的多核系统中数据的完整性。虽然这对于程序员是透明的,但为了调节性能,程序员需要了解缓存和一致性协议是如何运作的。另一方面,存储器一致性模型也对程序员开放。因此,程序员需要了解存储器一致性模型以编写正确的程序。

保持数据包顺序

并行数据包处理的另一个挑战是保持数据包的顺序。所有节点都应针对相关的数据包保持数据包顺序,因为上层传输协议的正常工作依赖这种顺序。了解哪些类数据包需要保持包顺序以及如何最有效地满足这一需求通常是程序员的职责。

为降低复杂度,NPU供应商通常会提供硬件支持和软件库。添加更多的数据包缓冲器可有助于确保数据包顺序,但这总是以增加延迟为代价。

降低复杂性需求

驾驭基于多核的NPU并非易事。英特尔公司的Larry Huston在第10届高性能计算机体系结构国际研讨会上发表的论文中总结道:

“理想的情况应是,程序员将应用写成一段软件,而工具会自动划分应用并将应用映射到并行资源集。这也许是个难以实现的目标,但在该方向上的任一进步都将升华开发者的开发生命。”

数据流架构正好满足这一需求。虽然Larry Huston的上述见解发表在2004年,但它在今天的效用和意义与6年前一样。

确定性数据流架构

数据流架构(图3)采用了独特的方法,且具有处理器内核组成的单个流水线。该架构已被设计成完全确定性和超高效的。除执行语境外,它还包括一个数据包指令集计算机(PISC)和一个引擎接入点(EA

APP下载

APP下载 登录

登录

热门文章

热门文章