摘要:设计了一种在Nios II处理器上的CCD数据采集系统。电荷耦合器件(Charge-Coupled Device,CCD)采集到的信号经过前端的差分运放处理后再进行A/D转换,转换后的数据存储于外部SDRAM中,被读取后显示在LCD上。本文重点介绍了各器件的电路设计和驱动程序的编写。实践表明,该设计成本低,实时性较高。

关键词:Nios II;CCD;数据采集系统;AD9844A;驱动时序

引言

电荷耦合器件(Charge-Coupled Device,CCD)具有尺寸小、精度高、功耗低、寿命长、测量精度高等优点,在图像传感和非接触测量领域得到了广泛应用。大部分研制的数据采集卡将采集到的数据传入PC机,在PC机上编写程序进行数据处理,这种处理方法速度较慢,不适合对实时性要求较高的场合,且需要较大的平台。现场可编程门阵列(FPGA)由于其丰富的逻辑资源和较容易的硬件编程语言,在数据处理上得到越来越到的应用。本设计在FPGA上给出了一种基于Nios II处理器的CCD采集系统的设计,将采集到的信号经过一系列的处理后直接显示在LCD上,方便且实时性较高。

1 系统硬件设计

1.1 系统硬件结构

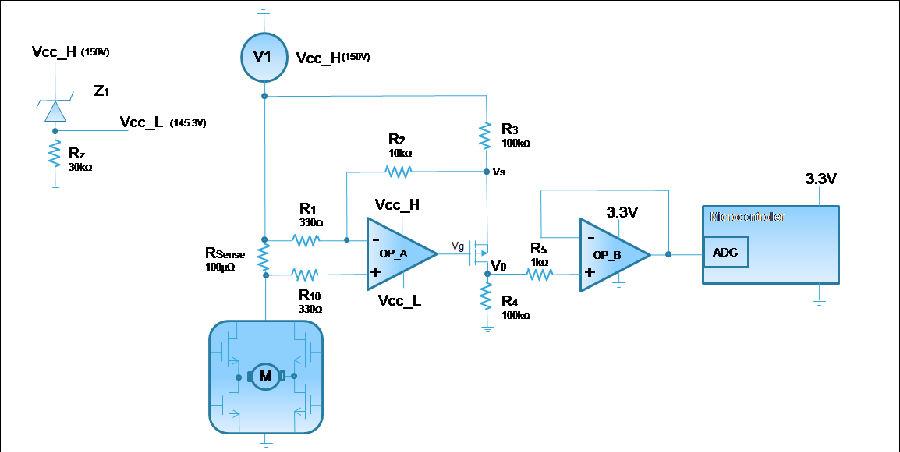

如图1所示,CCD采样控制器控制CCD进行采样,得到的信号经放大器AD623处理之后进入A/D采样电路,由A/D采样控制器控制,转换之后的数据存储于片上存储器中。系统所有的控制部分都由Nios II软核来完成,Nios II处理器将片上存储器中的数据逐一读取并进行处理之后显示在LCD上,Avalon总线负责各个控制器模块的数据传输。FPGA选用Altera公司的EP3C5E144C8。

1.2 分模块的设计

1.2.1 TCD1501D模块

根据工程项目的技术要求,本系统选用日本Toshiba公司的TCD1501D作为传感器,该器件是高灵敏度、低噪声和宽动态范围的线阵CCD器件。主要参数如下:

◆光敏像元数:5 000个。

◆像元尺寸:7μm×7μm×7μm。

◆光谱响应范围:300~1000μm。

◆灵敏度:10.4~15.6 V/(Lx·s)。

◆动态范围典型值:3 000 nm。

◆饱和曝光度典型值:0.23 Lx·s。

◆驱动时钟频率最大值:12 MHz。

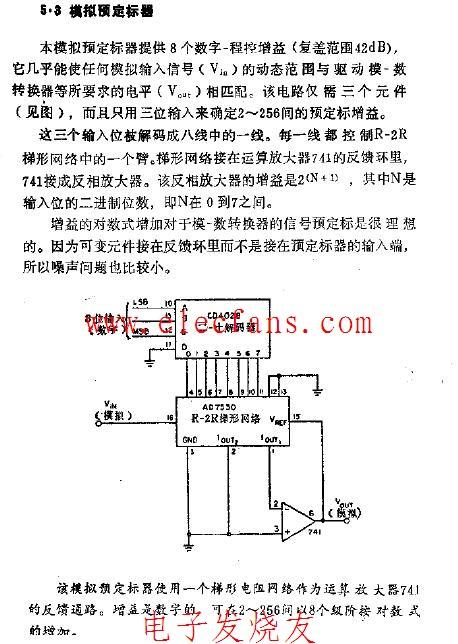

该器件正常工作的驱动脉冲主要有:复位时钟rs,移位脉冲f1、f2,转移脉冲sh,箝位脉冲cp和采样保持脉冲sp。该器件具有5 000个有效像元,正常工作还需要76个虚设单元信号。由于该器件是两列并行传输,所以在一个周期内至少需要2 538个f1(或f2)时钟脉冲才能完成一帧图像的转移。采用硬件描述语言(Verilog)的输入方式,设计各脉冲产生的程序,各驱动脉冲由基准时钟分频产生。其脉冲参数分别为:f1=f2=0.5 MHz,占空比为1:1,波形为方波,f1、f2在并行转移时有一个大于sh高电平的宽脉冲,脉宽为2 000 ns;复位脉冲rs=1 MHz,占空比为3:1,波形为方波;sh在转移时宽脉冲为1 000 ns;箝位脉冲cp和采样保持脉冲sp分别为rs脉冲的延迟。正确编译后,进行波形仿真,得到的仿真时序图如图2所示。

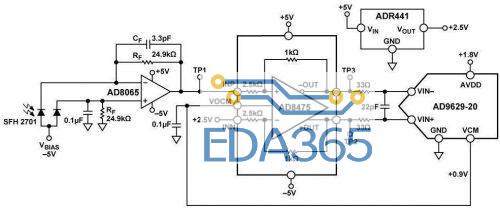

对比芯片手册要求的时序关系(如图3所示),各时序脉冲均满足芯片手册要求。其中,φ1B、φ2B即图2中的f1、f2,φTE.0就是f1、f2在并行转移时大于sh高电平的那个宽脉冲。

APP下载

APP下载 登录

登录

热门文章

热门文章