0 引言

直接数字式频率合成器(Direct Digitalfrequency Synthesizer,DDS)是从相位概念出发,直接合成所需波形的频率合成技术。VHDL是IEEE的工业标准硬件描述语言,可描述硬件电路的功能、信号连接关系及定时关系,在电子工程领域用来描述、验证和设计电子线路,得到了广泛应用。故将VHDL语言与DDS技术结合,设计生成BPSK信号。

1 DDS的基本原理

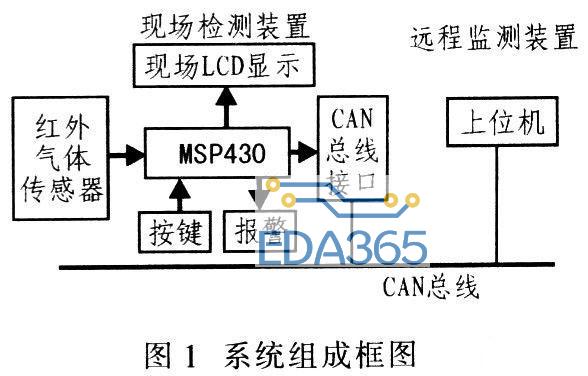

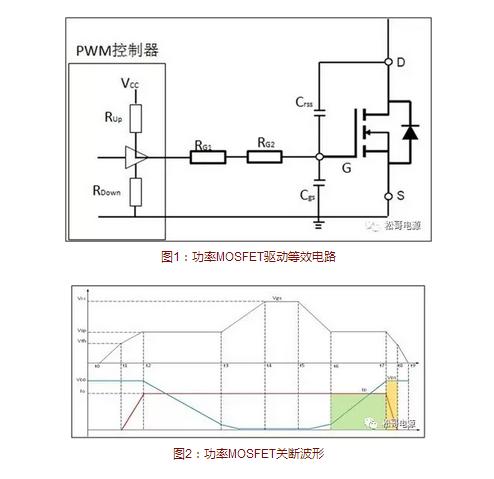

DDS把一系列数字量形式的信号通过数模转换器(DAC)转换成模拟量形式的信号,其基本结构如图1。

DDS由相位累加器、加法器、波形存储器(ROM)、数字乘法器、D/A转换器和低通滤波器(LPF)组成。DDS的核心是相位累加器,由一个加法器和一个相位寄存器(REG)级联构成。在参考时钟fc的控制下,相位累加器对频率控制字K进行线性累加,输出的和再与相位控制字P相加后作为地址,对ROM寻址。ROM中存放经过采样、量化处理后的周期性连续信号一个周期波形的幅度值,即与一个周期的相位采样相对应的函数波形查找表,不同相位地址对应周期信号的不同幅度值编码。ROM输出的幅度值编码通过数字乘法器被幅度控制字A加权,加权后的幅度值编码经D/A转换器变成阶梯波,再经低通滤波器平滑后就可得所合成信号的模拟波形。合成的信号波形取决于ROM中存放的幅度值数据,故用DDS可产生任意波形。

设相位累加器的字长为N,则DDS的输出频率f0和频率分辨率(即最小输出频率)△fmin分别为:

只要N足够大,DDS可以得到很小的频率分辨率。要改变DDS的输出频率,只要改变频率控制字K即可。

根据Nyquist采样定理,在对连续信号进行采样的一个周期内,采样频率不能改变,故利用DDS进行信号合成时,在信号合成的一个周期内,频率控制字K不能发生变化,也就是K在每次改变之前至少应该持续2N/K个DDS时钟周期,即2N/K/fc。

通过改变相位控制字P,可以控制输出信号的相位参数。设相位加法器的字长为M,当相位控制字由0变到P(P≠0)时,ROM的输入为相位累加器的输出与相位控制字P之和,因此,其输出的幅度值相位会增加2πP/2M,从而使最后输出的模拟信号产生相移。

DDS输出信号的幅度可以通过在ROM之后加入一个数字乘法器来实现。幅度控制字A起到对ROM所输出的幅度值编码进行加权的作用。

可见,当DDS的相位累加器字长和相位加法器字长确定后,通过改变K、P、A就可以有效地控制DDS输出的模拟信号的频率、相位和幅度,这就是DDS技术的调制特性。

2 采用VHDL语言实现DDS

为简单起见,以下所描述的DDS仅设置了频率控制字K,相位控制字P和幅度控制字A都未予以考虑,其处理可类推。DDS的输出为正弦波信号。

由于正弦波关于π奇对称,关于π/2与3π/2偶对称,因此波形存储器(ROM)中只需存储其1/4个周期的幅度值编码。具体地,ROM中存储正弦波0~π/2相位范围内的256个采样点的幅度值,采用8位编码。而DDS的输出为9位,最高位作为符号位,用以区分幅度值的正负,“0”表示正,“1”表示负。ROM为8位地址寻址,而相位累加器的字长采用10位。最高位用以区分正弦波的前、后半周期,“0”为前半周期,幅度值为正,“1”为后半周期,幅度值为负。次高位用以区分正弦波前、后半周期的前、后1/4周期,“0”为前1/4周期,寻址地址为相位累加器的低8位,“1”为后1/4周期,寻址地址为相位累加器低8位的取反。

用VHDL实现DDS的源程序的核心部分如下:

在Xilinx ISE 8.2i开发环境中对其进行仿真的结果如图2。

APP下载

APP下载 登录

登录

热门文章

热门文章