随着软件无线电的发展,中频数字接收机作为电子侦查系统中的一个关键环节已经越来越受到人们的关注。

本设计主要是研制基于固定中频数字下变频的中频数字接收机。本设计通过对五通道中频数字接收机软硬件的简单介绍论证了其可行性,并对实验结果进行了简单地分析。

本设计的软件部分全部在一片FPGA内完成,提高了系统的运行速度。

1 硬件设计

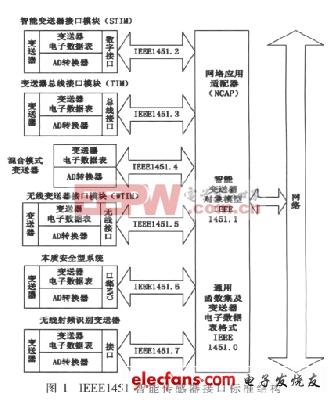

五通道数字接收机的系统框图如图1所示,它由五路调理电路、五路A/D变换器、时钟、FPGA以及外围电路组成。中频信号经过信号调理电路后,差分信号经A/D变换器采样送到FPGA进行处理,并将提取的I、Q信号送到测向处理器进行处理。信号的中心频率为150 MHz,采样频率为200 MHz。

1.1 变压器的选择

由于A/D变换器要求差分输入,本设计采用2个变压器级联的方式实现模拟信号的差分转换,其连接方法见图2所示。采用这种级联方式可以提高耦合系数从而使相位稳定。本设计变压器选择Mini-Circuits公司的ADT1-1WT变压器。

1.2 A/D变换器的选择

本设计信号的中心频率f0=150 MHz,带宽B=10 MHz,根据带通采样定理:设一个频率带限信号x(t),其频率限制在(fL,fR)内,如果其采样频率满足

上式中,n取能满足fs≥2(fR-fL)=2B的最大整数,则用fs进行等间隔采样所得到的信号采样值x(nTs)能准确的确定原信号x(t)。式中带通信号中心频率f0和频带宽度B也可以表示为:

上式中,n取能满足fs≥2B的正整数。本设计中选用的采样频率为200 MHz。

本设计中A/D变换器选用ADI公司的AD9230BCPZ-250。工作频率最高可达250 MHz。AD9230采样输出数据为12 bit,精度高,而且片内集成了高性能采样保持放大器和电压参考,最大700 MHz模拟差分输入带宽。此芯片为双端输入,更适合对差模信号进行采样量化。

1.3 时钟芯片的选择

由于本设计的采样频率比较高(200 MHz),为了保证A/D变换器的最佳性能,要求提供高精度、低抖动的时钟信号。本设计选用AD95163作为系统时钟。AD9516是一款时钟综合芯片,片内集成的VCO产生频率范围为1.75~2.25 GHz,其输出可以提供CMOS、LVPecl、LVDS三种时钟电平,而且有14通道时钟输出。可以通过配置内部寄存器改变其输出的时钟频率,以满足不同设计的要求。

APP下载

APP下载 登录

登录

热门文章

热门文章