0 引言

基准电压源广泛应用于各种模拟集成电路、数/模混合信号集成电路和系统集成芯片(SoC)中,是集成电路的一个基本元件,其稳定性直接影响到整个系统的精度。然而,传统的高性能基准电路普遍采用带隙基准电路,与标准CMOS工艺不兼容。为了解决带隙基准电路与标准CMOS工艺不兼容问题,一些学者提出了一定的解决方法,例如:利用N阱的寄生二极管设计带隙基准,利用CMOS管的亚阈值区工作原理设计基准,利用载流子和阈值电压在不同温度下的特性设计基准等。但是他们的电源抑制比普遍偏低,且温度系数较大。

本文利用高电源抑制比电路设计的和式偏置电流源进一步提高了电源抑制比,并利用NMOS和PMOS管的两个阈值电压VTHN和VTHP具有相同方向但不同数量的温度系数,设计了一种基于不同VTH值的新型CMOS基准。该设计充分利用CMOS器件高输入阻抗、低功耗的特点,利用相同电流减少了载流子迁移率对温度性能的影响,利用VRHN和VTHP温度系数抵消原理和高电源抑制比和式电流源,大大降低了基准的温度系数,提高了电源抑制特性,使电路的性能得到优化。

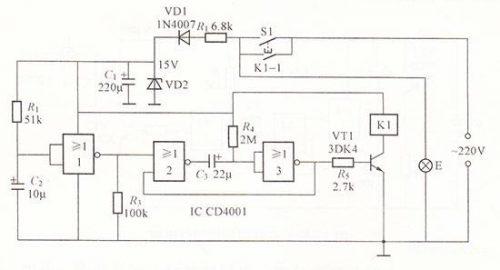

1 传统带隙电路原理

如图1所示,传统的带隙电路主要是利用双极型晶体管的基极-发射极电压VBE具有负温度系数,而两个不同电流密度的双极型晶体管之间的基极一发射极电压差△VBE具有正温度系数,将其乘以合适的系数K后,再与前者进行加权,即:VREF=VBE+K△VBE,从而在一定范围内就可以抵消VBE的温度漂移效应,得到低温漂的输出电压VREF。K值将通过把VBE的表达式带入VREF中,在参考温度T0处令求得。

但是使用BJT管会占用很大的芯片面积且与在标准CMOS工艺中不能很好的兼容。

2 新型CMOS基准电路原理

对于CMOS器件,其阈值电压VTH和载流子迁移率μ是主要的受温度因数影响的参量。虽然阈值电压VTH和载流子迁移率μ的值都随着温度的升高而减小,但是MOS器件阈值电压VTH和载流子迁移率μ的下降对于MOS管的漏电流ID有着完全相反的效果:阈值电压VTH越低,漏电流ID越大;而载流子迁移率μ越小,漏电流ID越小。

由文献可知,阈值电压VTH与环境温度有着近似的线性关系:

式中:aVT是阈值电压VTH的温度系数,其值介于1~4 mV/℃之间,对NMOS和PMOS是相互独立且不同的。

载流子迁移率μ和环境温度的关系为:

式中:μ(T0)是某基准温度时的载流子迁移率,且m介于1~2.5之间。

由式(1)可知,VTHN和VTHP具有不同的负温度系数,只要取合适的系数K时:

就可以得到不随温度变化的基准电压VREF。

APP下载

APP下载 登录

登录

热门文章

热门文章