本应用笔记将详细说明用于同步多个AD9779器件的数字数据输入的方法。DAC输出的相位对齐通过设计保证,精度小于一个DACCLK输出周期。然而,由于输出延迟不匹配(室温下及冷热温度下),多个DAC输出的相位对齐可能存在细微的不一致,本应用笔记不讨论这一问题。

同步方案

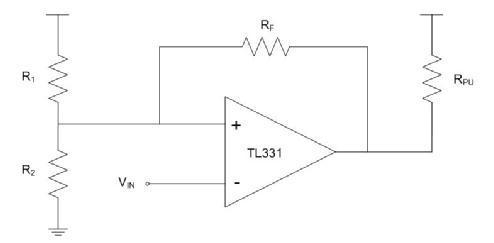

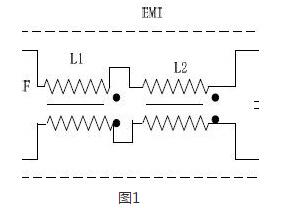

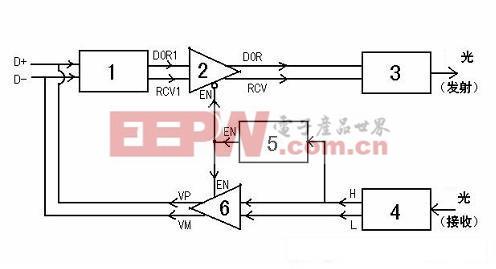

同步多个AD9779 DAC有两种方案。在第一种方案中,一个器件用作主器件,其余器件用作从器件。在第二种方案中,所有器件都是从器件。两种方案具有相同的时序限制,不存在性能权衡。主/从模式和从模式的框图分别如图1和图2所示。

图1. 主/从SYNC_I/O分配

图2. 从SYNC_I分配

同步详解

工作中,差分时钟信号驱动所有主器件和从器件的AD9779 REFCLK输入。REFCLK输入接收器是一个高增益差分放大器,各差分输入需要接近400 mV的共模输入电平和至少400 mV p-p的摆幅。

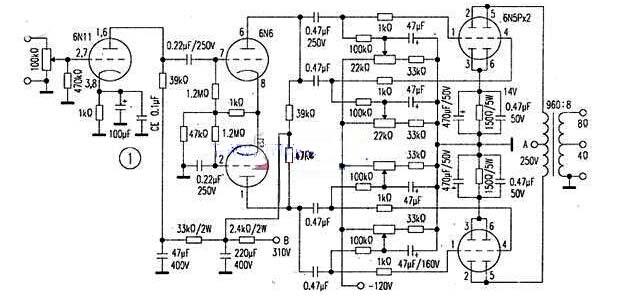

如果选定了主器件,可以使能主器件的差分LVDS输出信号,该信号称为SYNC_O+和SYNC_O?.通过寄存器0x07的位5,可以将SYNC_O设置为在DACCLK的上升沿或下降沿触发。SYNC_O还有一个可编程的延迟,可以通过寄存器0x04的位0 (MSB)和寄存器0x05的位[7:4] (LSB)设置。SYNC_O通过将同步驱动器使能位(寄存器0x07的位6)置1而使能。SYNC_O信号速度可以是REFCLK速度的整数除数,通过寄存器0x04的位[3:1]设置。主器件的REFCLK输入和SYNC_O信号的可能时序情况如图3所示。

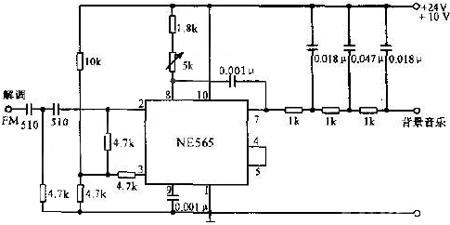

图3. DACCLK SYNC_O时序

APP下载

APP下载 登录

登录

热门文章

热门文章