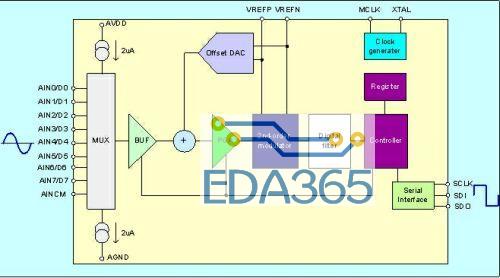

在ISSCC 2009的“Session 4 High-speed Data Converters”上,多家企业和大学就各种转换器发表了技术论文,包括12bit 2.9G样本/秒的D-A转换器(论文编号4.1:美国博通)1篇、Folding型A-D转换器(论文编号4.3,美国国家半导体)1篇、非同步二分法检索(Binary Search)型A-D转换器(论文编号4.4,台湾国立成功大学)1篇、采用时间交叉法的高速逐次比较型A-D转换器两篇(论文编号4.2,美国卡耐基梅隆大学;论文编号4.5,美国伊利诺大学),以及管线型A-D转换器两篇(论文编号4.6,美国加州大学洛杉矶分校;论文编号4.7,美国模拟器件)。其中,除了博通公司的D-A转换器和台湾成功大学的A-D转换器之外,其他5篇论文的共同点是,均采用数字助理技术对速度提高带来的精度问题进行了补偿。

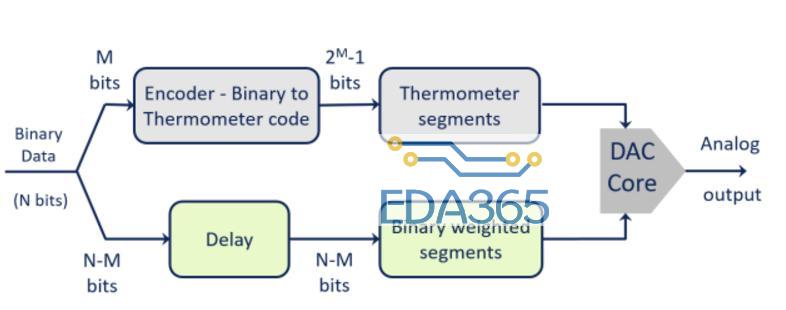

发表论文4.1的博通公司在不采用数字助理技术的情况下,通过改进内部电流源单元的纯模拟方法,在1GHz时实现了IM3>60dB。该性能达到了原来使用BiCMOS时耗电量超过1W才能实现的水平。

发表论文4.4的台湾成功大学通过大幅减少IMEC在ISSCC2008上发布的非同步二分法检索型A-D转换器的比较器数量,以2mW的耗电量实现了5bit、800M样本/秒的性能。该方式介于嵌入式和逐次比较型之间,不过大幅改进了尺寸方面的缺点。

论文4.2和4.5均采用时间交叉法运行逐次比较型A-D转换器,从而获得了较高的速度。通过数字补偿技术对时间交叉法特有的问题——各通道的时间、增益及偏移量误差进行了补偿。

论文4.3发表的是内部可实现36(=726)这一Folding Driven高系数(历史最高)的A-D转换器。考虑到要用于通信用途,Ich及Qch均采用补偿技术统一了线性,从而实现了10bit、1G Sample/秒的性能。

论文4.6和论文4.7均在管线型A-D转换器中采用了数字助理技术,分别实现了“10bit,500M Sample/秒”及“16bit,125MSample/秒”的性能。均可涵盖采用模拟设计能够实现的区域,采用数字技术对其他区域进行补偿后,可达到原来2倍以上的速度。两篇论文的内容都十分充实。

高性能化是A-D转换器及D-A转换器一成不变的要求。作为其发展方向,此次会议可使人们认识到数字助理技术的潜力。但是,除论文4.3外,上述补偿处理都是由片外软件完成的。从片上实时处理尚未成为主流这一点可以知道,将来的课题也会同时出现。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多