在当前SoC 快速发展及半导体行业激烈竞争的阶段,提高测试效率、降低测试成本,是从业者需要思考和解决的课题。

Verigy 93000 是单一平台的可升级测试系统,它是满足SoC 技术全面集成需要的芯片测试系统解决方案。

本论文阐述一种测试方法使得Verigy 93000 进行直流参数测试时独立并行使用硬件资源,从而节省测试时间,提高测试效率。

2 Verigy 93000 用于DC测试的硬件资源

2.1 PMU(parameter measure unit,参数测量单元)

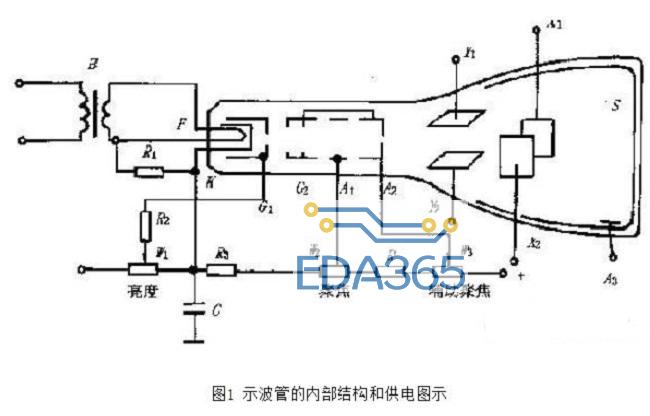

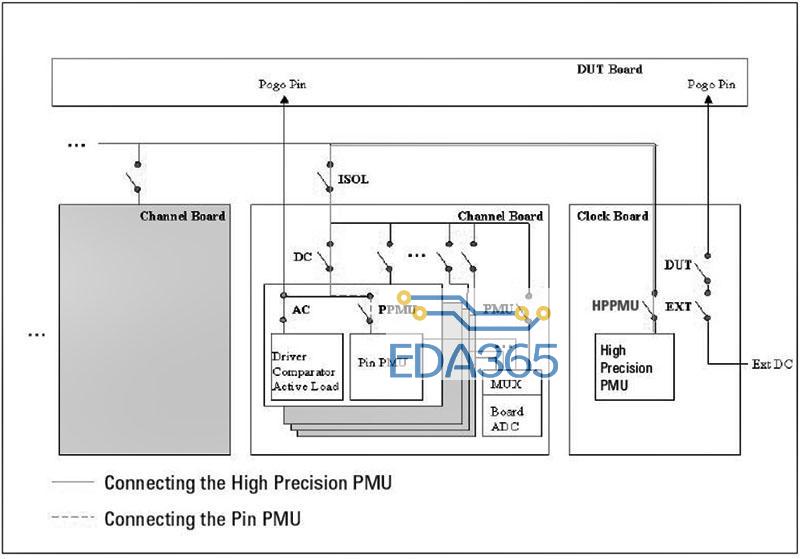

PMU 是Verigy 93000 进行DC 测试最常用的硬件资源(如图1 所示)。当前应用最广泛的Pinscale测试系统中的PMU 有两种, 一种称为PPMU(Per- Pin PMU),包含在每个数字通道内。根据测试系统的配置结构,大头可以达到2048 个,小头1024个;另一种HPPMU (High Precision PMU,高精度PMU),每个Group中一个,大头有8 个,小头结构就只有4 个。因此在测试中,只要PPMU 的参数范围和精度满足芯片需求,我们尽可能使用PPMU,并通过合适的编程方法做到硬件资源完全并行使用,加快测试速度。

图1 93000 的PMU 资源

2.2 Verigy 93000 的DPS (DevicePower Supply,芯片供电电源)资源

Verigy 93000 中每块DPS 板卡可以提供8 路电源通道,电源通道除了给芯片提供电源外,还具有加电压测电流的功能,这通常用于芯片的功耗测试。

本文不就此类测试展开讨论。

3 PPMU 资源完全并行使用的测试方法

PPMU 是Verigy 93000 中每一个数字通道都有的硬件资源,它具有加电压测电流(VFIM)和加电流测电压(IFVM)两种功能。应用这两种功能进行DC 测试,通常有两种实现方法。

1) 传统方法:通过调用PPMU 相应的API(可编程应用接口) PMU_VFIM (加电压测电流)和PMU_IFVM(加电流测电压)来实现。但应用这种方法进行测试时,如果不同的管脚需要不同的测试条件,测试时每个管脚是串行执行的,这样机台per- pin 的PMU 资源的优势就没有得到最好发挥,测试时间会相应增加。

2) Flex DC 测试方式:可以做到使用PPMU 测试不同条件的PIN 时完全独立,互不影响。因此,在使用PMU 进行DC 测试时,为了提高测试效率,增加产出,在测试条件允许的情况下,测试者尽可能采用这种方法。

两种方法的比较如表1 所示。

表1 两种DC 测试方法的比较

3.1 Flex DC 编程方式的具体实现

Flex DC 测试方法在程序中通过PPMU_SETTING、PPMU_RELAY、PPMU_MEASURE以及TASK_LIST 创建任务列表的方法来实现。此时,我们需要把不同测试条件的PIN 对应的PPMU的工作模式及条件范围、RELAY 的状态、测试结果的获取分别设定为相同的SETTING、RELAY 和MEASURE 中,然后把上述设定添加到同一个任务列表中。这样, 对于上述SETTING、RELAY 和MEASURE 中的不同pin 包含的动作,机台在执行测试的过程中是完全独立并行的,可以做到资源的最优利用。

以2 个pin 为例,pin1 测试中需施加5 V 电压测电流,pin2 要施加2.5 V 电压测电流,Flex DC 的代码如下:

PPMU_SETTING set1;

PPMU_RELAY relay1;

PPMU_MEASURE measure1;

TASK_LIST task1;

set1. pin( pin1 )。 vForce( 5 V)。iRange( 40mA)。min( 0 mA)。max( 50 mA);

set1.pin( pin2 )。vForce( 2.5 V)。iRange( 40mA)。min( 0 mA)。max( 40 mA);

relay1.pin(pin1, pin2)。status(“PPMU_ON”);

measure1.pin (pin1, pin2)。execMode (TM::PVAL);

task1.add(set1)。add(relay1)。add(measure1);

task1.execute( );

以一款电源芯片为例,该芯片大部分为DC 测试项,另加小部分功能测试。下面我们来看测试中采用Flex DC 测试方法和直接采用PPMU_IFVM进行测试,测试时间的对比情况。(如表2 所示)。

表2 一款电源芯片两种测试方法的参数比较

表中对比可以看出,如不对测试程序进行优化,单芯片测试时相差0.6 s,双芯片同时测试相差0.9s;对测试程序进行优化(主要针对多芯片测试,使不同位置的芯片测试中能并行进行的动作同时执行),时间差值就更明显,单芯片为0.9 s,双芯片达1.6 s。可见,采用Flex DC 的测试方式,可以有效减少测试时间。

4 小结

结合Verigy 93000 SoC 测试机台的特点,讨论了一种DC 测试资源的并行使用方法。结果表明该方法在测试中能完全并行使用硬件资源,使测试时间有效降低。

APP下载

APP下载 登录

登录

热门文章

热门文章