1. 数字ATE特性

测试工程师能够从具备多种应用特性的不同数字I/O仪器中选择合适的设备进行通信与测试。数字测试设备的核心特性是能够生成硬件定时以及/或实现预定义数字测试模式的采集,这些模式通常存储在设备所包含的存储器中。数字仪器已经超越了驱动1和0等数字模式功能,它通常支持包含部分或所有表1所列出的逻辑状态的波形。

表1:部分数字测试设备支持的数字逻辑状态

逻辑状态 | 驱动数据 | 期望响应 | |

驱动状态 | 0 | 逻辑低 | 无关 |

1 | 逻辑高 | 无关 | |

Z | 禁用 | 无关 | |

比较状态 | L | 禁用 | 逻辑低 |

H | 禁用 | 逻辑高 | |

X | 禁用 | 无关 |

如表1所示,六种逻辑状态控制电压驱动器和数字测试仪的比较引擎(如果可以被支持)。这些状态指定测试仪在特定的通道中驱动哪些激励数据以及被测设备的期望响应。当这些状态出现在数字测试仪器中时,它们能够完成双向通信以及采集响应数据的直接比较。

NI 655x数字波形发生器/分析仪支持表1中所示的全部6种逻辑状态。以下章节解释了这些特性的硬件实现,提供了每周期双向控制和实时硬件比较的更为详细的分析。

2. 每周期双向控制

通信方向控制功能是为被测设备选择数字测试系统的十分关键的特性。最基本的数字I/O仪器包含简单的单向控制,这意味着一个通道不是将数据传送到管脚上就是进行数据采集。更为复杂的设备可以被配置为将激励数据驱动到管脚上,或是从该管脚采集数据,但无法在同一操作中完成。两个基本的逻辑状态,1代表驱动逻辑高,0代表驱动逻辑低,能够控制这些设备所有的发生操作。它们无法在同一个操作中支持双向功能。这些设备的典型应用包括基本模式I/O、握手和数字数据记录。

更为复杂的数字测试仪允许在同一个数字操作中完成双向功能,这意味着仪器能够在连续的时钟周期内,在发生数据和采集数据之间进行切换。为了支持双向控制,由于激励通道必须还能够禁用电压驱动器,因此需要超过两种基本逻辑状态。第三种状态称为三态,或者也通常被称为高Z状态或是高阻状态。三态提供了在一个设备正在驱动一个通道时,确保不会有多个设备同时驱动这个通道的控制能力,否则可能会导致接收到错误的数据。三态对于I2C通信、IC测试、比特错误率测试(BERT)和通用数字激励/响应测试等双向应用而言是必须的。

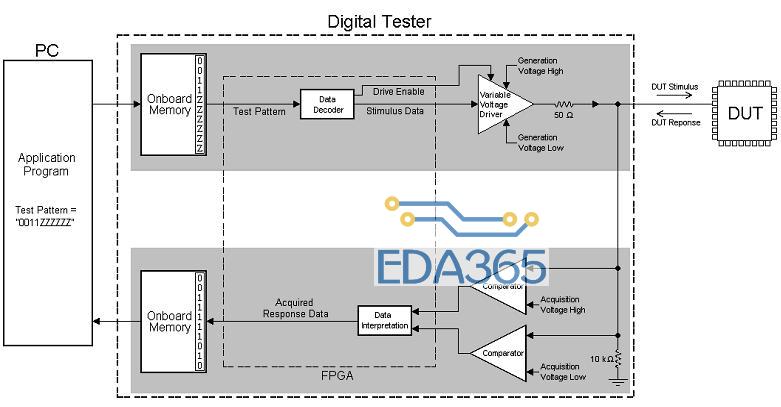

NI 655x支持每通道、每周期三态,或者也称为高阻抗和“Z”状态。图1显示了单一三态通道是如何在NI 655x数字波形发生器/分析仪的FPGA实现的。在图中,发生逻辑显示在数字测试仪的上半部分,采集电路在下半部分显示。

图1:单一NI 655X数字通道的方块图

典型的双向设备测试,例如存储器存储器芯片等,首先需要将激励数据或测试模式下载到数字测试仪的板载存储器中。然后,激励数据经过解码,决定是否需要激活通道电压驱动,如果需要激活,那么应该激活哪些数据的驱动。在NI 655x设备中,采集电路比较器直接连接到数字测试仪电压驱动器的输出上。这意味着来自数字测试仪和被测设备的激励数据可以用NI 655x进行采集。由于比较器无法分辨是被测设备还是数据测试仪(或者两者都是)将数据传送到通道中,所以您必须在读操作中将数字测试仪的电压驱动器设置为三态,防止数据同时从被测设备和数字测试仪的电压驱动器传送到通道中。

在完成信号采集之后,数据解码电路判断采集信号是逻辑低还是逻辑高,并将结果存储在板载存储器中。采集得到的响应数据最终被写入PC中,进行分析和记录。下一章节将这个方块图进行进一步扩展,引入了NI 655x设备能够对采集响应数据进行直接比较的特性。

3. 实时硬件比较

另一个数字测试仪器的重要功能是验证被测设备在不同用户使用情形和激励数据的情况下,都能够返回正确响应数据的能力。为了实现这个目标,主要有两种将采集的响应数据与预期数据进行比较的方法。第一种方法是采集实际响应数据,并使用软件解释结果。应用程序只需要两种基本逻辑状态来配置测试仪的激励数据。另一种方法是将激励数据和预期响应数据预先载入硬件中,确保在采集数据的同时进行实时数据比较。过去,第二种方法只适用于高价的数字测试仪,现在强大低价的FPGA技术通过使用表1列出的三种比较状态,实现实时硬件比较,极大地扩大了这种功能的用户群体。只要波形包含比较状态,采集的响应数据就能够与预测响应进行比较。

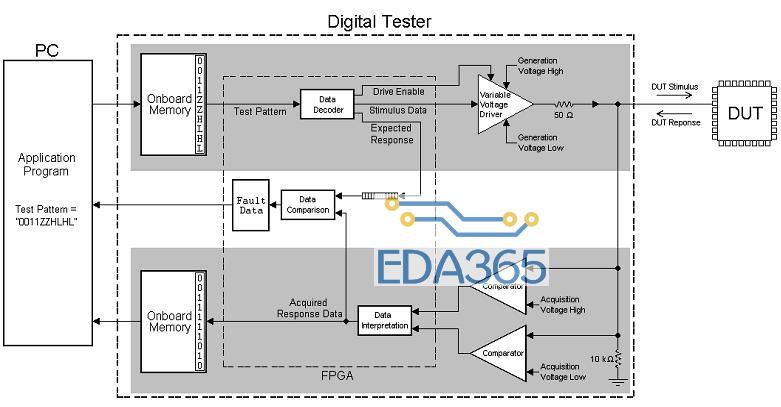

图2显示了带有硬件比较电路和之前讨论过的每通道三态特性的NI 655X通道的完整方块图。

图2:带有硬件比较电路的NI 655X数字通道的方块图

FPGA的数据比较逻辑将发生电路与采集电路结合在一起。数据解码器从板载存储器接收数据,根据每个采样的逻辑状态启用或禁用驱动器。解码器将预期响应传送到FIFO存储器中,在响应数据开始采集的时候,将预期数据传送到数据比较逻辑中。如果在比较的过程中检测到了错误,出错信息将与采集数据分开存储,确保这些数据可以使用应用软件进行访问,用于进一步的分析。

FPGA为每个检测到的错误存储以下信息:

- 错误采样数

- 出错通道

- 错误总数

4. 常见数字测试应用

本小节解释了如何实现之前章节所讨论的用于通用数字测试应用的数字ATE特性,例如功能测试和特征提取。

功能测试

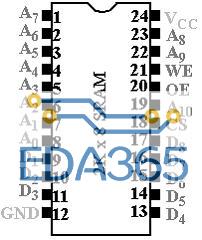

对于许多行业而言,最重要的测试之一是元件功能测试,例如定制ASIC和商业A/D转换器。需要扩展功能测试的常见双向设备是存储器芯片。图3显示了一个典型的SRAM集成电路(IC)及其管脚输出。

图3:SRAM IC管脚输出

如前所述,典型的存储器集成电路包含三条地址线、八条数据线、一条写启用(WE)线和一条读启用(OE)线。表2显示了一组可以用于测试这块SRAM芯片的数字测试模式。

表2:存储器集成电路的数字测试模式

| 采样 | 测试数据 | 实际响应 |

W/R | 地址数据 | |

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 | 10 000 01111111 10 001 10111111 10 010 11011111 10 011 11101111 10 100 11110111 10 101 11111011 10 110 11111101 10 111 11111110 01 000 LHHHHHHH 01 001 HLHHHHHH 01 010 HHLHHHHH 01 011 HHHLHHHH 01 100 HHHHLHHH 01 101 HHHHHLHH 01 110 HHHHHHLH 01 111 HHHHHHHL | 01111111 10111111 11011111 11111111 11111111 11111011 11111101 11111110 01111111 10111111 11011111 11111111 11111111 11111011 11111101 11111110 |

在WE(写启用)置为高电平时,IC芯片从数字测试仪等外置设备接收数据,并将数据写回由地址线指定的位置中。如果OE(读启用)置为高电平,集成电路从地址线所指定的位置接收数据,并将数据驱动至数据线上。验证这种存储器设备的最后一个步骤是通过比较预期响应分析输出。

下面两个小节讨论了使用NI 655x数字波形发生器/分析仪,在LabVIEW中,利用软件解决方案和硬件解决方案实现功能测试。

软件比较方法

在软件比较应用中,测试仪生成激励数据、采集实际响应数据,然后在存储到主机PC存储器之后完成响应数据的分析。实际响应数据分析完全是在软件中进行的,而不是实时完成的。下面的步骤更为详细地描述了软件比较。

1、如图所示,原始测试数据是用户输入或通过文件读取的。测试数据包含了激励数据和响应数据。

表3:测试向量与激励数据的转换

测试数据 | 0011ZZHLHL |

激励数据 | 0011ZZZZZZ |

2、如图所示,纯激励数据是从测试数据中提取的,测试数据中的1和0表示激励数据;所有其他的字符表示没有数据生成,因此电压驱动器必须被置入三态禁用。

3、激励数据通过数字测试仪生成并送入通道中,之后采集响应数据。发生操作和采集操作并行运行。

4、在完成发生和采集之后,应用程序在软件中完成以字节为单位的比较。给出的例子是采集的响应数据。只有当“H”或“L”出现在原始测试数据中的时候,最终通过/不通过的判断才会受到所采集的响应数据的影响。

表4:测试向量与实际响应数据的比较

测试数据 | 0011ZZHLHL |

采集到的响应数据 | 0011111010 |

结果 | 通过 |

软件比较要求所有数据传送到主机计算机,进行后处理,使之适合于低速应用。如果所采集到的数据超出了测试仪板载内存的大小,将所有数据传送到主机计算机可能会超出计算机的带宽限制。在这种情况以及其他需要更高比较速率的情形下,必须使用实时硬件比较。

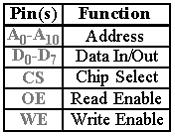

NI LabVIEW是一种图形化编程语言,下面用LabVIEW展示了NI 655x设备的数字软件比较应用的功能。下面的几张图片展示了如何建立独立的发生操作和采集操作,以及如何将它们合并在一个同步功能测试应用中。

首先,图4显示了如何建立发生部分的LabVIEW程序。其中的关键功能包括配置测试仪、读取测试模式并开始进行发生。

图4:LabVIEW高速数字发生程序

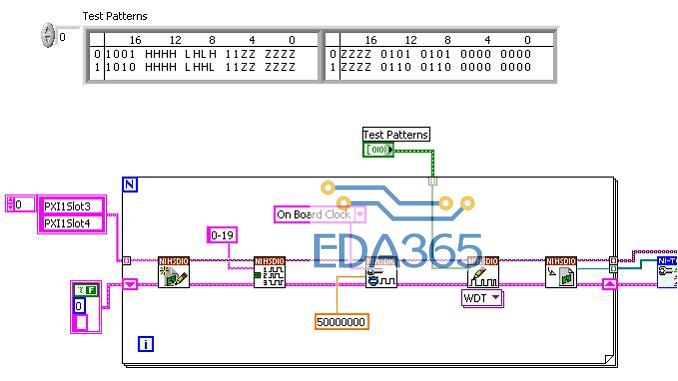

在测试数据被载入板载发生内存之前,在图5中所示的原始数字测试数据被解释为激励数据和预期响应数据。在数据被解释之后,激励数据被下载到NI 6552进行发生。

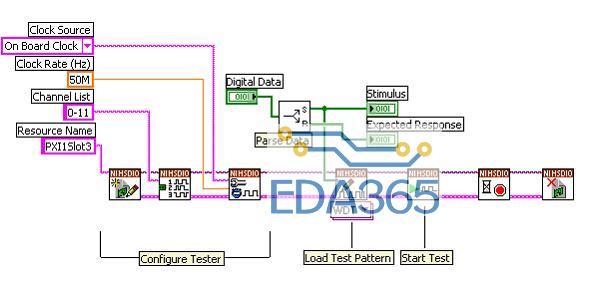

建立程序的采集部分十分相似。图6给出了功能测试应用所需的采集程序。

图6:LabVIEW高速数字采集程序

尽管NI 6552支持这两个程序同时工作,但是简单地将它们组合在一起并不是有效的测试方法。简单地同时运行我们的采集程序和发生程序并不能将采集数据与预期响应数据对齐。由于这些程序运行在非确定性软件中,您无法依赖程序的定时来保持一致性。此外,通过被测设备和连接被测设备电缆的传递延迟也必须考虑。数据从数字测试仪通过电缆和被测设备流回测试仪所需的时候称为全程延迟,在图7中标出。

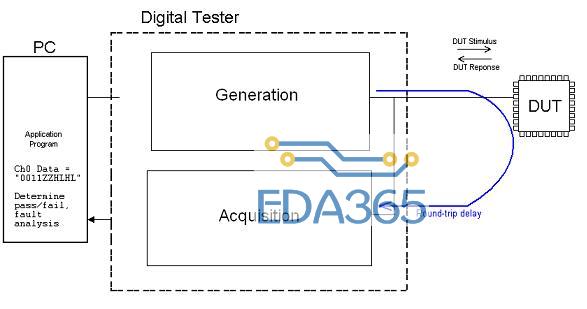

图7:使用外部连接解决全程延迟

解决全程延迟和软件延迟的最佳方法是输出与测试开始对应的边沿信号。对于NI 655x而言,数据活动事件提供了这个功能,并且可以输出到外部来触发采集的开始,如图8所示。注意,必须确保信号的回路与数据具有相同的全程延迟。

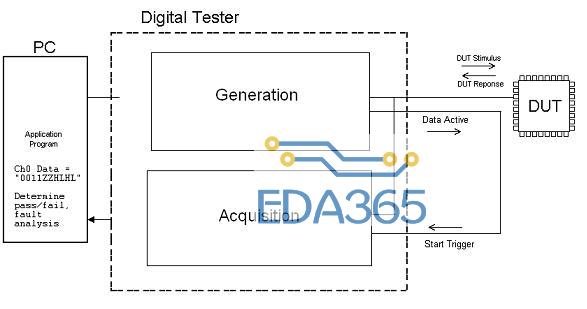

图8:使用数据活动事件触发从发生信号进行采集

您还可以使用数据活动事件控制响应数据和采样时钟活动边沿的相对延迟。举例而言,您可以将数据活动事件输出到PFI 1上,并路由到PFI 2上,PFI 2可以配置为采集开始触发的信号源,如图8所示。您还可以将发生采样时钟输出到DDC CLK OUT,并将采集采样时钟设置为STROBE。

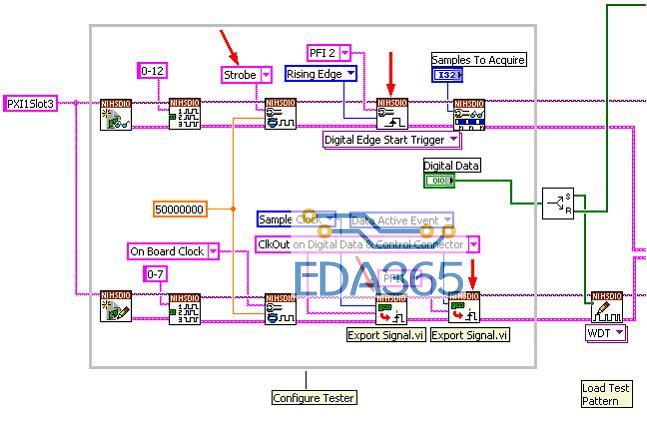

图9显示了配置和外部路由数据活动事件和采样时钟的LabVIEW程序。标有箭头的函数可以完成所需的额外配置。

图9:使用数据活动事件和输出采样时钟同步发生和采集

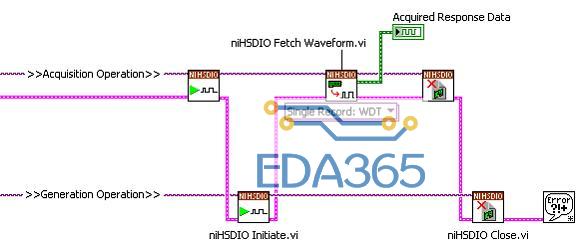

如图10所示,采集操作必须在发生操作之前开始,以便确保采集操作在发生操作开始之前,做好接收开始触发的准备。最后可选的步骤是分析采集到的数据,您可以用来得到一个是否通过的简单结果。无需将采集的响应数据进行详细软件分析,下面的小节会讨论如何使用实时硬件比较特性,实现比软件更高效地完成分析。

图10:确保采集已经在发生开始之前就绪,能够接收开始触发信号

实时硬件比较方法

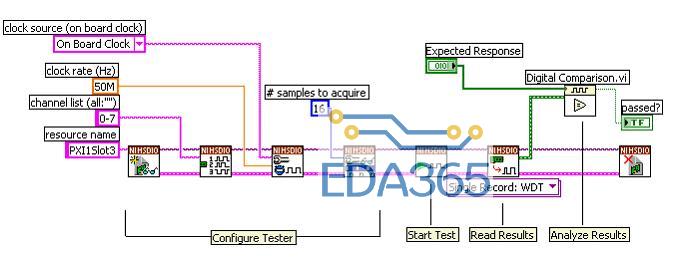

利用板载FPGA完成采集响应数据与预期数据的比较,能够大大提高速度和激励响应程序的可靠性。要开发使用硬件进行响应数据比较的程序,只需要对之前描述的LabVIEW软件比较程序进行少量的改动。

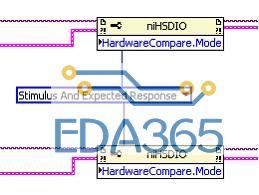

1、在发生环节和采集环节的配置阶段中,使用niHSDIO属性节点,启用NI 655x的硬件比较部分,如图11所示。

图11:使用属性节点方便地启用硬件比较

2、在打开硬件比较之后,波形中的六个逻辑状态开始控制NI 655x操作,而免去使用任何解释函数和分析函数。请参阅表1获得关于六个逻辑状态的更多信息。

3、对于需要更为复杂的出错分析的应用,获取函数可以采集出错数据和错误附近的采样点。对于错误的每个采样,您都可以得到以下信息:

- 包含错误的采样点

- 错误采样点中出错的比特

- 被测设备的预期响应

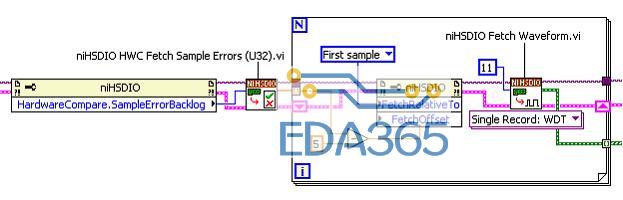

结合硬件比较中的采样错误缓存属性的属性节点,您可以直接从NI 655x FPGA获得总错误数。图12显示了硬件比较实例,采样错误缓存属性用于获取错误以及在错误发生前后的五个采样的响应数据。通过获取这些信息,您可以完成更为详细的错误分析。

图12:使用采样错误缓存获取错误附近的数据

所有数据比较都是以采样为单位在硬件中完成的,这大大减少了在软件中分析数据所花费的时间。使用硬件比较方法,NI 655x可以方便地编程实现高性能功能测试和其他激励响应的应用。

需要这个硬件比较的完整实例,请参考在线NI开发者园地(ni.com/zone)中的“高速数字实时硬件比较”实例。

特征提取

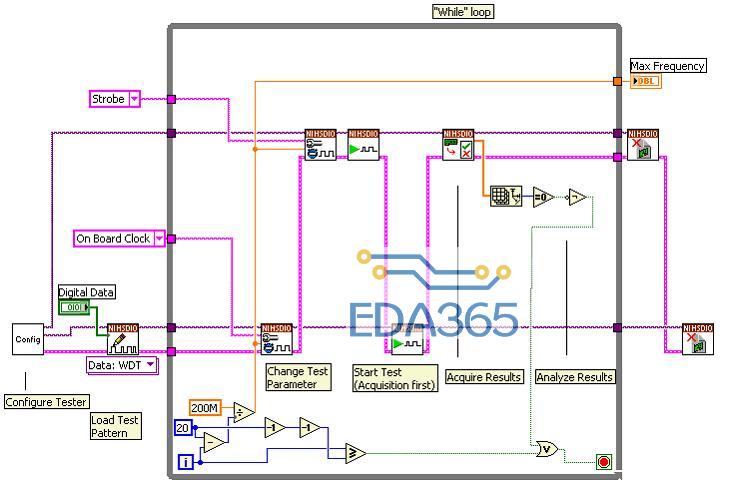

可以通过将之前所讨论的功能测试实例进行扩展,来完成被测设备的特征提取。举例而言,要得到被测设备的最大时钟速率,应用程序必须修改为从较低的频率开始,对一定范围的采样时钟速率进行扫描。特征提取测试使用之前功能测试所讨论的方法,返回通过/不通过的结果;但是,如果测试通过,就会提高采样时钟速率,并重新运行测试。这些步骤被不断重复直至被测设备无法通过测试。通过测试的最高频率就被解释为被测设备的最大工作频率。

为实现这种类型的特征提取,需要为程序增加一个循环,以便调节所需的测试参数,实现重复测试。NI-HSDIO并不需要在每次循环中都重新配置数字测试仪的所有设置,因此测试之间的重新配置时间可以尽量缩短。图13给出这个代码修改的实例。

图13:增加循环修改参数,完成特征提取

5. 扩展性

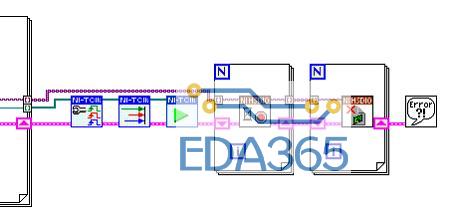

由于数字电子设备变得越来越高级,其组件可能包含只有几个管脚的串行设备,也可能包含具有数百个管脚的复杂集成电路。为了测试这些设备,数字测试系统必须扩展其通道数。使用NI-TClk(触发时钟)同步技术,多个NI 655x模块可以方便地在同一个系统中以亚纳秒级别进行同步,测试高通道数设备。举例而言,如果系统需要40个通道,下列程序解释了对多个设备进行同步所需的附加函数。

图14:使用For循环和仪器名称数组有效配置多个设备

每个模块仍然需要使用自己的一套函数进行配置和控制;但是,添加一个简单的For循环可以大大减少所需的编程任务。图14给出了使用For循环和仪器名称数组将发生程序扩展为多模块的实例。在内循环中完成所有设备的配置之后,如图15所示,只需要三个用于配置NI-TClk同步的附加VI。

图15:三个NI-TClk函数实现亚纳秒级别的同步

您还可以使用NI-TClk编写程序,使多个模块对同步的外部触发信号进行响应。要获取关于NI-TClk技术的更多信息,请访问ni.com/info并输入信息代码rdtctf,参考《用于模块化仪器定时与同步的NI T时钟技术》技术白皮书。

在使用NI-TClk同步多个模块完成硬件比较之后,如果在一个NI 655x设备上检测到错误,那么只有那个设备存储关于错误的信息。系统中的其他NI 655x设备就好像采样通过那样继续工作。由于每个设备只是记录其自身的错误,您无需担心同一个错误被计算多次;但是,您需要对所有模块的信息进行后期处理,以便在需要采样器错误率的时候建立完整的列表。

6. 结论

在增加每周期双向控制和实时硬件比较之后,相对任何其他基于PC的设备而言,NI 655x数字波形发生器/分析仪提供了更为丰富的数字测试应用解决方案。全新的解决方案涵盖了存储器芯片的功能测试、快速特征提取应用以及BERT(比特错误率测试)。PXI平台的可扩展性和软件的灵活性进一步改进了数字测试仪器的灵活性和功能。

APP下载

APP下载 登录

登录

热门文章

热门文章